硅栅CMOS倒阱工艺研究.docx

快乐****蜜蜂

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

硅栅CMOS倒阱工艺研究.docx

硅栅CMOS倒阱工艺研究硅栅CMOS倒阱工艺研究摘要:CMOS(ComplementaryMetal-Oxide-Semiconductor)技术是目前集成电路制造中最主流的工艺之一。而采用硅栅CMOS倒阱工艺在集成电路制造中具有一定的优势。本论文主要对硅栅CMOS倒阱工艺进行研究,探讨其原理、制备方法以及应用。通过实验和理论分析,得出了一些结论,并对未来的研究方向提出了建议。一、引言硅栅CMOS倒阱工艺是一种常见的深亚微米工艺,它主要通过在CMOS器件的栅极和通道区域之间形成剖面状的倒阱电荷,从而实现电

0.35μm CMOS多晶硅栅刻蚀工艺研究.docx

0.35μmCMOS多晶硅栅刻蚀工艺研究摘要:本论文研究了0.35μmCMOS多晶硅栅刻蚀工艺,通过对硅栅刻蚀过程中的影响因素进行深入分析,优化了刻蚀工艺参数,提高了刻蚀质量。在实验中,采用了多种测试方法对刻蚀结果进行了评估,并对刻蚀机理进行了探讨。研究结果表明,通过优化刻蚀工艺条件,可以得到满足0.35μmCMOS多晶硅栅刻蚀要求的高质量刻蚀结果。关键词:CMOS;多晶硅;栅刻蚀;工艺参数;刻蚀质量引言栅刻蚀是CMOS工艺中的一个重要环节。在CMOS芯片制造过程中,栅刻蚀决定了晶体管栅处是否有残留物,在

3微米硅栅高速CMOS逻辑电路工艺研究.docx

3微米硅栅高速CMOS逻辑电路工艺研究随着信息技术的发展,微电子器件尺寸越来越小,研究微米级别的高速CMOS逻辑电路工艺成为科研热点之一。本文主要介绍了3微米硅栅高速CMOS逻辑电路的工艺研究。1.3微米硅栅高速CMOS逻辑电路工艺简介3微米硅栅高速CMOS逻辑电路工艺是指采用CMOS工艺制备某一电路时,其工艺的线宽为3微米,硅栅尺寸为3微米。该工艺具有制造成本低、电路设计简单、功耗低等优点,并被广泛应用于数字电路、模拟电路、光电子学等领域。2.工艺流程3微米硅栅高速CMOS逻辑电路工艺的主要步骤包括:(

硅栅P阱CMOS反相器版图设计举例刻NMOS管S.ppt

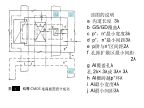

该图的说明a沟道长度3λbGS/GD覆盖λcp+,n+最小宽度3λdp+,n+最小间距3λep阱与n+区间距2λf孔距扩散区最小间距2λgAl覆盖孔λ孔2λ×3λ或3λ×3λhAl栅跨越p+环λiAl最小宽度4λjAl最小间距3λ2)铝栅、硅栅MOS器件的版图Source/Drain:Photomask(darkfield)Gate:Photomask(darkfield)Contacts:Photomask(darkfield)MetalInterconnects:Photomask(lightfiel

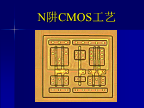

N阱CMOS工艺流程.ppt

N阱CMOS工艺①初始材料②外延生长③N阱扩散③N阱注入曝光氧化层的刻蚀N阱注入形成N阱④场区LOCOS(局部氧化)氮化硅的刻蚀沟道终止注入场氧的生长去除氮化硅⑤阈值调整采用一步调节方法重新生长二氧化硅(栅氧)⑥多晶硅淀积和光刻刻蚀多晶硅⑦源/漏注入P+离子注入N+离子注入⑧接触、金属化及保护层生长磷硅玻璃PSG光刻接触孔刻铝刻铝光刻8刻压焊孔掩膜版NMOSTransistorsPMOS晶体管衬底PNP管多晶电阻NSD和PSD电阻电容