晶体管制造工艺技术前瞻.docx

快乐****蜜蜂

亲,该文档总共13页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

晶体管制造工艺技术前瞻.docx

最新晶体管制造工艺技术前瞻制程的历史与演进CPU制程技术发展到今天,其尺寸已经从1971年Intel发布的4004CPU时的10μm进化到了今天的32nm级别,Intel公司最新推出的新款处理器—代号Westmere的32nm制程处理器(见图1)就是目前顶尖制程工艺的代表。台积电也计划于年内推出其28nm制程工艺,另外一家主要的芯片制造厂商GlobalFoundries公司则计划于年内推出基于SOI的32nm制程工艺和基于体硅的28nm制程工艺。图1:45nm制程和32nm制程不过,从早期的Intel48

最新晶体管制造工艺技术前瞻.docx

最新晶体管制造工艺技术前瞻制程的历史与演进CPU制程技术发展到今天,其尺寸已经从1971年Intel发布的4004CPU时的10μm进化到了今天的32nm级别,Intel公司最新推出的新款处理器—代号Westmere的32nm制程处理器(见图1)就是目前顶尖制程工艺的代表。台积电也计划于年内推出其28nm制程工艺,另外一家主要的芯片制造厂商GlobalFoundries公司则计划于年内推出基于SOI的32nm制程工艺和基于体硅的28nm制程工艺。图1:45nm制程和32nm制程不过,从早期的Intel48

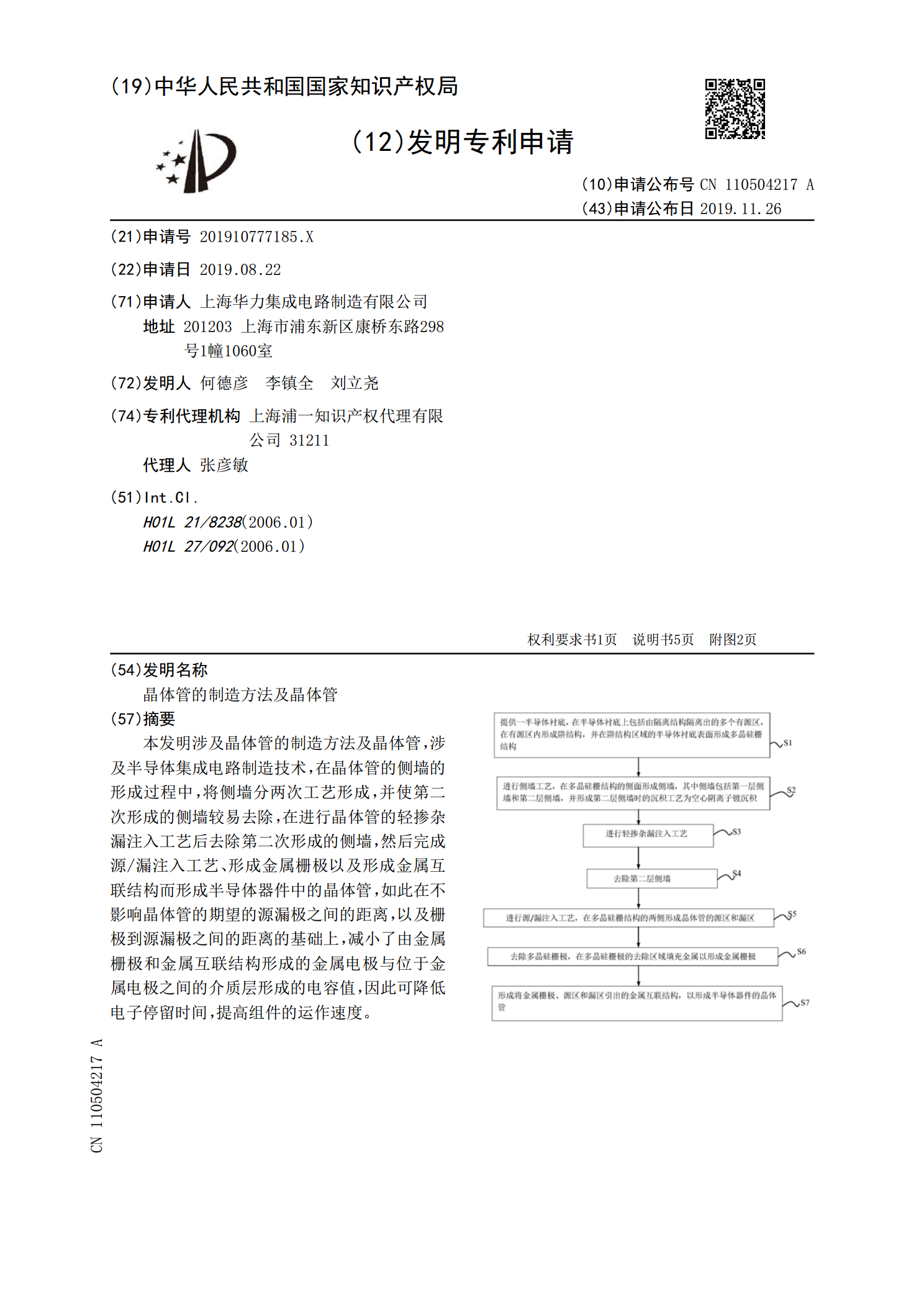

晶体管的制造方法及晶体管.pdf

本发明涉及晶体管的制造方法及晶体管,涉及半导体集成电路制造技术,在晶体管的侧墙的形成过程中,将侧墙分两次工艺形成,并使第二次形成的侧墙较易去除,在进行晶体管的轻掺杂漏注入工艺后去除第二次形成的侧墙,然后完成源/漏注入工艺、形成金属栅极以及形成金属互联结构而形成半导体器件中的晶体管,如此在不影响晶体管的期望的源漏极之间的距离,以及栅极到源漏极之间的距离的基础上,减小了由金属栅极和金属互联结构形成的金属电极与位于金属电极之间的介质层形成的电容值,因此可降低电子停留时间,提高组件的运作速度。

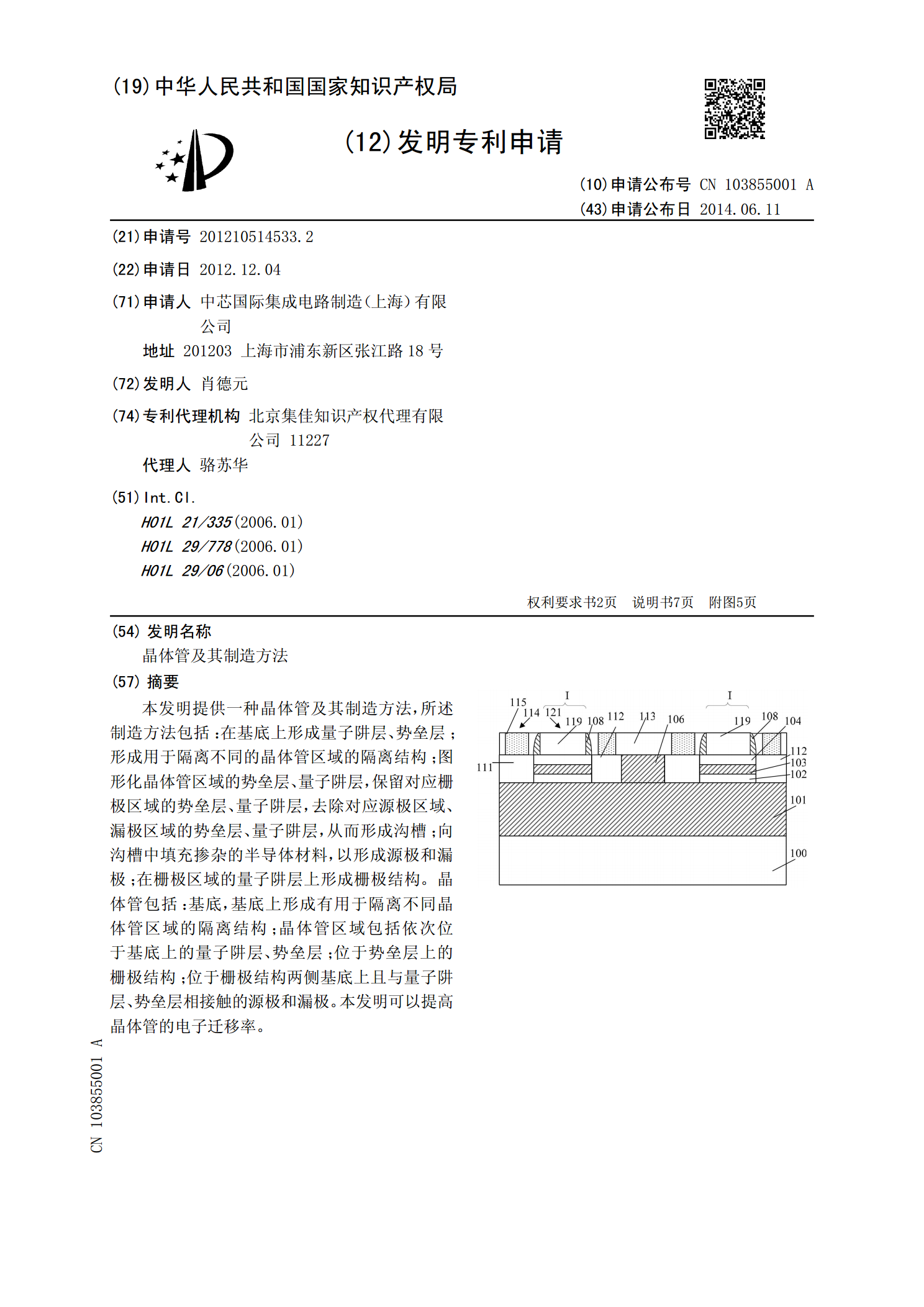

晶体管及其制造方法.pdf

本发明提供一种晶体管及其制造方法,所述制造方法包括:在基底上形成量子阱层、势垒层;形成用于隔离不同的晶体管区域的隔离结构;图形化晶体管区域的势垒层、量子阱层,保留对应栅极区域的势垒层、量子阱层,去除对应源极区域、漏极区域的势垒层、量子阱层,从而形成沟槽;向沟槽中填充掺杂的半导体材料,以形成源极和漏极;在栅极区域的量子阱层上形成栅极结构。晶体管包括:基底,基底上形成有用于隔离不同晶体管区域的隔离结构;晶体管区域包括依次位于基底上的量子阱层、势垒层;位于势垒层上的栅极结构;位于栅极结构两侧基底上且与量子阱层、

组装晶体管收音机工艺技术.pptx

任务11组装晶体管收音机11.2任务资讯11.2.1晶体管收音机的工作原理一、识读晶体管收音机的方框图超外差式晶体管AM收音机一般由高频和低频两大电路组成,其中,高频电路主要包括变频级(高放、混频、本振)、中放级(中放Ⅰ、中放Ⅱ、自动增益控制)、检波级3大单元电路组成;低频电路主要由前置放大与功放2大电路组成。各方框图的主要作用如下。高放:把天线接收下来的广播(高频)信号进行放大。本振:产生一个本机振荡,该振荡频率总是跟踪高放级,总比高放级的信号频率高465KHZ,把这个频率称为“中频”,中频送至混频级。