晶体管的制造方法及晶体管.pdf

书生****ma

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

晶体管的制造方法及晶体管.pdf

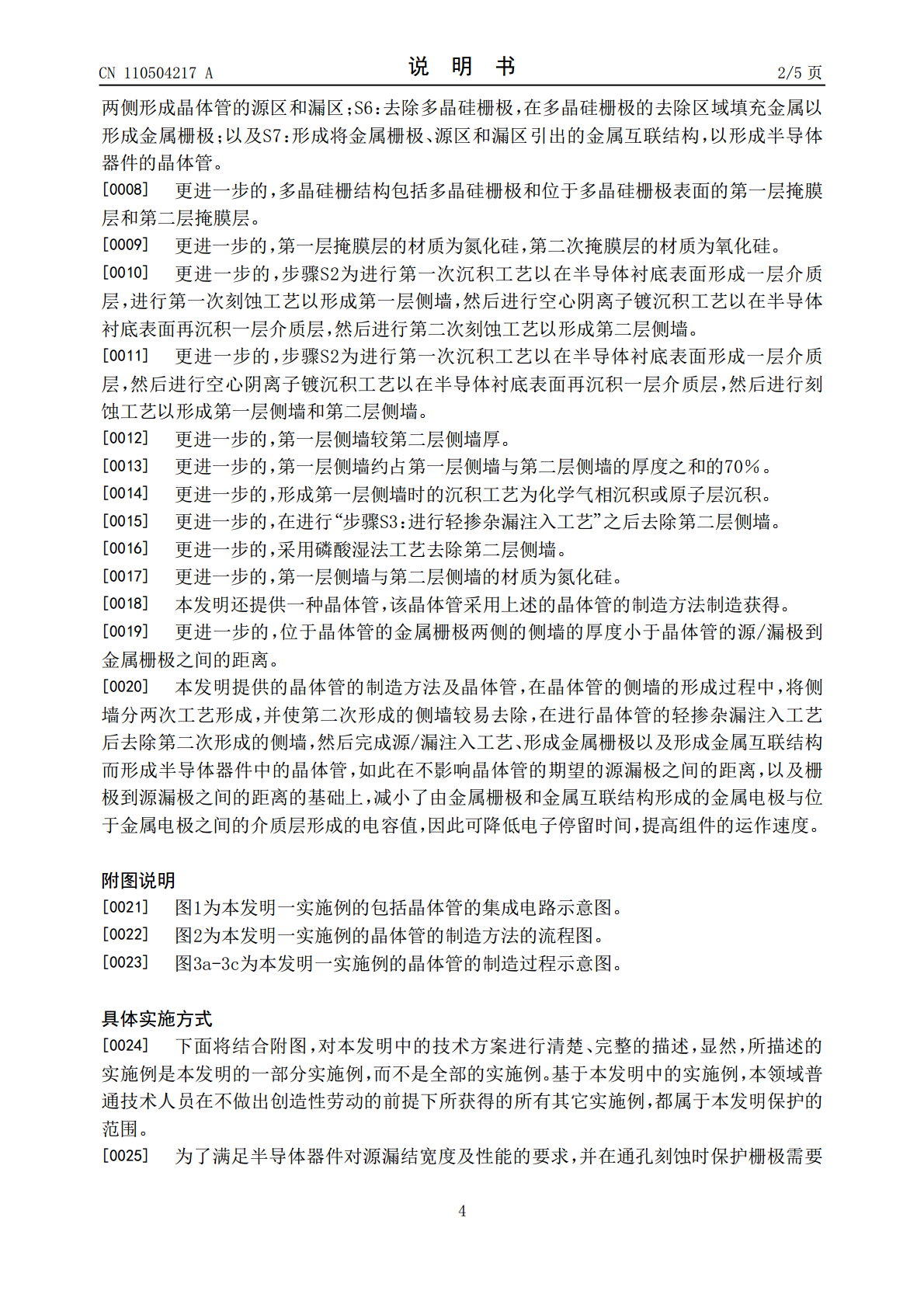

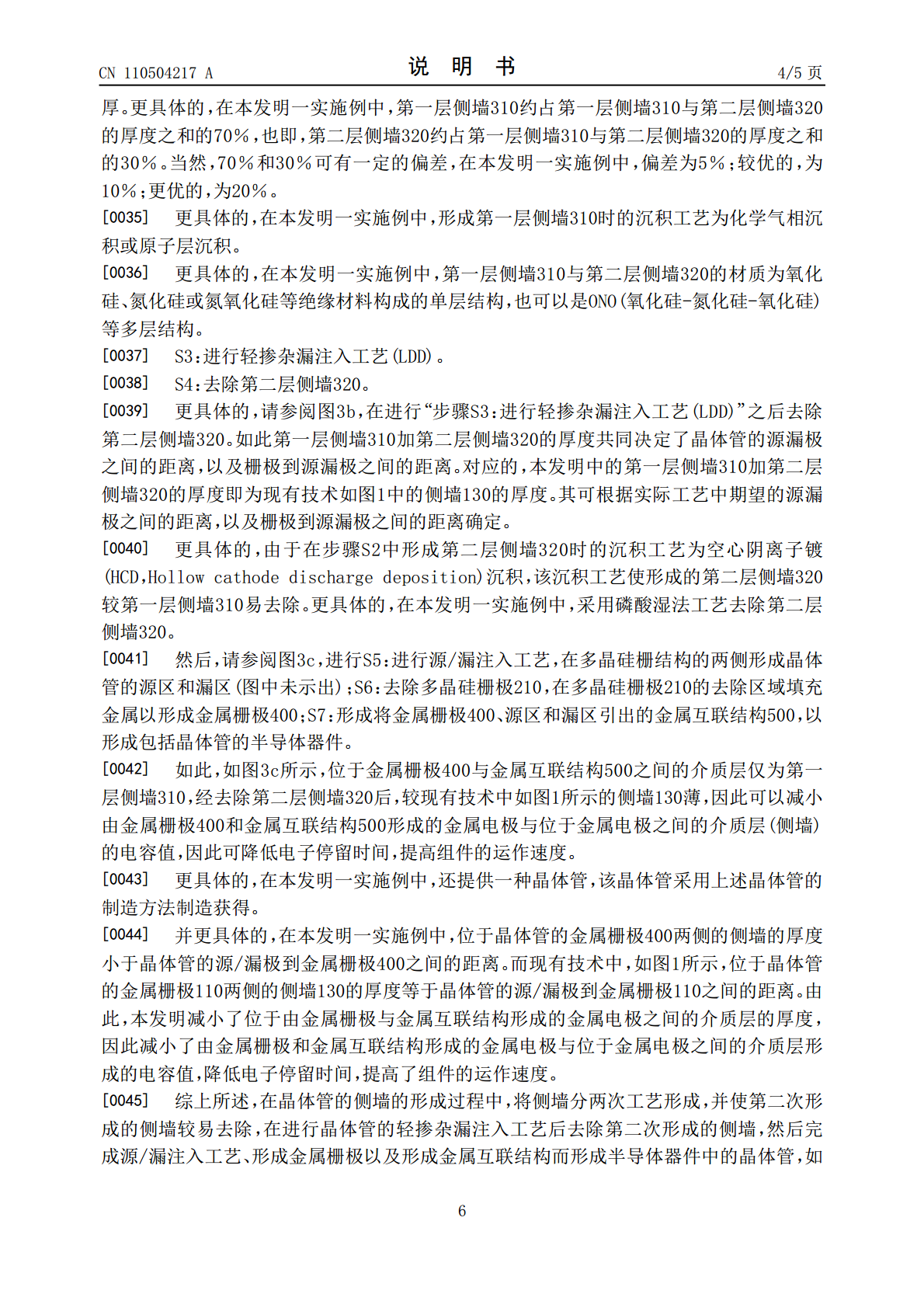

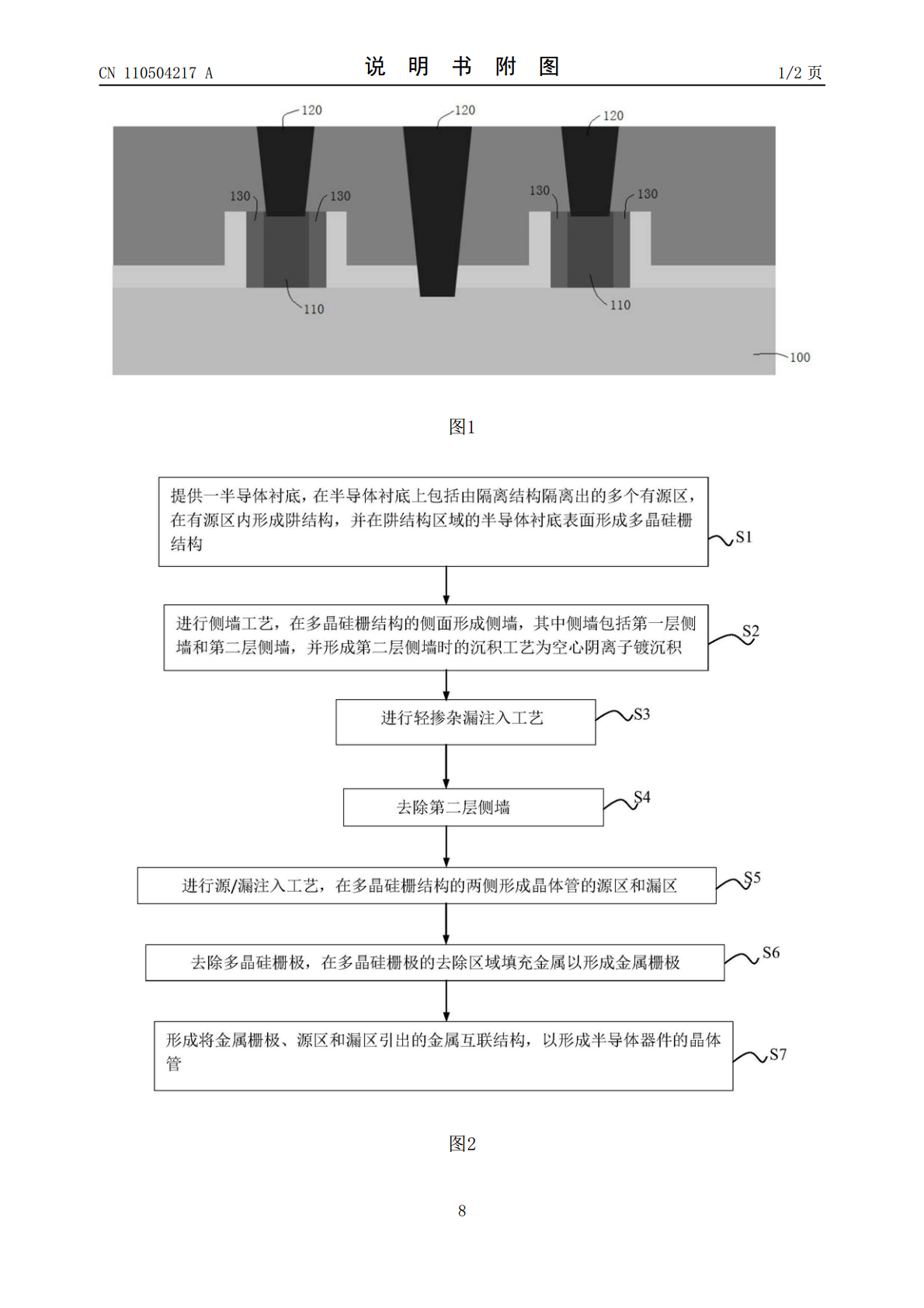

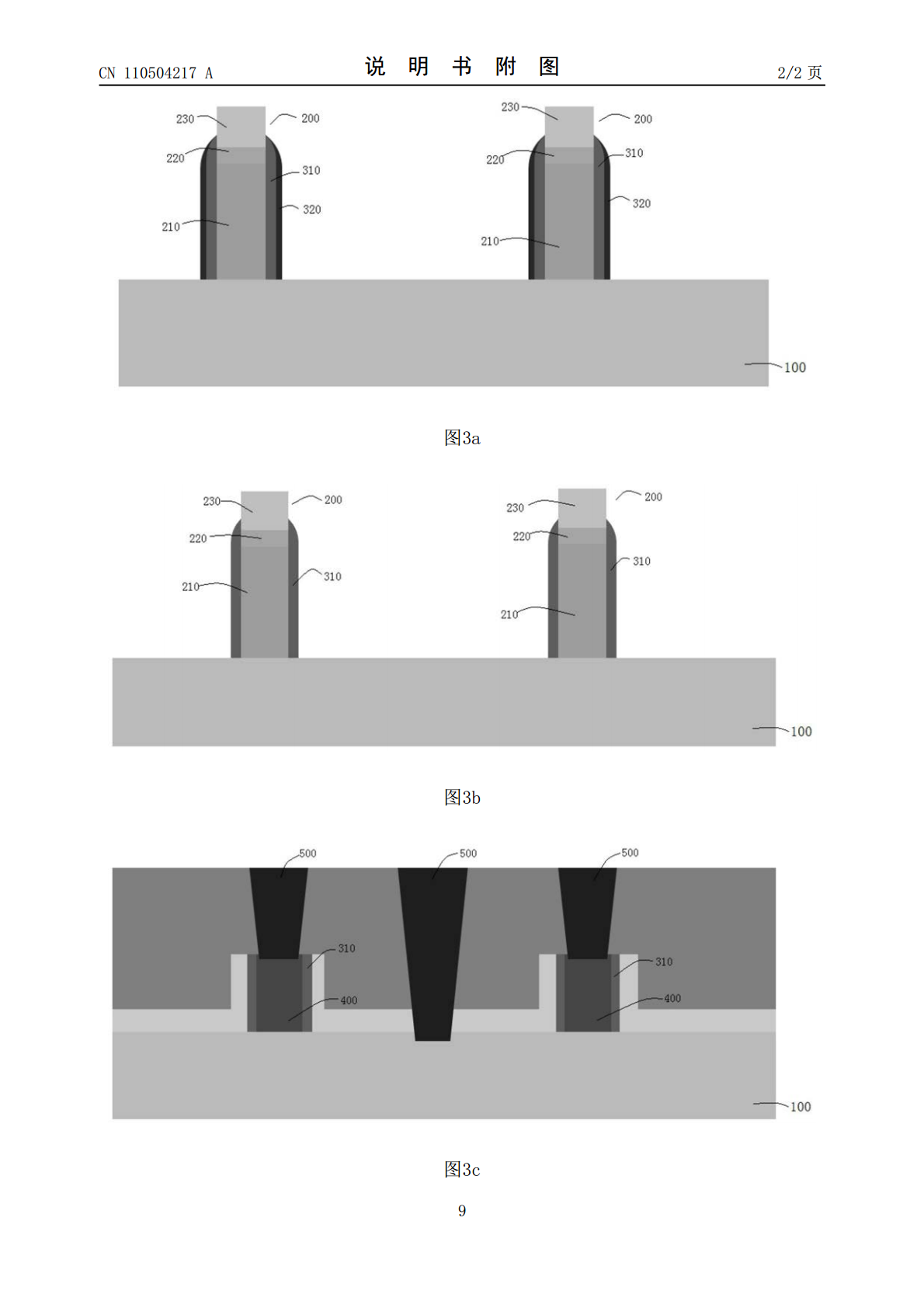

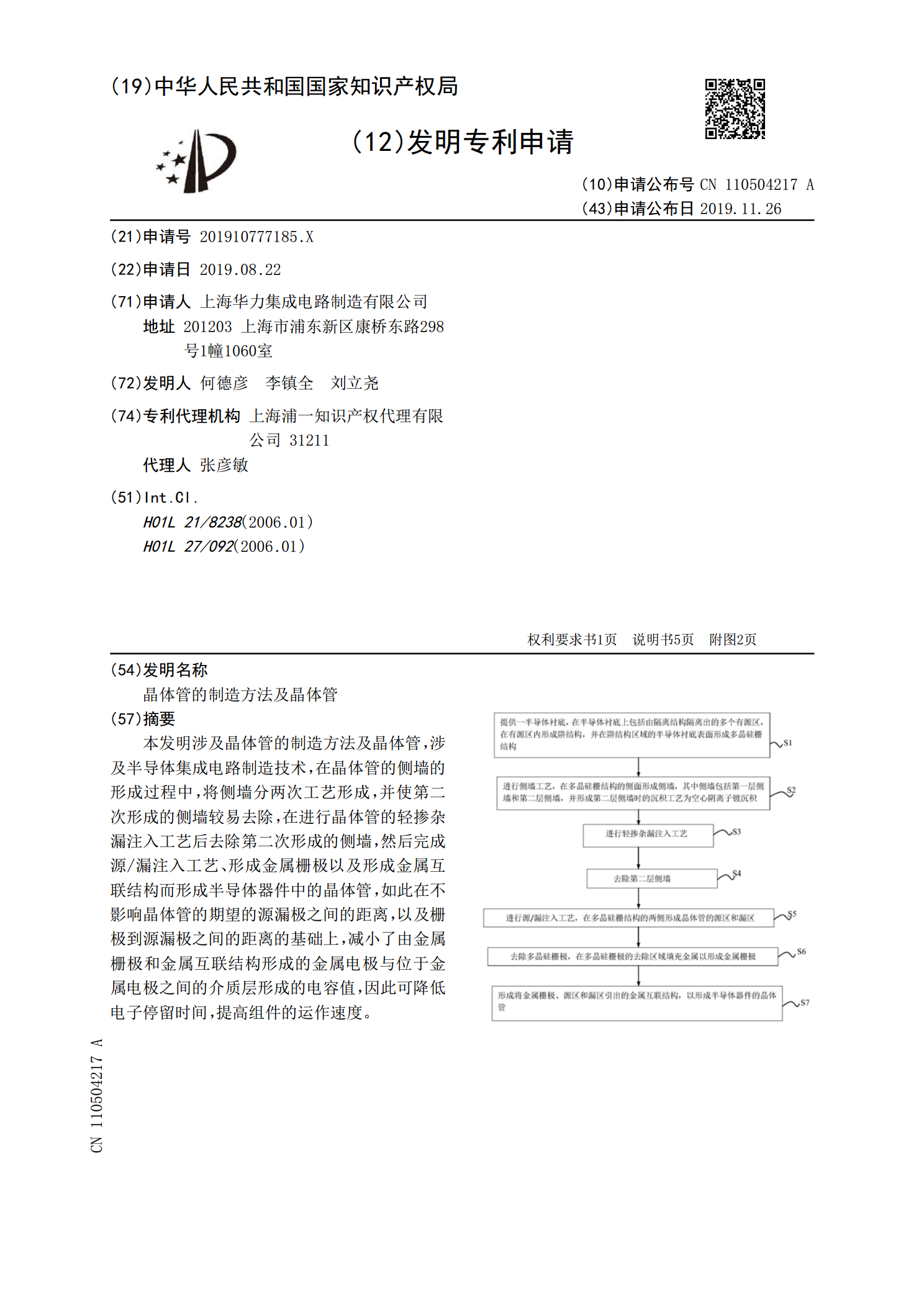

本发明涉及晶体管的制造方法及晶体管,涉及半导体集成电路制造技术,在晶体管的侧墙的形成过程中,将侧墙分两次工艺形成,并使第二次形成的侧墙较易去除,在进行晶体管的轻掺杂漏注入工艺后去除第二次形成的侧墙,然后完成源/漏注入工艺、形成金属栅极以及形成金属互联结构而形成半导体器件中的晶体管,如此在不影响晶体管的期望的源漏极之间的距离,以及栅极到源漏极之间的距离的基础上,减小了由金属栅极和金属互联结构形成的金属电极与位于金属电极之间的介质层形成的电容值,因此可降低电子停留时间,提高组件的运作速度。

晶体管及其制造方法.pdf

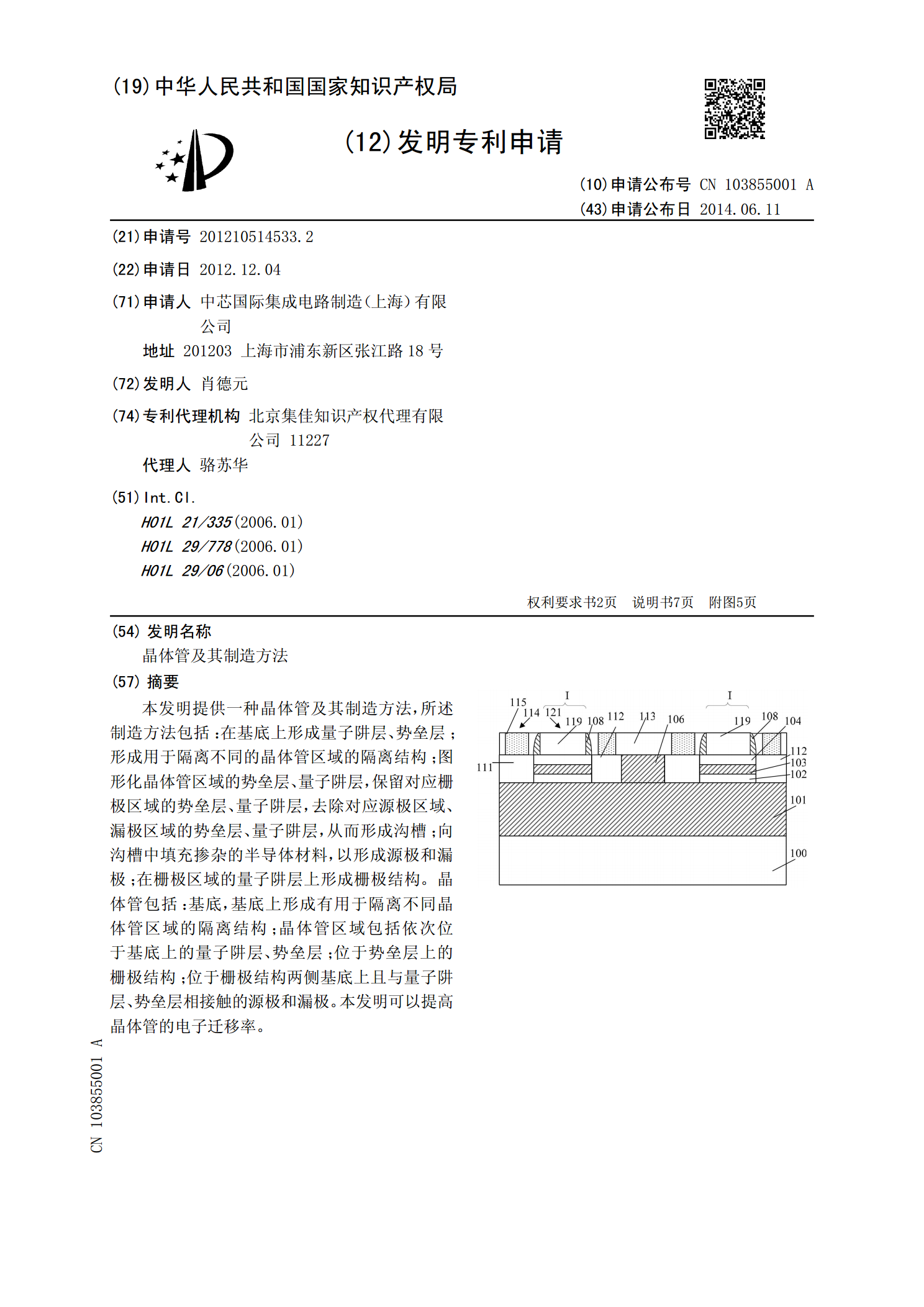

本发明提供一种晶体管及其制造方法,所述制造方法包括:在基底上形成量子阱层、势垒层;形成用于隔离不同的晶体管区域的隔离结构;图形化晶体管区域的势垒层、量子阱层,保留对应栅极区域的势垒层、量子阱层,去除对应源极区域、漏极区域的势垒层、量子阱层,从而形成沟槽;向沟槽中填充掺杂的半导体材料,以形成源极和漏极;在栅极区域的量子阱层上形成栅极结构。晶体管包括:基底,基底上形成有用于隔离不同晶体管区域的隔离结构;晶体管区域包括依次位于基底上的量子阱层、势垒层;位于势垒层上的栅极结构;位于栅极结构两侧基底上且与量子阱层、

薄膜晶体管制造方法.pdf

薄膜晶体管制造方法,包括:在基板(10)的表面上依次形成栅极(11)、覆盖栅极(11)及基板(10)表面形成栅极绝缘层(12)、位于所述栅极(11)上方形成有源层(13)、正投影于有源层(13)中部的蚀刻阻挡层(14)及在有源层(13)、蚀刻阻挡层(14)及栅极绝缘层(12)上形成包括覆盖所述蚀刻阻挡层(14)的第一区域(151)以及连接所述第一区域(151)相对两侧的第二区域(152),所述每一第二区域(152)与所述有源层(13)及蚀刻阻挡层(14)连接的金属层(15);在金属层(15)上形成光阻层(

薄膜晶体管、薄膜晶体管阵列基板及其制造方法.pdf

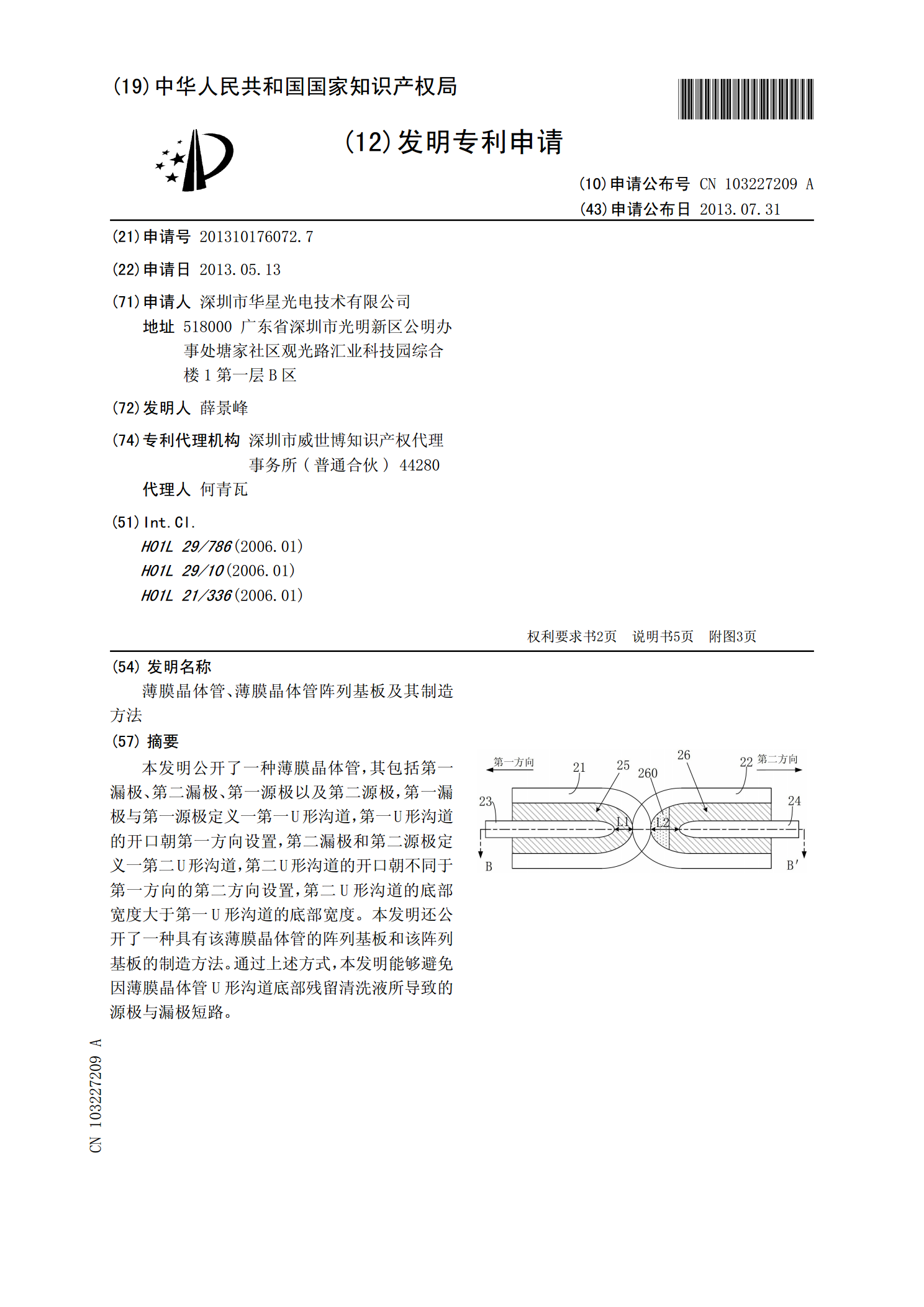

本发明公开了一种薄膜晶体管,其包括第一漏极、第二漏极、第一源极以及第二源极,第一漏极与第一源极定义一第一U形沟道,第一U形沟道的开口朝第一方向设置,第二漏极和第二源极定义一第二U形沟道,第二U形沟道的开口朝不同于第一方向的第二方向设置,第二U形沟道的底部宽度大于第一U形沟道的底部宽度。本发明还公开了一种具有该薄膜晶体管的阵列基板和该阵列基板的制造方法。通过上述方式,本发明能够避免因薄膜晶体管U形沟道底部残留清洗液所导致的源极与漏极短路。

双极性晶体管及其制造方法.pdf

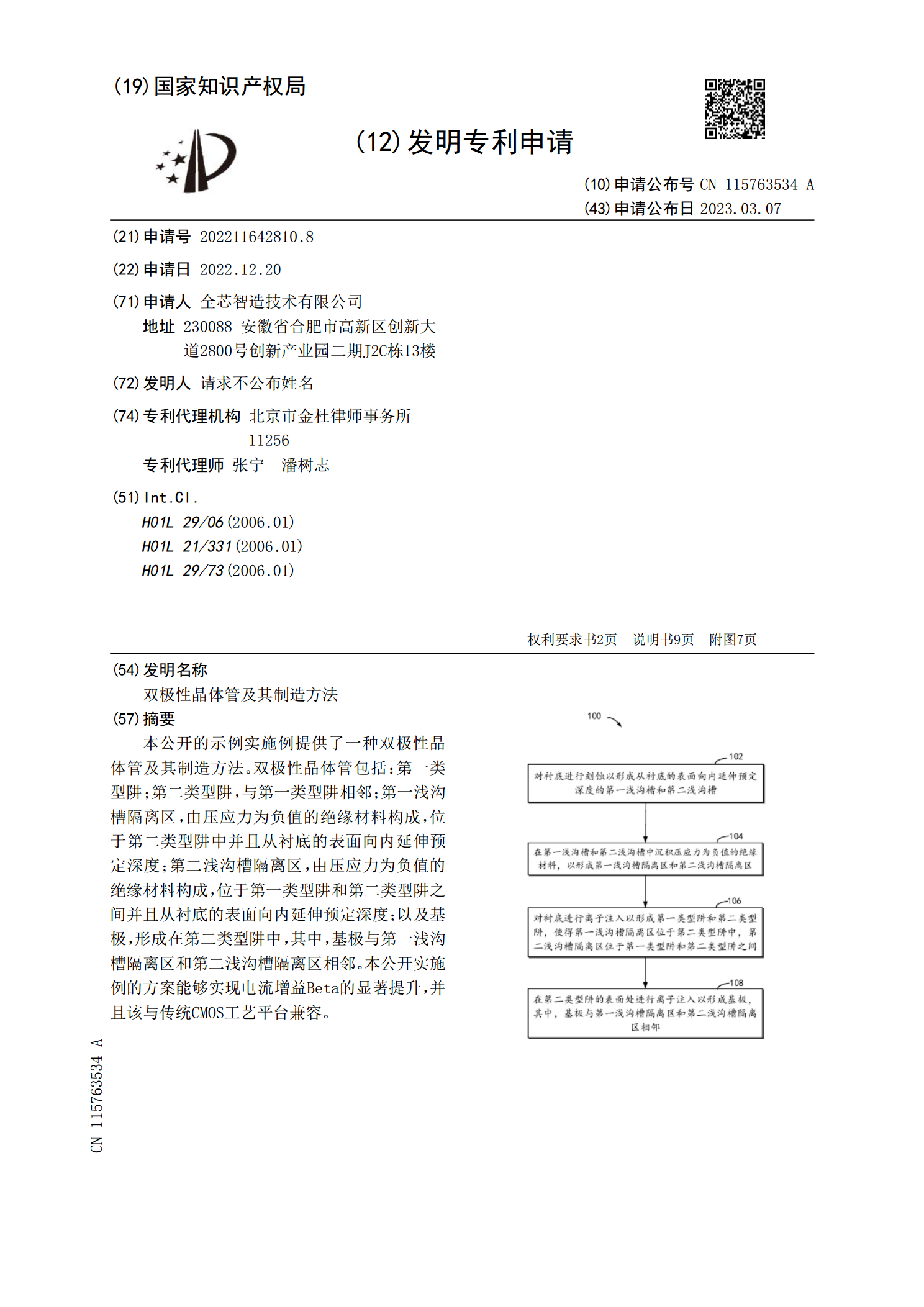

本公开的示例实施例提供了一种双极性晶体管及其制造方法。双极性晶体管包括:第一类型阱;第二类型阱,与第一类型阱相邻;第一浅沟槽隔离区,由压应力为负值的绝缘材料构成,位于第二类型阱中并且从衬底的表面向内延伸预定深度;第二浅沟槽隔离区,由压应力为负值的绝缘材料构成,位于第一类型阱和第二类型阱之间并且从衬底的表面向内延伸预定深度;以及基极,形成在第二类型阱中,其中,基极与第一浅沟槽隔离区和第二浅沟槽隔离区相邻。本公开实施例的方案能够实现电流增益Beta的显著提升,并且该与传统CMOS工艺平台兼容。