《MOS存储器》PPT课件.ppt

lj****88

亲,该文档总共26页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

《MOS存储器》PPT课件.ppt

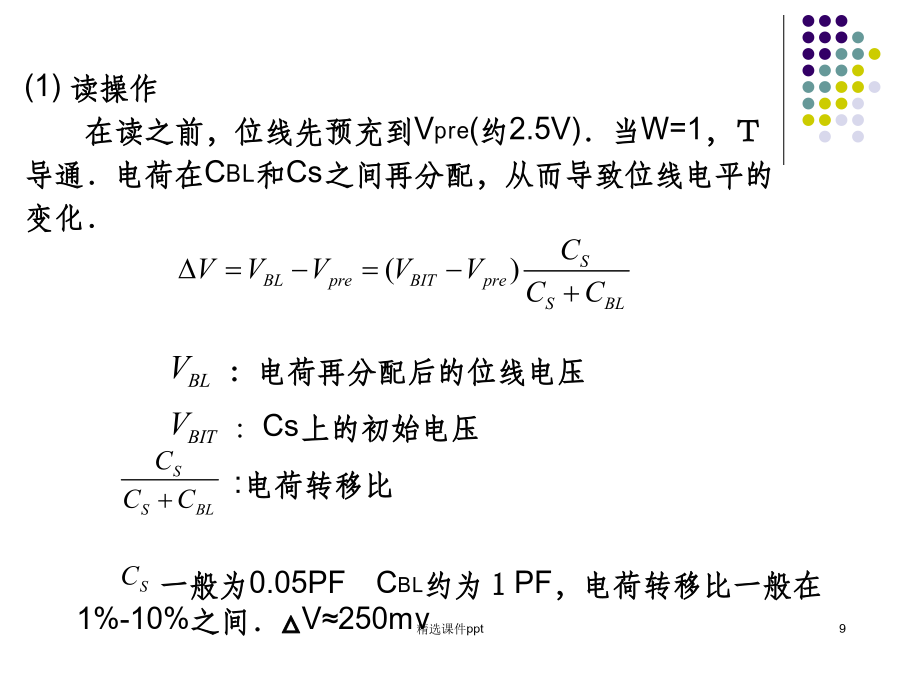

MOS存储器2.不挥发性读写存储器NVRWM(non-volatileread-writememory)习惯称为可擦除型ROM.(1)可擦除型EPROM(erasablePROM).紫外光擦除,一次性全部擦除.(2)电可擦除EEPROM(electricallyerasablePROM).浮栅隧道结构,可逐字擦写,速度快,不需从设备上取出.价格较贵.(3)闪烁型复栅结构,比EEPROM简单,通常用作可变信息的存储.3.随机存取存储器RAM(randomaccessmemory)挥发性的.(1)静态SRAM

MOS存储器.ppt

MOS存储器2.不挥发性读写存储器NVRWM(non-volatileread-writememory)习惯称为可擦除型ROM.(1)可擦除型EPROM(erasablePROM).紫外光擦除,一次性全部擦除.(2)电可擦除EEPROM(electricallyerasablePROM).浮栅隧道结构,可逐字擦写,速度快,不需从设备上取出.价格较贵.(3)闪烁型复栅结构,比EEPROM简单,通常用作可变信息的存储.3.随机存取存储器RAM(randomaccessmemory)挥发性的.(1)静态SRAM

MOS管原理ppt课件.ppt

MOS管的那些事儿我们在笔记本主板维修中见到的MOS管几乎都是绝缘栅增强型,这里也就只说说它的那些事儿吧。而且,我们不谈原理,只谈应用。1三个极怎么判定电路符号开始之前,一个小测试:再来一个,试试看:电路符号电路符号电路符号电路符号电路符号电路符号电路符号电路符号电路符号电路符号电路符号电路符号电路符号电路符号电路符号S极S极电路符号方法2:加入MOS管电路符号笔记本电脑中用到的隔离MOS管只有两个。下面我们来分步讨论一下它的原理,为了方便,隔离MOS管都用二级管代替表示。电路符号电路符号电路符号电路符号

MOS管的分类ppt课件.ppt

MOS的种类及应用MOS管的种类MOS的分类方法MOS的分类方法结型管和绝缘栅型管MOS的分类方法功率分类功率分类MOS的导通特性MOS的作用MOS的应用MOS管的应用电路MOS管的应用电路MOS管的实际应用结束语

MOS管知识ppt课件.ppt

第三章场效应管及其放大电路一.场效应管的分类1.基本结构图3.1是N沟道增强型绝缘栅场效应管的结构示意图。利用栅源电压uGS的大小,来改变半导体表面感生电荷的多少,从而控制漏极电流iD的大小。分析:主要讨论uGS对iD的控制作用。(1)当uGS=0时(见图3.2a),不论所加电压uDS的极性如何,其中总有一个PN结是反向偏置的,反向电阻很高,则漏极电流iD≈0。(2)当栅源极之间加正向电压uGS(见图3.2b),(3)当栅极与源极之间加正向电压uGS≥UT时(见图3.2c),被吸到表面层中的自由电子较多,