基于FPGA的LED大屏幕控制系统设计.doc

猫巷****志敏

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

基于FPGA的LED大屏幕控制系统设计.docx

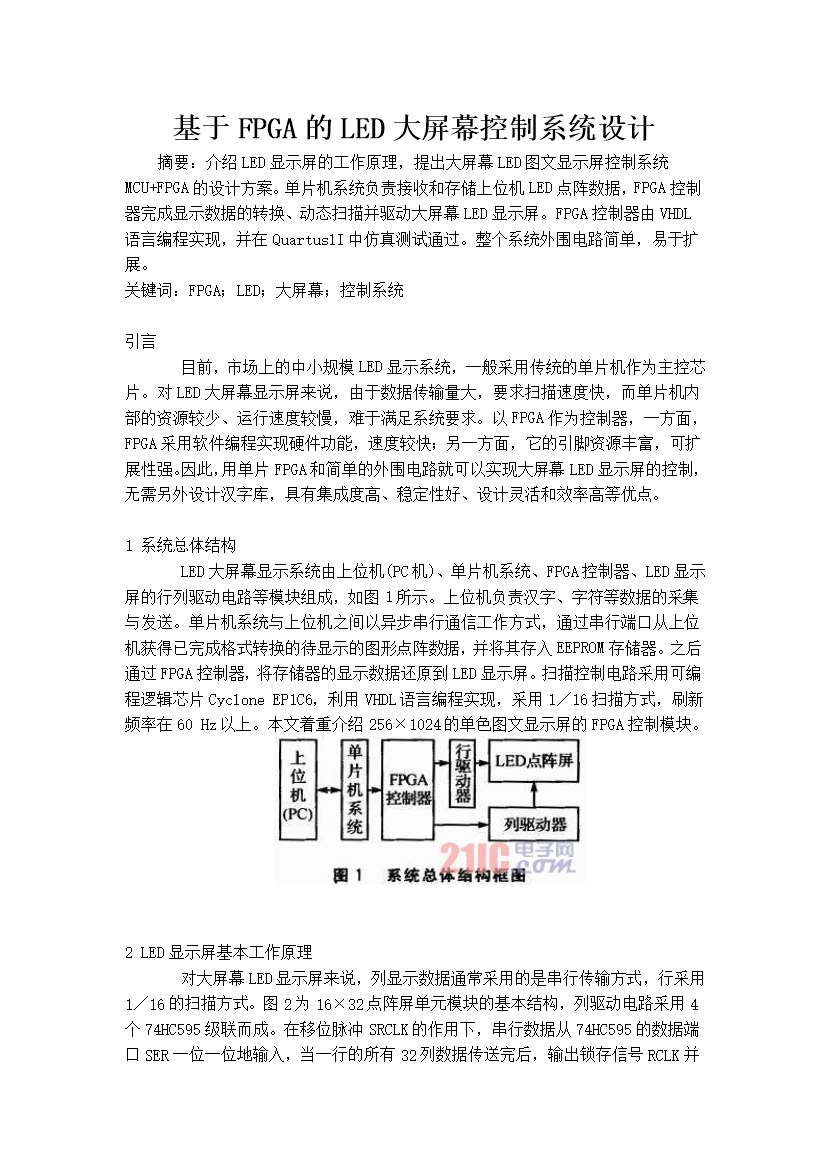

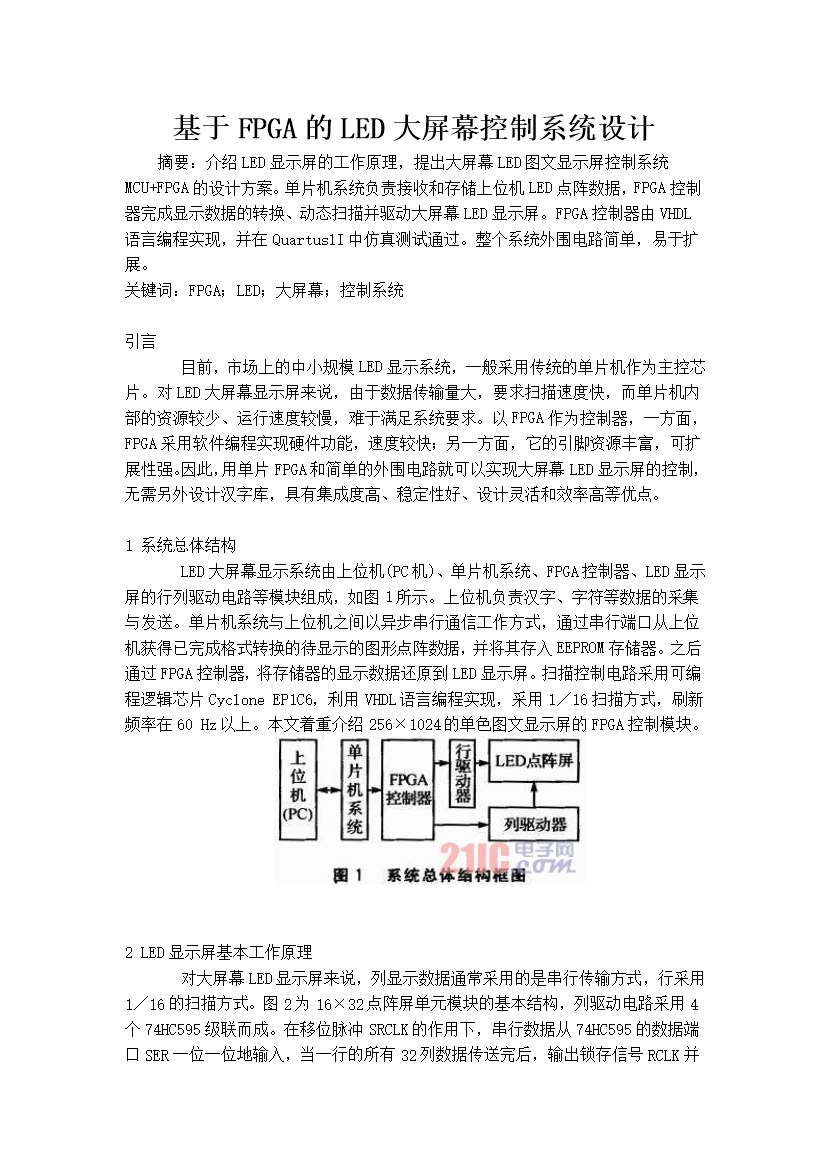

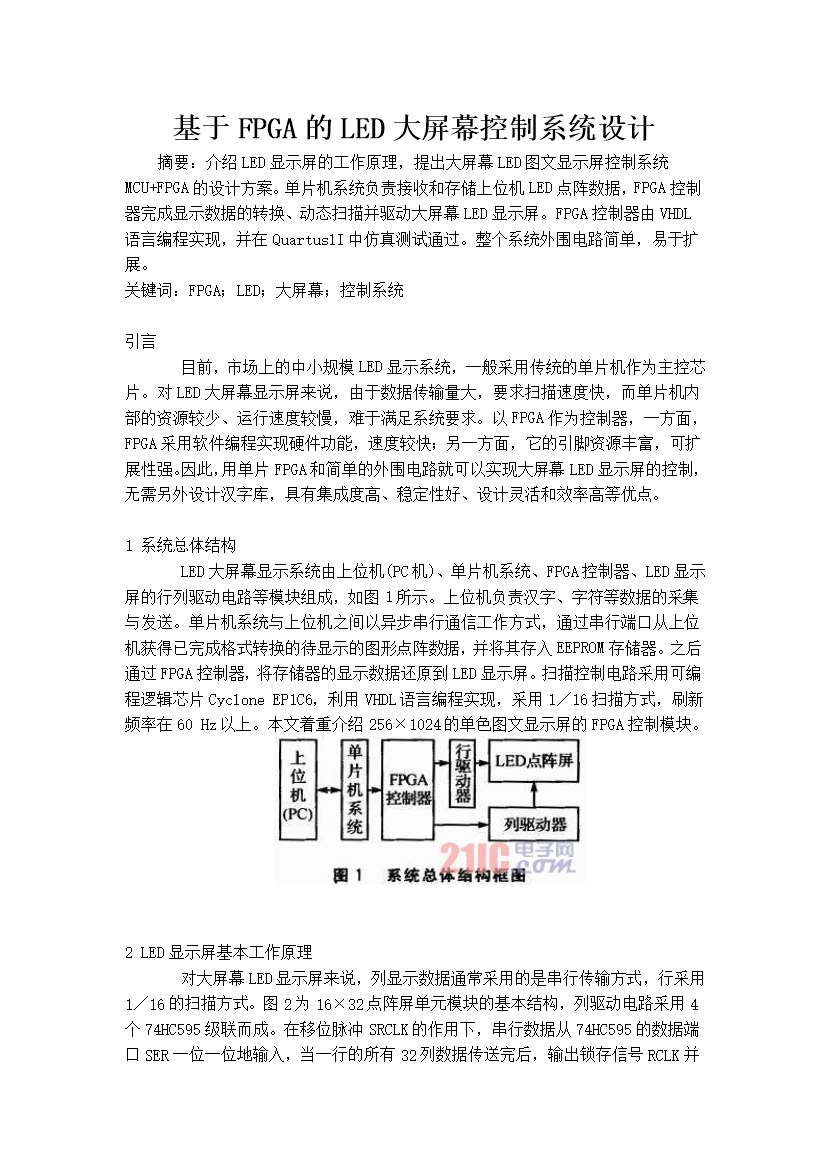

基于FPGA的LED大屏幕控制系统设计摘要:介绍LED显示屏的工作原理,提出大屏幕LED图文显示屏控制系统MCU+FPGA的设计方案。单片机系统负责接收和存储上位机LED点阵数据,FPGA控制器完成显示数据的转换、动态扫描并驱动大屏幕LED显示屏。FPGA控制器由VHDL语言编程实现,并在QuartuslI中仿真测试通过。整个系统外围电路简单,易于扩展。关键词:FPGA;LED;大屏幕;控制系统引言目前,市场上的中小规模LED显示系统,一般采用传统的单片机作为主控芯片。对LED大屏幕显示屏来说,由于数据传

基于FPGA的LED大屏幕控制系统设计.doc

基于FPGA的LED大屏幕控制系统设计摘要:介绍LED显示屏的工作原理提出大屏幕LED图文显示屏控制系统MCU+FPGA的设计方案。单片机系统负责接收和存储上位机LED点阵数据FPGA控制器完成显示数据的转换、动态扫描并驱动大屏幕LED显示屏。FPGA控制器由VHDL语言编程实现并在QuartuslI中仿真测试通过。整个系统外围电路简单易于扩展。关键词:FPGA;LED;大屏幕;控制系统引言目前市场上的中小规模LED显示系统一般采用传统的单片机作为主控芯片。对LED大屏幕显示屏来说由于数据传输量大

基于FPGA的LED大屏幕控制系统设计.doc

基于FPGA的LED大屏幕控制系统设计摘要:介绍LED显示屏的工作原理提出大屏幕LED图文显示屏控制系统MCU+FPGA的设计方案。单片机系统负责接收和存储上位机LED点阵数据FPGA控制器完成显示数据的转换、动态扫描并驱动大屏幕LED显示屏。FPGA控制器由VHDL语言编程实现并在QuartuslI中仿真测试通过。整个系统外围电路简单易于扩展。关键词:FPGA;LED;大屏幕;控制系统引言目前市场上的中小规模LED显示系统一般采用传统的单片机作为主控芯片。对LED大屏幕显示屏来说由于数据传输量大

基于FPGA的LED大屏幕控制系统设计.doc

基于FPGA的LED大屏幕控制系统设计摘要:介绍LED显示屏的工作原理提出大屏幕LED图文显示屏控制系统MCU+FPGA的设计方案。单片机系统负责接收和存储上位机LED点阵数据FPGA控制器完成显示数据的转换、动态扫描并驱动大屏幕LED显示屏。FPGA控制器由VHDL语言编程实现并在QuartuslI中仿真测试通过。整个系统外围电路简单易于扩展。关键词:FPGA;LED;大屏幕;控制系统引言目前市场上的中小规模LED显示系统一般采用传统的单片机作为主控芯片。对LED大屏幕显示屏来说由于数据传输量大

基于FPGA的大屏幕LED控制器的研究与设计.docx

基于FPGA的大屏幕LED控制器的研究与设计摘要:本文主要介绍了基于FPGA的大屏幕LED控制器的研究与设计。首先介绍了课题背景和研究意义,然后阐述了LED显示屏的基本原理和市场现状,分析了现有控制器的不足,提出了基于FPGA的LED控制器解决方案,并对其进行了详细的设计和实现。最后,进行了测试和验证,结果显示,基于FPGA的LED控制器具有高性能和可靠性,具有重要的应用价值。关键词:FPGA、大屏幕LED控制器、设计、实现、测试1、引言随着科技的不断发展,LED显示屏的应用越来越广泛,从电视背光到广告牌