基于FPGA的通用异步收发器设计.docx

快乐****蜜蜂

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

基于FPGA的通用异步收发器设计.docx

基于FPGA的通用异步收发器设计基于FPGA的通用异步收发器设计摘要:本论文主要讨论了基于FPGA的通用异步收发器的设计。异步通信是一种无需使用时钟信号同步的通信方式,可以实现高速、灵活和可靠的数据传输。本文首先介绍了异步通信的原理和优势,然后详细阐述了基于FPGA的异步收发器的设计方法和实现过程。最后给出了设计的性能评估和未来改进的展望。关键词:FPGA,异步通信,收发器,设计,性能评估一、引言随着通信技术的发展和高速数据传输的需求不断增加,异步通信作为一种不依赖于时钟信号同步的通信方式,逐渐受到了广泛

基于FPGA的通用异步收发器的设计的任务书.docx

基于FPGA的通用异步收发器的设计的任务书任务书一、任务背景在数字电路系统设计中,异步传输是逐渐被重视的一种数据传输方式,它可以在压缩设计时间基本不用增加成本的情况下提高系统性能。因此,本次设计将设计一种基于FPGA的通用异步收发器。根据不同信号的情况,我们需要设计出一种可以自适应的异步收发器,在不同的传输环境下具备较好的数据传输表现。二、任务要求1.完成异步收发器的设计和实现,需要考虑以下因素:(1)正确地处理不同数据信号的传输模式,如:数据宽度、传输速率、时序稳定性等要求。(2)能适应不同的传输环境,

基于FPGA的异步收发器模块设计.docx

基于FPGA的异步收发器模块设计异步收发器是数字电子电路中的重要组成部分,在不同的应用中广泛使用。它的主要作用是实现数据的传输和处理。基于FPGA的异步收发器模块设计是一项重要的任务,这篇论文将详细介绍这个问题。首先,介绍异步收发器的基本原理。异步收发器是一种数据传输电路,它能够在不同速度的系统之间进行数据传输。在异步收发器中,发送器和接收器之间没有时钟信号来同步数据传输。通常,发送器将数据转成一系列异步信号,由接收器进行恢复,然后将其转化回原始数据。在异步收发器中,控制信号是非常重要的。为了控制数据的传

基于PLDFPGA的通用异步收发器设计.docx

基于PLDFPGA的通用异步收发器设计随着数字电路设计的迅速发展,越来越多的应用需要高性能的通信模块。在这样的情况下,异步收发器是不可或缺的一个模块。本文将介绍一种基于PLDFPGA的通用异步收发器设计。1.异步收发器的基本原理异步收发器是指传输数据时发送端和接收端时钟不同步的一种接口。在异步系统中,数据传输使用的是数据时序而不是时钟信号同步。异步传输因其灵活性和协议可扩展性而越来越受到关注。异步收发器的工作原理,如图1所示。在发送端,输入数据通过同步复位电路复位。当外部输入信号到达时,数据被传输到寄存器

基于FPGA的容错异步串行收发器装置.pdf

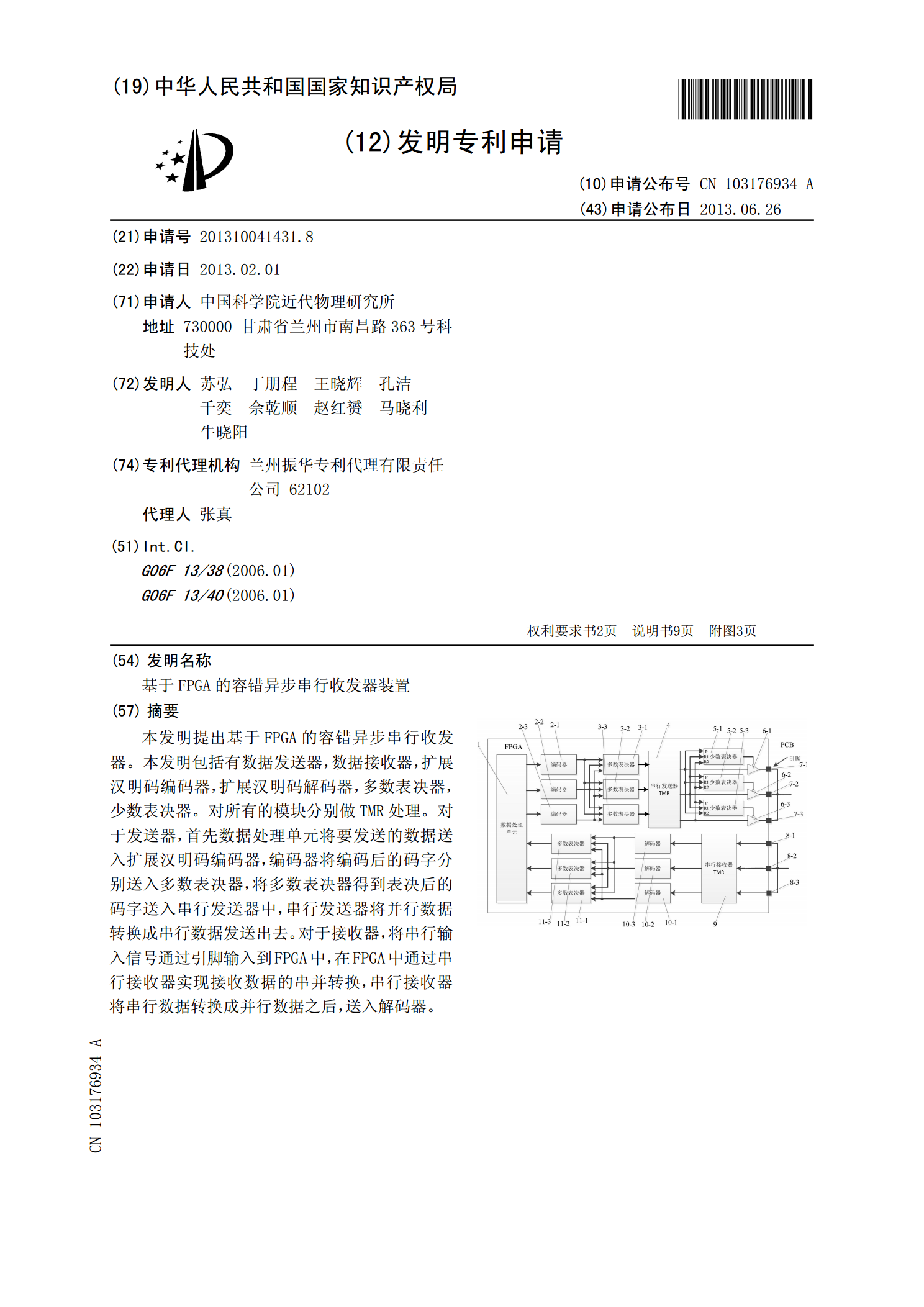

本发明提出基于FPGA的容错异步串行收发器。本发明包括有数据发送器,数据接收器,扩展汉明码编码器,扩展汉明码解码器,多数表决器,少数表决器。对所有的模块分别做TMR处理。对于发送器,首先数据处理单元将要发送的数据送入扩展汉明码编码器,编码器将编码后的码字分别送入多数表决器,将多数表决器得到表决后的码字送入串行发送器中,串行发送器将并行数据转换成串行数据发送出去。对于接收器,将串行输入信号通过引脚输入到FPGA中,在FPGA中通过串行接收器实现接收数据的串并转换,串行接收器将串行数据转换成并行数据之后,送入