基于FPGA的高速峰值检测.docx

快乐****蜜蜂

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

基于FPGA的高速峰值检测.docx

基于FPGA的高速峰值检测摘要本文针对信号处理领域中的高速峰值检测问题,提出了一种基于FPGA实现的高速峰值检测方法。该方法通过将峰值检测算法实现在FPGA上,大大提高了计算速度和稳定性,并具有较高的实时性和精度。本文详细介绍了该方法的实现流程和技术细节,并用实验结果验证了其有效性和性能优势。关键词:高速峰值检测;FPGA;实时性;精度;性能优势一、引言在信号处理领域中,峰值检测是一个重要的技术问题。例如,在音频、视频信号相关的应用领域中,峰值检测可以用于识别信号的关键特征,并提供跟踪或测量这些特征的手段

FPGA在峰值检测中的应用.docx

FPGA在峰值检测中的应用FPGA在峰值检测中的应用摘要:本文主要介绍FPGA在峰值检测中的应用,分别从峰值检测的基本原理、常用的实现方法、FPGA实现的优势等方面进行了阐述。通过本文可以看出,FPGA在峰值检测中的应用具有可编程性强、速度快、精度高、功耗低、系统集成度高等优点,因此在很多领域,尤其是对于需要高速、精度要求高的实时峰值检测应用中,FPGA都有着广泛的应用前景。1.引言峰值检测是指在一段信号中寻找最大值的过程,具有广泛的应用场景,如音频、图像处理、通信、雷达等领域。峰值检测的实现方法有多种,

基于FPGA的高速串行接口.pdf

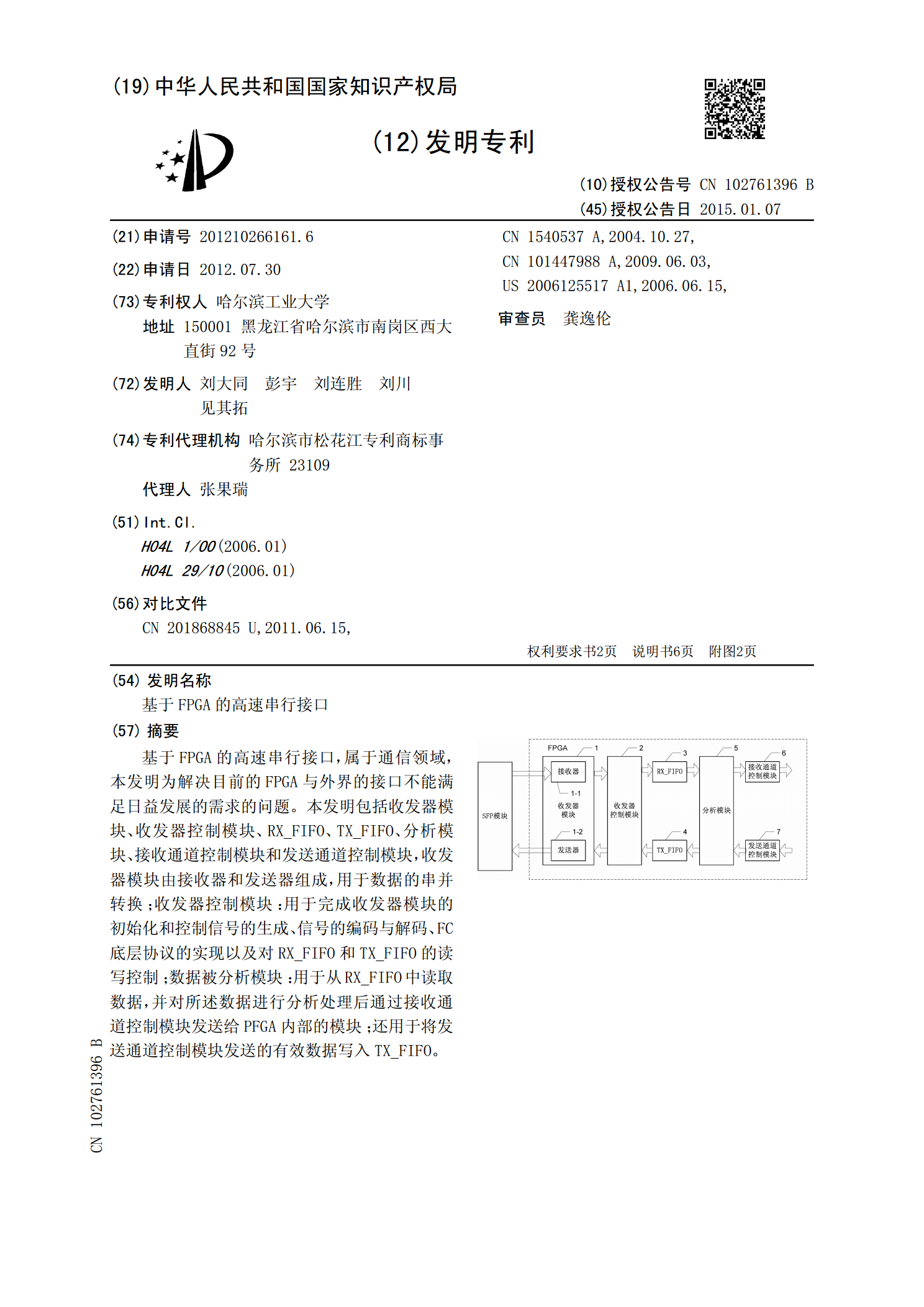

基于FPGA的高速串行接口,属于通信领域,本发明为解决目前的FPGA与外界的接口不能满足日益发展的需求的问题。本发明包括收发器模块、收发器控制模块、RX_FIFO、TX_FIFO、分析模块、接收通道控制模块和发送通道控制模块,收发器模块由接收器和发送器组成,用于数据的串并转换;收发器控制模块:用于完成收发器模块的初始化和控制信号的生成、信号的编码与解码、FC底层协议的实现以及对RX_FIFO和TX_FIFO的读写控制;数据被分析模块:用于从RX_FIFO中读取数据,并对所述数据进行分析处理后通过接收通道控

基于FPGA的高速PCB的设计.docx

基于FPGA的高速PCB的设计随着电子科技的不断进步,FPGA(现场可编程门阵列)在通信、计算机、控制等领域的应用越来越广泛,成为了一种重要的硬件设备。在很多高速应用中,FPGA已经成为了PCB(印制电路板)设计的一个重要组成部分,它使得高速电路的设计变得更加完善和可靠。本文将阐述基于FPGA的高速PCB设计的原理、技术和应用。一、FPGA的原理FPGA是一种具有可编程逻辑门和可编程输入/输出接口的芯片,它可以根据设计者的需求实现特定的逻辑功能或控制任务。在FPGA芯片中,有大量的可编程逻辑模块(CLB)

基于FPGA的高速AD采样设计.docx

基于FPGA的高速AD采样设计基于FPGA的高速AD采样设计摘要:高速模数转换(AD)采样是许多现代通信和信号处理系统中非常重要的一个环节。本论文针对高速AD采样的设计,提出了一种基于现场可编程门阵列(FPGA)的解决方案。通过详细介绍FPGA的基本原理和特性,并结合高速AD采样的需求,设计了一个带有高速数据接口的FPGA模块,实现了高速AD采样的功能。通过对各个模块进行详细设计和优化,实现了高速AD采样的同时保证了高精度和低功耗。实验结果表明,该设计能够满足高速AD采样的需求,并具有良好的性能和稳定性。