FPGA高速串行接口发送模块关键技术研究.docx

快乐****蜜蜂

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

FPGA高速串行接口发送模块关键技术研究.docx

FPGA高速串行接口发送模块关键技术研究论文题目:FPGA高速串行接口发送模块关键技术研究摘要:随着信息技术的快速发展和计算机应用广泛深入,对高速数据传输和通信的要求越来越高。因此,高速串行接口的设计和研究变得尤为重要。本论文针对FPGA高速串行接口发送模块的关键技术进行研究,包括时钟管理、信号编码、时序控制和误码校正等方面。通过对这些关键技术的深入分析和详细论述,本论文旨在给出一种可靠高效的FPGA高速串行接口发送模块设计方案。1.引言2.高速串行接口概述2.1高速串行接口的基本概念和应用领域2.2高速

基于FPGA的高速串行接口.pdf

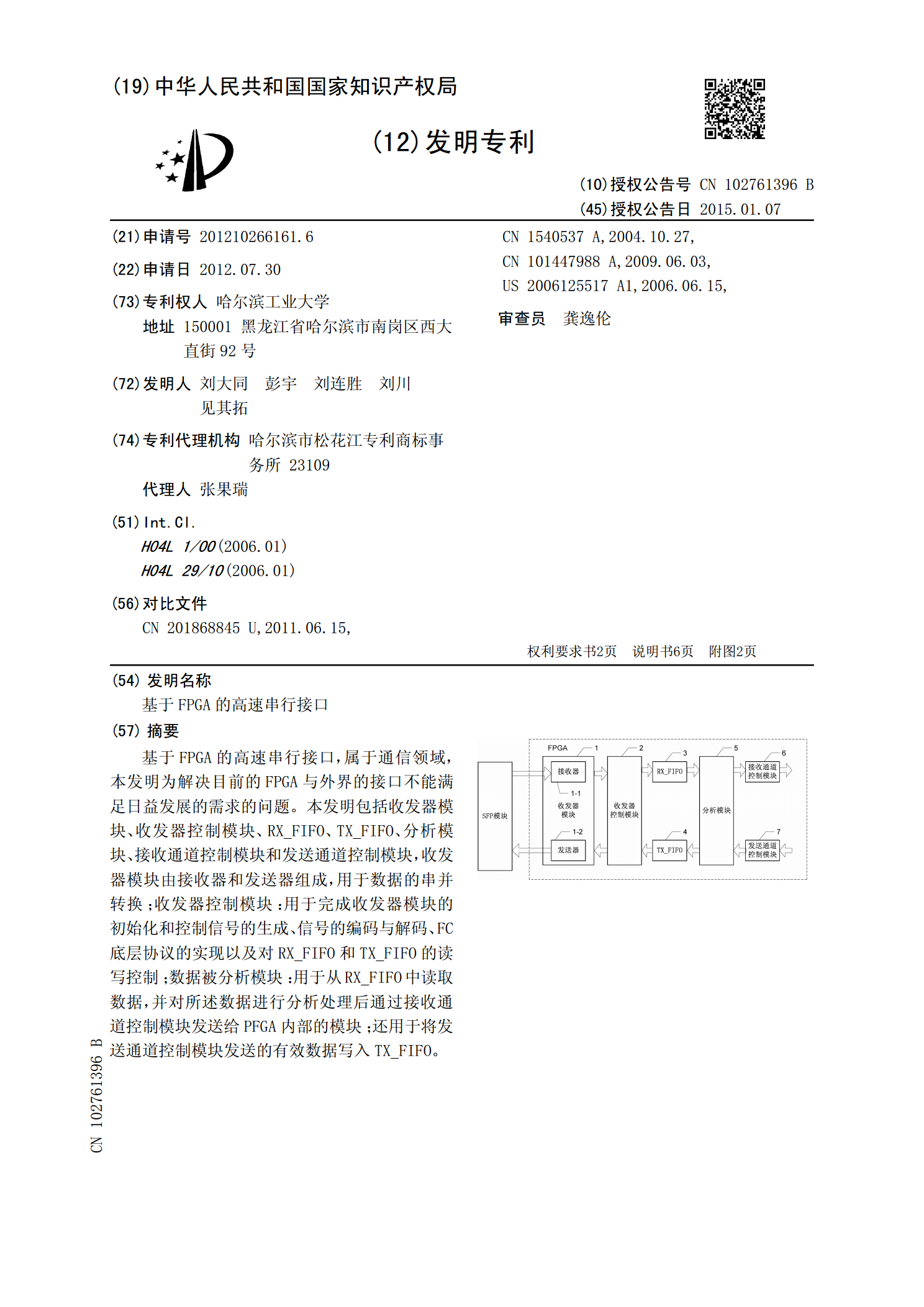

基于FPGA的高速串行接口,属于通信领域,本发明为解决目前的FPGA与外界的接口不能满足日益发展的需求的问题。本发明包括收发器模块、收发器控制模块、RX_FIFO、TX_FIFO、分析模块、接收通道控制模块和发送通道控制模块,收发器模块由接收器和发送器组成,用于数据的串并转换;收发器控制模块:用于完成收发器模块的初始化和控制信号的生成、信号的编码与解码、FC底层协议的实现以及对RX_FIFO和TX_FIFO的读写控制;数据被分析模块:用于从RX_FIFO中读取数据,并对所述数据进行分析处理后通过接收通道控

基于FPGA的高速串行接口模块仿真设计的中期报告.docx

基于FPGA的高速串行接口模块仿真设计的中期报告一、选题背景与意义随着现代通信技术的快速发展,高速通讯模块的设计越来越重要。高速串行接口模块是实现高速通信的关键部件之一,它在音视频领域、医疗器械领域、航空航天领域、军事领域等多个领域中都具有广泛的应用。基于FPGA的高速串行接口模块由于其高度可编程性和低延迟等特点越来越受到人们的关注。本项目旨在通过仿真设计,实现基于FPGA的高速串行接口模块。二、研究现状目前,基于FPGA的高速串行接口模块的研究已经有了较为成熟的技术路线。首先,需要选取合适的FPGA开发

5Gbs高速串行接口关键技术研究.docx

5Gbs高速串行接口关键技术研究摘要5G网络的发展和应用需要高速可靠的通信信道,高速串行接口技术成为必不可少的一部分。本文介绍了5Gbs高速串行接口技术的基础知识、关键技术、应用场景及瓶颈问题,并对以太网协议中的物理层技术进行了分析和探讨。最后,提出了未来5Gbs高速串行接口技术发展的建议和展望。关键词:5Gbs;高速串行接口技术;以太网协议;物理层技术;未来展望一、引言5G网络的快速发展驱动了无线通信技术和网络架构的进一步发展与演变。高速可靠的通信信道是实现5G网络的必要条件,高速串行接口技术作为5G网

高速串行接口接收机关键技术研究.docx

高速串行接口接收机关键技术研究高速串行接口(High-SpeedSerialInterface,简称HSI)是一种数据传输技术,用于在高速数据通信中实现高速、可靠的数据传输。在当今信息时代,高速串行接口在各种领域中得到广泛应用,如计算机内部通信、数据中心互连、通信网络、图像视频传输等。高速串行接口的性能直接影响到整个系统的性能,并且面临着多种技术挑战。一、引言高速串行接口接收机是实现高速、远距离、低功耗和抗干扰性能的关键技术。随着通信技术的发展和需求的增加,人们对高速串行接口接收机的要求越来越高。本文将从