WSN PLL频率综合器中分频器的设计.docx

快乐****蜜蜂

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

WSN PLL频率综合器中分频器的设计.docx

WSNPLL频率综合器中分频器的设计IntroductionFrequencysynthesizersareessentialcomponentsinmanywirelesscommunicationsystems.Inwirelesssensornetworks(WSN),frequencysynthesizersplayacriticalroleinachievingreliablecommunicationwithlowpowerconsumption.Aphase-lockedloop(PLL)i

用前置分频器的PLL频率合成器.docx

《锁相技术》课程结业论文题目:用前置分频器的PLL频率合成器设计院系名称:信息科学与工程学院专业班级:电子信息工程09级4班学生姓名:李永魁学号:200948300419授课教师:朱春华2012年4月28日摘要锁相技术是实现相位自动控制的一门学科。锁相原理在数学方面,早在30年代无线电技术发展的初期就已经出现了1930年已经建立了同步控制理论的基础。1932年贝尔赛什第一次公开发表了锁相环的数学描述。用锁相环路提取想干载波来完成同步检波。到了40年代。电视接收机中的同步扫描电路中开始广泛的应用锁相技术,使

应用于WSN的低功耗小数分频器和频率综合器的设计的任务书.docx

应用于WSN的低功耗小数分频器和频率综合器的设计的任务书任务书一、任务背景无线传感网络(WirelessSensorNetwork,简称WSN)是一种由大量分布式传感器节点组成的网络系统,它与微型电子技术、无线通信技术和信息处理技术等领域密切相关。WSN是一种低功耗、低成本、小型化的多媒体传输技术,被广泛应用于自然资源监测、环境检测、智能城市、生物医学等领域。在WSN中,时间同步和频率同步是WNS协议中的基础。传感节点需要精确的时间同步和频率同步,以便在无线通信中正确地共享信息。因此,低功耗小数分频器和频

一种新型高速低抖动低功耗双模预分频器及其在PLL频率综合器中的应用.pdf

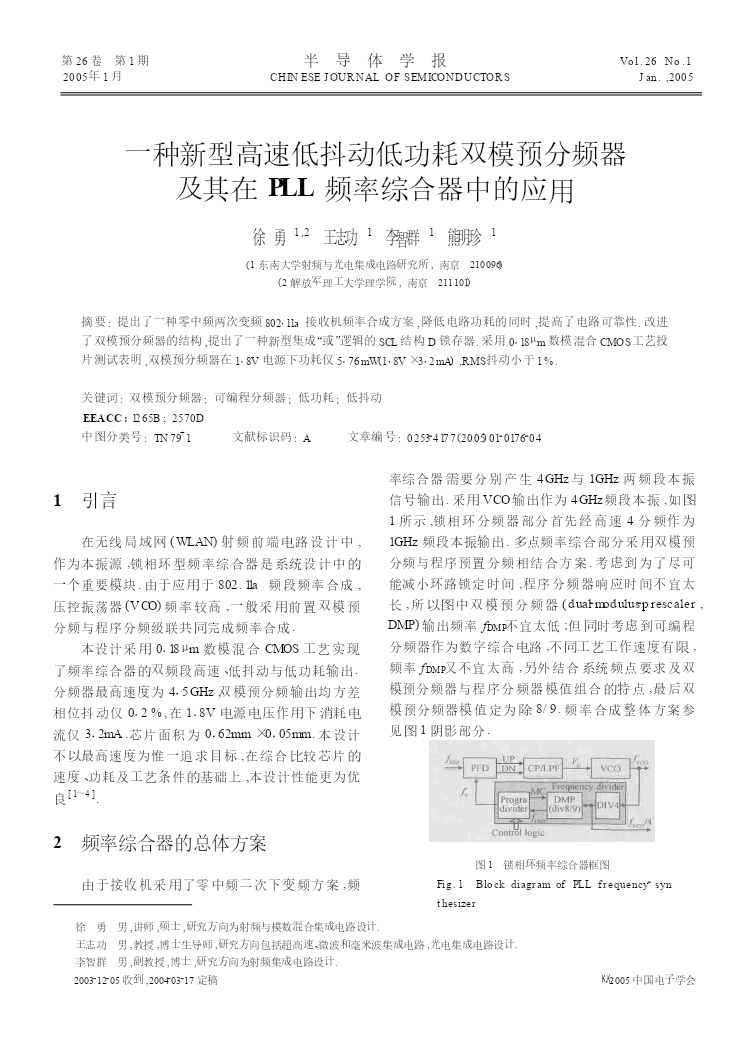

第26卷第1期半导体学报Vol.26No.12005年1月CHINESEJOURNALOFSEMICONDUCTORSJan.,2005一种新型高速低抖动低功耗双模预分频器及其在PLL频率综合器中的应用徐勇1,2王志功1李智群1熊明珍1(1东南大学射频与光电集成电路研究所,南京210096)(2解放军理工大学理学院,南京211101)摘要:提出了一种零中频两次变频802111a接收机频率合成方案,降低电路功耗的同时,提高了电路可靠性.改进了双模预分频器的结构,提出了一种新型集成“或”逻辑的SCL结构D锁存

DRM频率综合器中分频器的设计综述报告.pptx

汇报人:/目录0102报告的目的和意义DRM频率综合器概述分频器在DRM系统中的重要性03普通分频器数字分频器锁相环分频器混频器分频器原理比较分析04设计前的准备和考虑因素设计步骤和方法分频器电路设计分频器性能指标和测试方法05分频器的应用领域和实例分频器的发展趋势和未来展望分频器在DRM系统中的未来应用和挑战06总结报告内容对分频器设计的建议和展望对DRM频率综合器中分频器未来研究的建议和展望汇报人: