一种新型高速低抖动低功耗双模预分频器及其在PLL频率综合器中的应用.pdf

yy****24

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种新型高速低抖动低功耗双模预分频器及其在PLL频率综合器中的应用.pdf

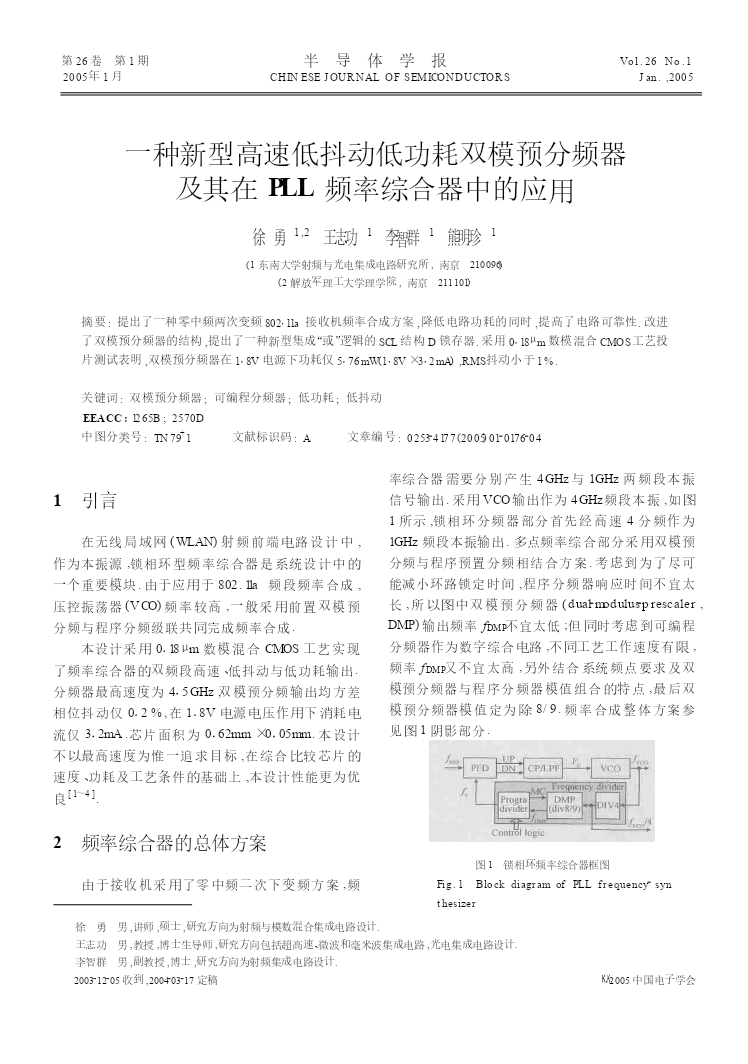

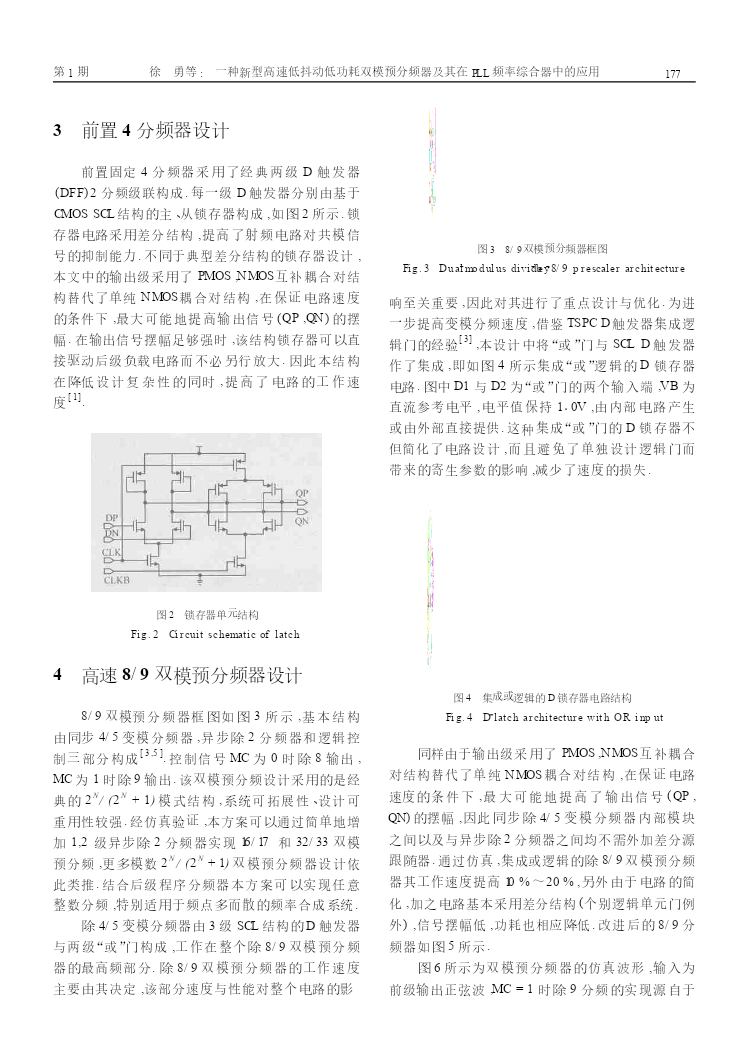

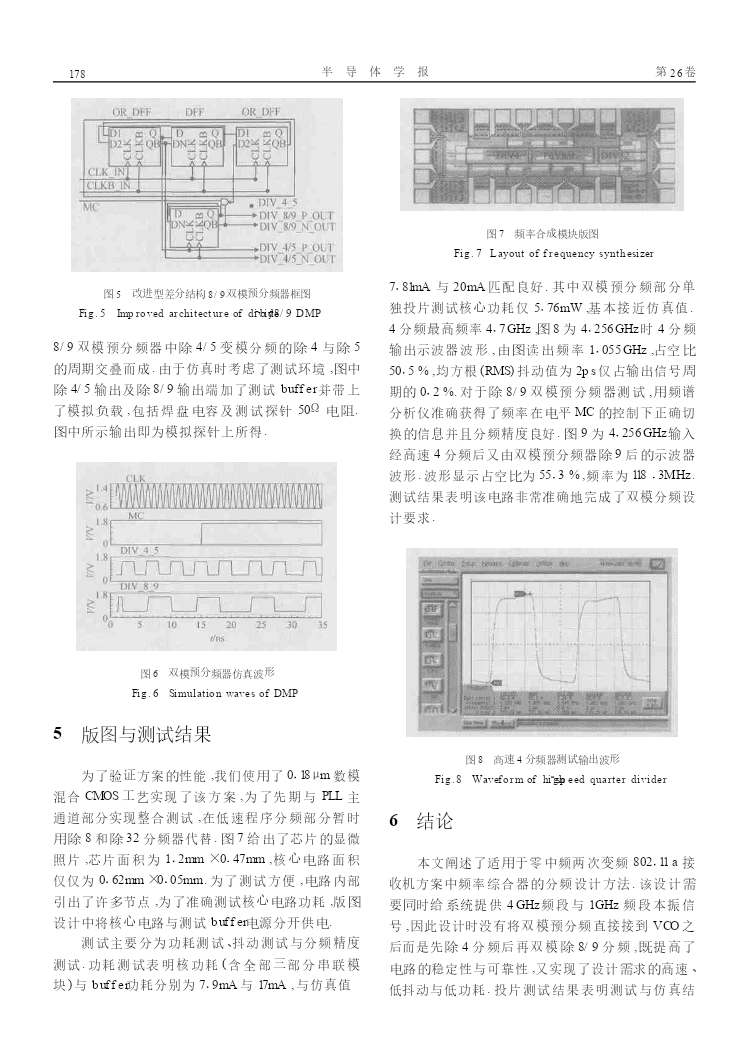

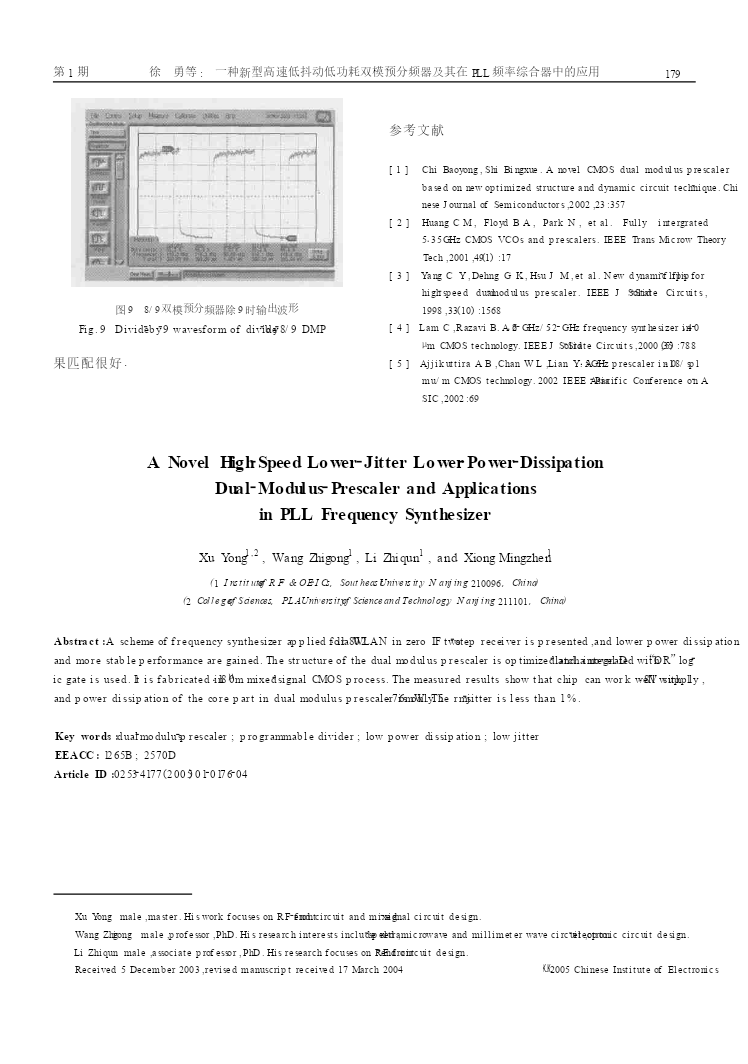

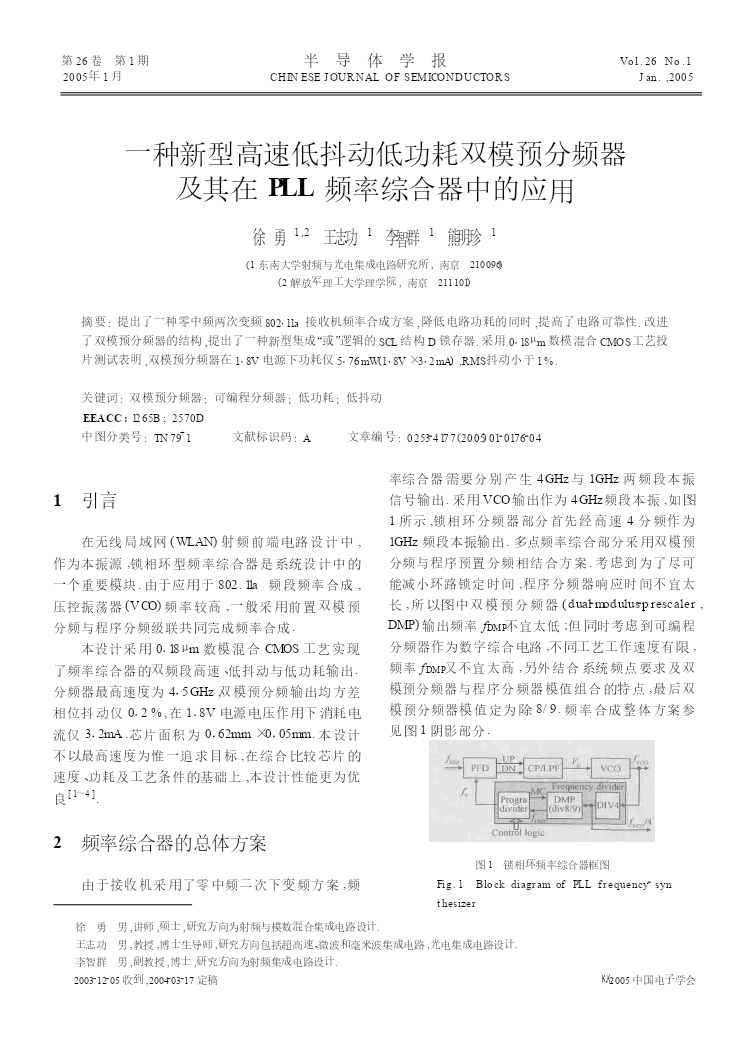

第26卷第1期半导体学报Vol.26No.12005年1月CHINESEJOURNALOFSEMICONDUCTORSJan.,2005一种新型高速低抖动低功耗双模预分频器及其在PLL频率综合器中的应用徐勇1,2王志功1李智群1熊明珍1(1东南大学射频与光电集成电路研究所,南京210096)(2解放军理工大学理学院,南京211101)摘要:提出了一种零中频两次变频802111a接收机频率合成方案,降低电路功耗的同时,提高了电路可靠性.改进了双模预分频器的结构,提出了一种新型集成“或”逻辑的SCL结构D锁存

WSN PLL频率综合器中分频器的设计.docx

WSNPLL频率综合器中分频器的设计IntroductionFrequencysynthesizersareessentialcomponentsinmanywirelesscommunicationsystems.Inwirelesssensornetworks(WSN),frequencysynthesizersplayacriticalroleinachievingreliablecommunicationwithlowpowerconsumption.Aphase-lockedloop(PLL)i

频率综合器中低功耗高速多模分频器设计的“时间借用”方法.pdf

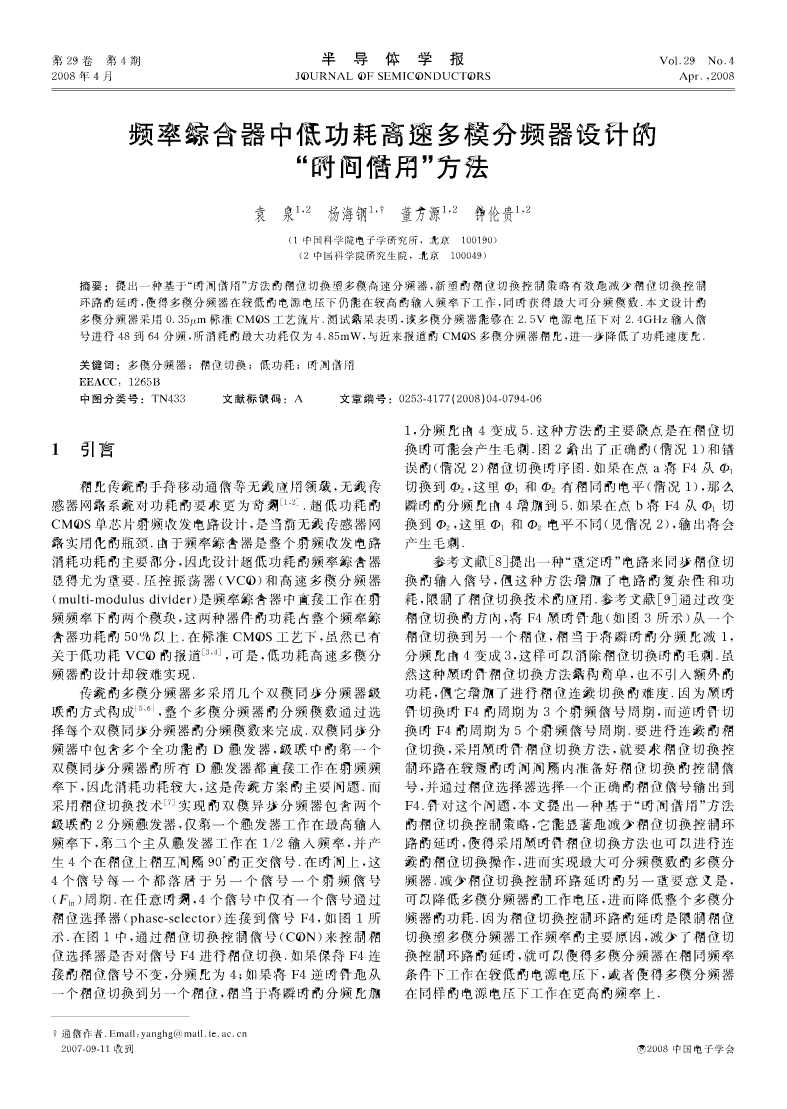

第29卷第4期半导体学报犞狅犾.29犖狅.42008年4月犑犗犝犚犖犃犔犗犉犛犈犕犐犆犗犖犇犝犆犜犗犚犛犃狆狉.,2008频率综合器中低功耗高速多模分频器设计的“时间借用”方法袁泉1,2杨海钢1,董方源1,2钟伦贵1,2(1中国科学院电子学研究所,北京100190)(2中国科学院研究生院,北京100049)摘要:提出一种基于“时间借用”方法的相位切换型多模高速分频器,新型的相位切换控制策略有效地减少相位切换控制环路的延时,使得多模分频器在较低的电源电压下仍能在较高的输入频率下工作,同时获得最大可分频模数

WSN-PLL频率综合器中分频器的设计的开题报告.docx

WSNPLL频率综合器中分频器的设计的开题报告尊敬的评委老师:我是一名电子信息工程专业的本科生,我的毕业设计题目为“WSNPLL频率综合器中分频器的设计”。以下是我的开题报告:一、选题背景近年来,随着物联网技术的快速发展,无线传感器网络(WirelessSensorNetwork,WSN)逐渐成为人们关注的热点。WSN是由大量分布式的、无线联网的传感器节点组成的网络,其广泛应用于环境监听、运动追踪、健康监测、安全防范等领域。在WSN中,频率同步是实现多节点协同工作的重要前提。而PLL频率综合器则是实现频率

射频接收机中低抖动双模分频器.pdf

第28卷第12期半导体学报犞狅犾.28犖狅.122007年12月犆犎犐犖犈犛犈犑犗犝犚犖犃犔犗犉犛犈犕犐犆犗犖犇犝犆犜犗犚犛犇犲犮.,2007犔狅狑犑犻狋狋犲狉,犇狌犪犾犕狅犱狌犾狌狊犘狉犲狊犮犪犾犲狉狊犳狅狉犚犉犚犲犮犲犻狏犲狉狊,,犜犪狀犵犔狌1,犠犪狀犵犣犺犻犵狅狀犵1,犎犲犡犻犪狅犺狌1,犔犻犣犺犻狇狌狀1,犡狌犢狅狀犵12,犔犻犠犲犻1,犪狀犱犌狌狅犉犲狀犵1(1犐狀狊狋犻狋狌狋犲狅犳犚犉牔犗犈犐犆狊,犛狅狌狋犺犲犪狊狋犝狀犻狏犲狉狊犻狋狔,犖犪狀犼犻狀犵210096,犆犺犻狀犪)(2犐