围栅硅纳米线MOS器件模型与工艺的研究的开题报告.docx

骑着****猪猪

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

围栅硅纳米线MOS器件模型与工艺的研究的开题报告.docx

围栅硅纳米线MOS器件模型与工艺的研究的开题报告题目:围栅硅纳米线MOS器件模型与工艺的研究摘要:随着芯片制造技术的不断发展,集成电路中器件尺寸不断缩小,其中纳米级别的器件逐渐成为研究热点。本文主要研究围栅硅纳米线MOS器件的模型和工艺,结合理论模拟和实验验证,分析其电学性能及可行性。关键词:围栅硅纳米线MOS器件、模型、工艺、电学性能一、研究背景围栅硅纳米线MOS器件是一种用于芯片制造的新型器件,具有尺寸小、性能优、功耗低等优点。在其制造过程中,需要对其进行设计、制造和优化,以保证器件的电学性能和可靠性

围栅硅纳米线MOS器件模型与工艺的研究.docx

围栅硅纳米线MOS器件模型与工艺的研究围栅硅纳米线MOS器件模型与工艺的研究摘要:近年来,随着纳米技术的发展,围栅硅纳米线(GAA-SiNW)场效应晶体管被广泛研究和应用。本文基于围栅硅纳米线MOS器件模型和工艺的研究,探讨了其性能特点和应用前景。首先,简要介绍了围栅硅纳米线MOS器件的结构和制备工艺。然后,分析了围栅硅纳米线MOS器件的特点和电学性能。最后,讨论了围栅硅纳米线MOS器件的应用前景和挑战。关键词:围栅硅纳米线;MOS器件;模型;工艺;性能特点1.引言围栅硅纳米线(GAA-SiNW)场效应晶

围栅硅纳米线器件性能潜力研究.docx

围栅硅纳米线器件性能潜力研究围栅硅纳米线(Gate-all-aroundsiliconnanowires)器件是一种新兴的纳米尺度电子器件,具有巨大的性能潜力和应用前景。本文将围绕围栅硅纳米线器件的结构特点、性能潜力以及相关的研究方向展开讨论。围栅硅纳米线器件采用纳米尺度的硅纳米线作为通道,周围环绕着一个完全封闭的栅极。相比于传统的金属氧化物半导体场效应晶体管(MOSFET)结构,围栅硅纳米线器件具有更好的电流控制能力、更低的功耗和更小的占用面积。围栅硅纳米线器件的性能潜力主要体现在以下几个方面:首先,围

围栅硅纳米线器件性能潜力研究的中期报告.docx

围栅硅纳米线器件性能潜力研究的中期报告随着纳米技术的不断发展,围栅硅纳米线器件越来越受到关注。本研究旨在探究围栅硅纳米线器件的性能潜力。本中期报告主要介绍已完成的研究进展及未来的研究计划。已完成的研究进展:1.制备了围栅硅纳米线器件我们采用化学气相沉积法制备围栅硅纳米线,并采用电子束光刻和干法刻蚀技术制备了围栅硅纳米线场效应晶体管。经过测试,器件的性能表现良好,与已有文献中的结果相符合。2.研究了器件的电学性能我们通过调节围栅长度和宽度等参数,研究了器件的传输特性和电流-电压特性。实验结果表明,较小的围栅

纳米线围栅MOS器件及其制备方法.pdf

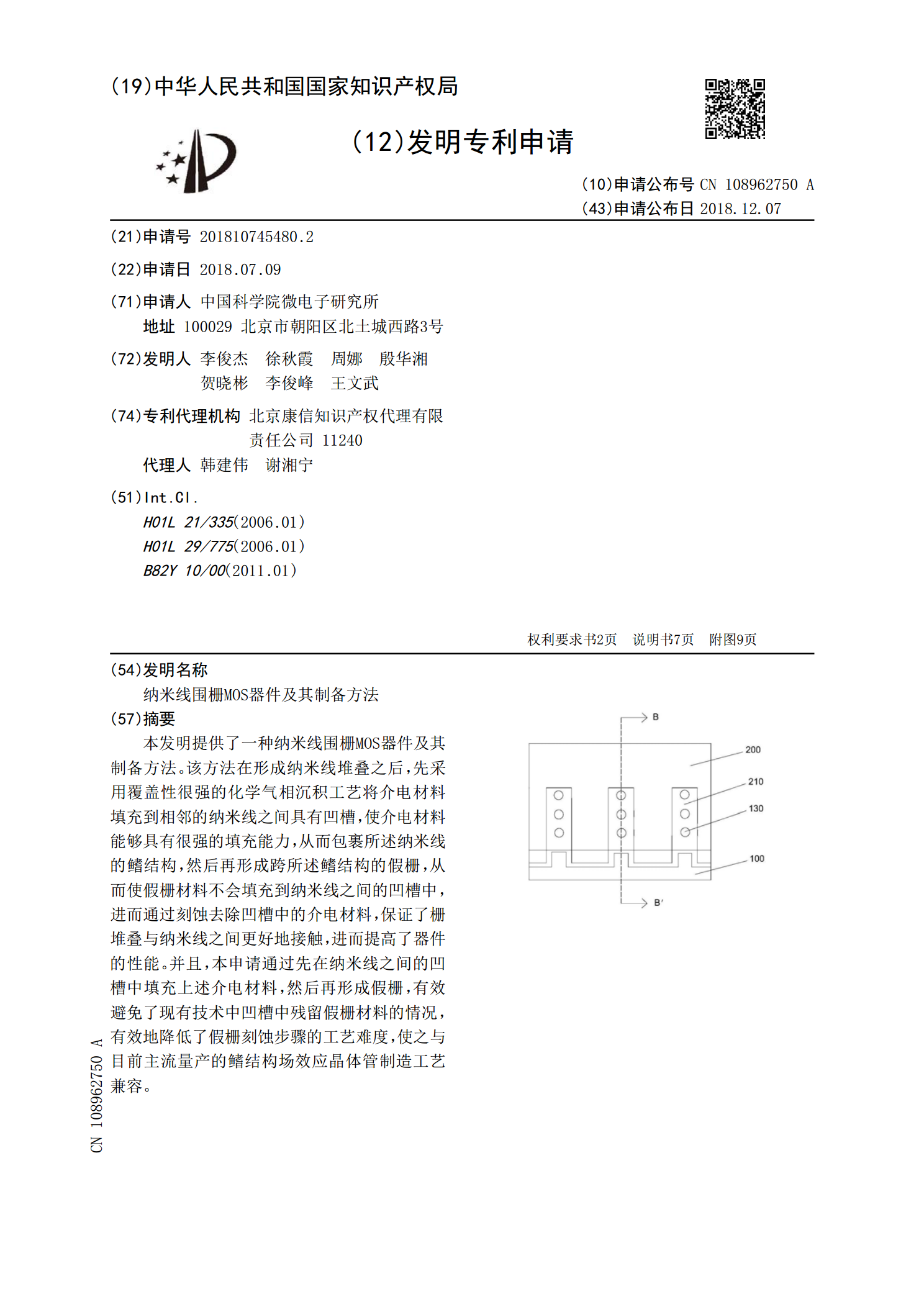

本发明提供了一种纳米线围栅MOS器件及其制备方法。该方法在形成纳米线堆叠之后,先采用覆盖性很强的化学气相沉积工艺将介电材料填充到相邻的纳米线之间具有凹槽,使介电材料能够具有很强的填充能力,从而包裹所述纳米线的鳍结构,然后再形成跨所述鳍结构的假栅,从而使假栅材料不会填充到纳米线之间的凹槽中,进而通过刻蚀去除凹槽中的介电材料,保证了栅堆叠与纳米线之间更好地接触,进而提高了器件的性能。并且,本申请通过先在纳米线之间的凹槽中填充上述介电材料,然后再形成假栅,有效避免了现有技术中凹槽中残留假栅材料的情况,有效地降低