数模转换与模数转换.pptx

骑着****猪猪

亲,该文档总共39页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

数模转换与模数转换.pptx

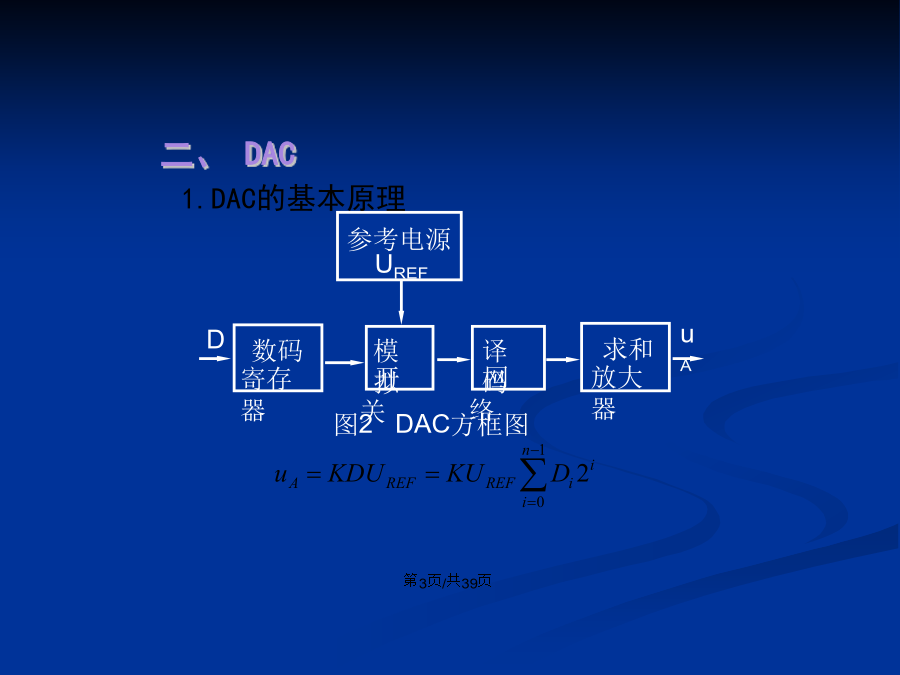

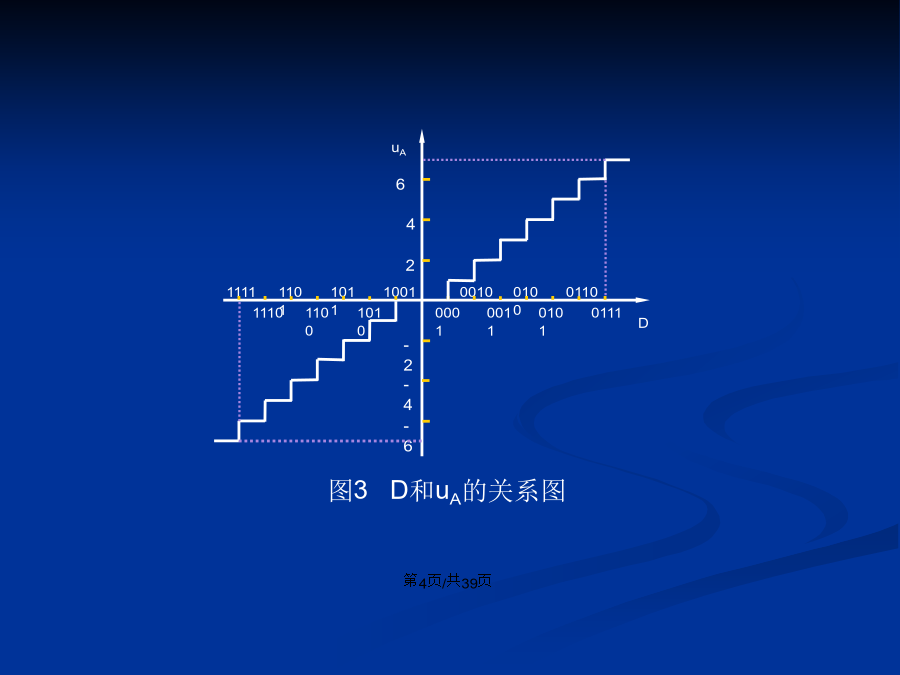

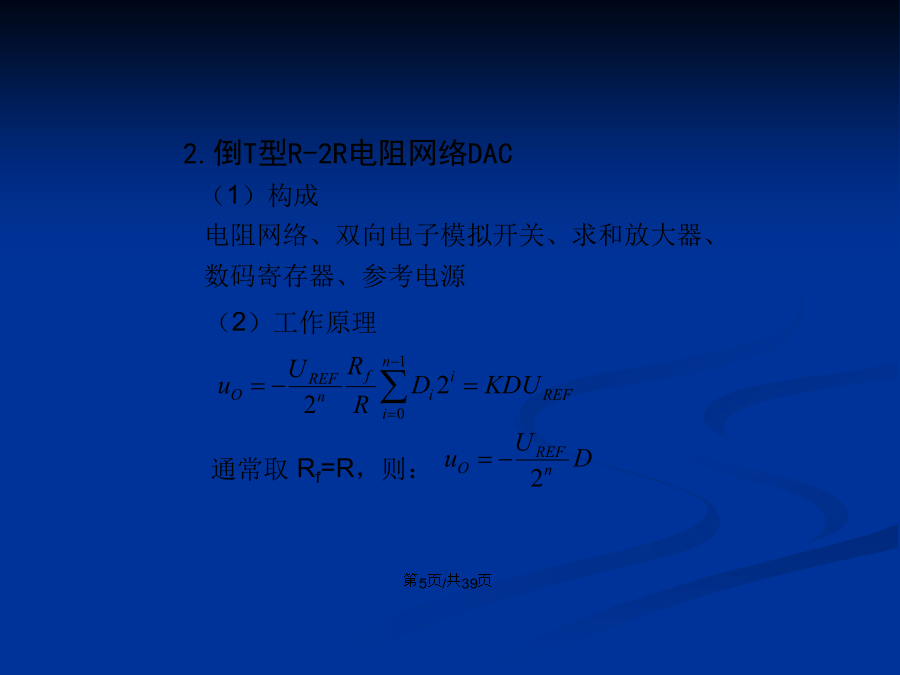

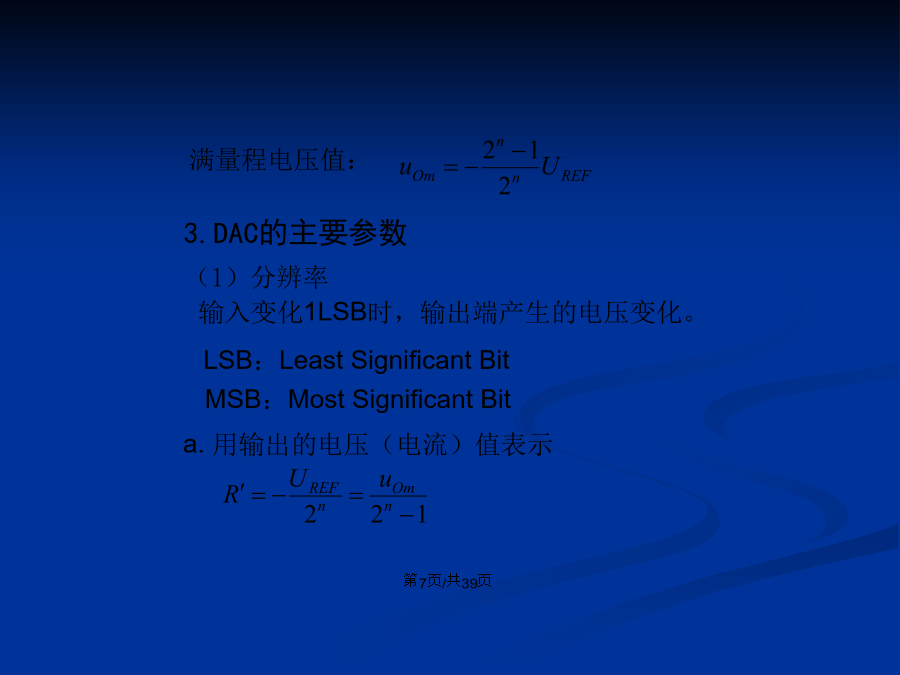

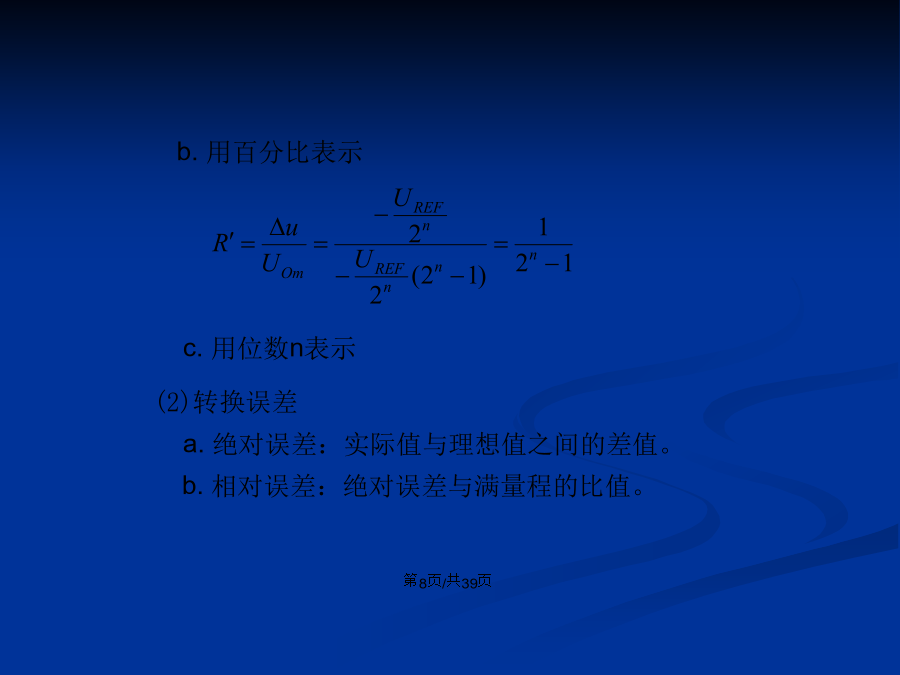

会计学目录1.概念及其应用二、DAC图3D和uA的关系图(1)构成图4倒T型R-2R电阻网络D/A转换电路满量程电压值:b.用百分比表示从输入的数字量发生突变开始,直到输出电压进入与稳态值相差±½LSB范围以内的这段时间。三、ADCO图5模拟信号的采样保持(1)组成直到最低位比较完为止。此时JKFF中所存的数码就是所求的输出数字量。图64位逐次逼近型A/D转换器结构图CPb.用百分比表示绝对误差与额定最大输入模拟值(FSR)的比值,通常用百分数表示。四、常用D/A转换器美国NationalSemicond

数模模数转换.ppt

数/模转换与模/数转换A/D、D/A转换0A/D转换器的作用1.采样与保持2.量化与编码的过程◆模数转换电路分为:直接比较型和间接比较型◆直接比较型:就是将输入模拟信号直接与标准的参考电压比较,从而得到数字量。属于这种类型常见的有并行ADC和逐次比较型ADC。◆间接比较型:输入模拟量不是直接与参考电压比较,而是将二者变为中间的某种物理量再进行比较,然后将比较所得的结果进行数字编码。(1)并行ADC表9.1三位并行ADC转换真值表(2)逐次比较型ADC逐次逼近型ADCD/A转换器(DAC)就是一种将离散的数

数模和模数转换.ppt

第五讲数模和模数转换5.1概述能将模拟量转换为数字量的电路称为模数转换器,简称A/D转换器或ADC;能将数字量转换为模拟量的电路称为数模转换器,简称D/A转换器或DAC。ADC和DAC是沟通模拟电路和数字电路的桥梁,也可称之为两者之间的接口。5.2D/A转换器将输入的每一位二进制代码按其权的大小转换成相应的模拟量,然后将代表各位的模拟量相加,所得的总模拟量就与数字量成正比,这样便实现了从数字量到模拟量的转换。转换特性(1)分辨率分辨率用输入二进制数的有效位数表示。在分辨率为n位的D/A转换器中,输出电压能

数模模数转换原理.pdf

模数和数模转换.ppt

概述模拟信号到数字信号的转换称为模—数转换,或称为A/D(AnalogtoDigital)能将模拟量转换为数字量的电路称为模数转换器,简称A/D转换器或ADC;能将数字量转换为模拟量的电路称为数模转换器,简称D/A转换器或DAC。A/D转换器(ADC)A/D转换器(ADC)一、转换原理1.采样定理2.量化和编码⒉量化编码例如:要将01V的模拟电压转换为三位二进制代码方法二:取=2/15V,01/15V的电压以0×表示,则§9-3-2采样-保持电路1.并联比较型A/D转换器寄存器:由七个D触发