AD中文数据手册.doc

17****21

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

AD中文数据手册.doc

AD9854特征·300M内部时钟频率·可进行频移键控(FSK),二元相移键控(BPSK),相移键控(PSK),脉冲调频(CHIRP),振幅调制(AM)操作·正交的双通道12位D/A转换器·超高速比较器,3皮秒有效抖动偏差·外部动态特性:80dB无杂散动态范围(SFDR)@100MHz(±1MHz)AOUT·4倍到20倍可编程基准时钟乘法器·两个48位可编程频率寄存器·两个14位可编程相位补偿寄存器·12位振幅调制和可编程的通断整形键控功能·单引脚FSK和BPSK数据输入接口·PSK功能可由I/O接口实现

AD中文数据手册.docx

AD9854特征·300M内部时钟频率·可进行频移键控(FSK),二元相移键控(BPSK),相移键控(PSK),脉冲调频(CHIRP),振幅调制(AM)操作·正交的双通道12位D/A转换器·超高速比较器,3皮秒有效抖动偏差·外部动态特性:80dB无杂散动态范围(SFDR)@100MHz(±1MHz)AOUT·4倍到20倍可编程基准时钟乘法器·两个48位可编程频率寄存器·两个14位可编程相位补偿寄存器·12位振幅调制和可编程的通断整形键控功能·单引脚FSK和BPSK数据输入接口·PSK功能可由I/O接口实现

AD9880中文数据手册.pdf

BY:ql_smbjAD9880中文数据手册全文翻译自:ADI公司AD9880B数据手册英文AD9880数据手册版本号:Rev.0BY:ql_smbj简单描述AD9880是一个集模拟接口和HDMI接口于一体单个芯片,并且还支持HDCP。1.1模拟接口AD9880是一个真正8位的150MSPS的单片模拟接口,用于对复合视频(YPbPr)和RGB图像信号的采集。有150MSPS的编码速率和330MHz的带宽,所以支持全部HDTV格式(最高1080p)和最高SXGA(1280*1024@75Hz)的FED。Ad

AD8132中文数据手册.pdf

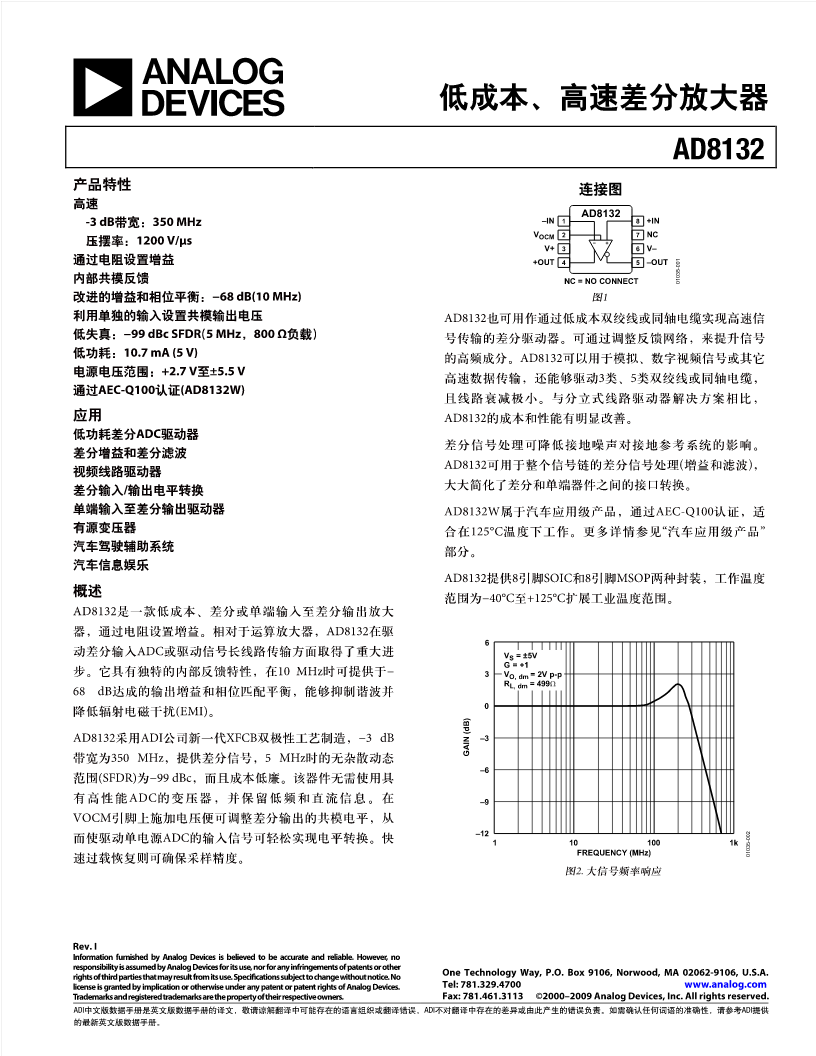

低成本、高速差分放大器AD8132产品特性连接图高速AD8132-3dB带宽:350MHz–IN18+IN压摆率:1200V/μsVOCM27NCV+36V–通过电阻设置增益+OUT45–OUT内部共模反馈01035-001NC=NOCONNECT改进的增益和相位平衡:−68dB(10MHz)图1利用单独的输入设置共模输出电压AD8132也可用作通过低成本双绞线或同轴电缆实现高速信低失真:−99dBcSFDR(5MHz,800Ω负载)号传输的差分驱动器。可通过调整反馈网络,来提升信号低功耗:10.7mA(

AD9854中文数据手册.docx

DDS模块设计DDS模块的设计是本系统的重点,也是本章阐述的重点。DDS模块主要是围绕芯片AD9852进行设计的,设计要求既要满足性能指标,还要求优化电路,减小电路面积,否则13路DDS共同存在会使系统体积显得较大。下面先介绍AD9852的基本特性。4.2.1AD9852介绍图4-2AD9852功能结构框图chart4-2AD9852functionandstructure如图4-2所示,AD9852内部包括一个具有48位相位累加器、一个可编程时钟倍频器、一个反sinc滤波器、两个12位300MHzDAC