AD9854中文数据手册.docx

快乐****蜜蜂

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

AD9854中文数据手册.docx

DDS模块设计DDS模块的设计是本系统的重点,也是本章阐述的重点。DDS模块主要是围绕芯片AD9852进行设计的,设计要求既要满足性能指标,还要求优化电路,减小电路面积,否则13路DDS共同存在会使系统体积显得较大。下面先介绍AD9852的基本特性。4.2.1AD9852介绍图4-2AD9852功能结构框图chart4-2AD9852functionandstructure如图4-2所示,AD9852内部包括一个具有48位相位累加器、一个可编程时钟倍频器、一个反sinc滤波器、两个12位300MHzDAC

AD9854中文数据手册要点.docx

AD9854特征·300M内部时钟频率·可进行频移键控(FSK),二元相移键控(BPSK),相移键控(PSK),脉冲调频(CHIRP),振幅调制(AM)操作·正交的双通道12位D/A转换器·超高速比较器,3皮秒有效抖动偏差·外部动态特性:80dB无杂散动态范围(SFDR)@100MHz(±1MHz)AOUT·4倍到20倍可编程基准时钟乘法器·两个48位可编程频率寄存器·两个14位可编程相位补偿寄存器·12位振幅调制和可编程的通断整形键控功能·单引脚FSK和BPSK数据输入接口·PSK功能可由I/O接口实现

AD9854中文手册个人翻译版.docx

AD9854并行和串行驱AD9854简介AD9854最高支持300MHz的时钟速率,内置的倍频器能实现4到20倍的倍频,拥有48位可编程频率寄存器和14位可编程相位偏移寄存器以及12位可编程幅度调节寄存器,集成了12位的DAC,支持最高速率为10MHz的串行编程或者最高速率为100MHz的并行编程。如何使用AD9854内部和外部的更新时钟此功能是由一个双向的I/O管脚即20管脚和一个可编程的32位递减计数器来实现的。为了使输出波形能随着写入控制寄存器的值改变,需要提供给20管脚一个上升沿的时钟信号或者由内

中文数据手册.doc

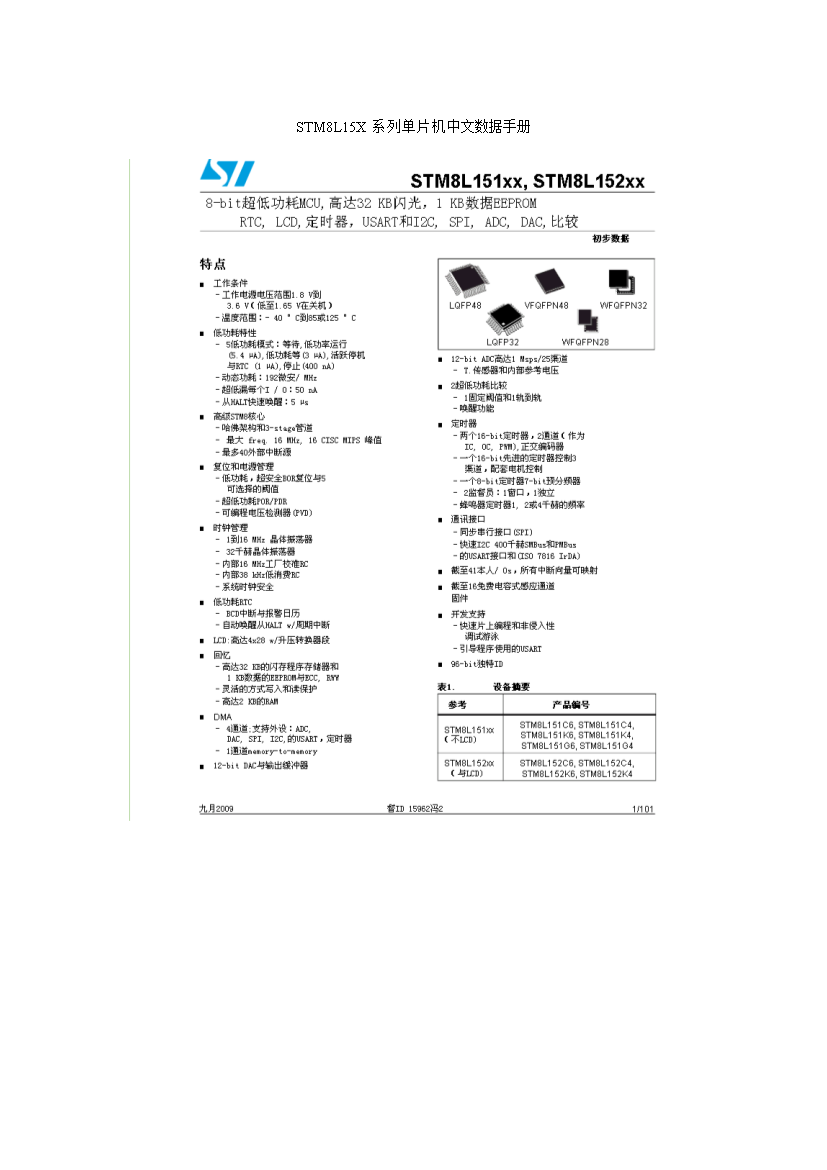

STM8L15X系列单片机中文数据手册

中文数据手册.doc

STM8L15X系列单片机中文数据手册