直接数字频率合成器.pptx

骑着****猪猪

亲,该文档总共40页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

直接数字频率合成器.pptx

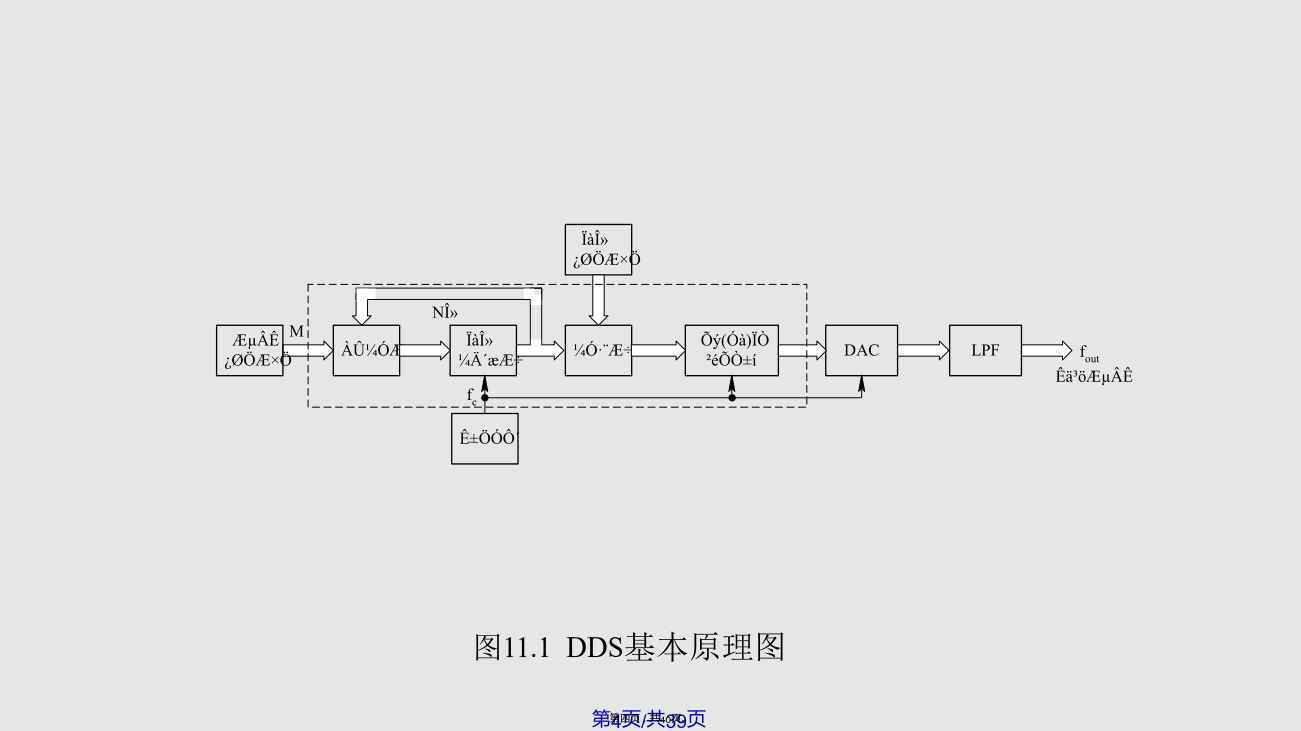

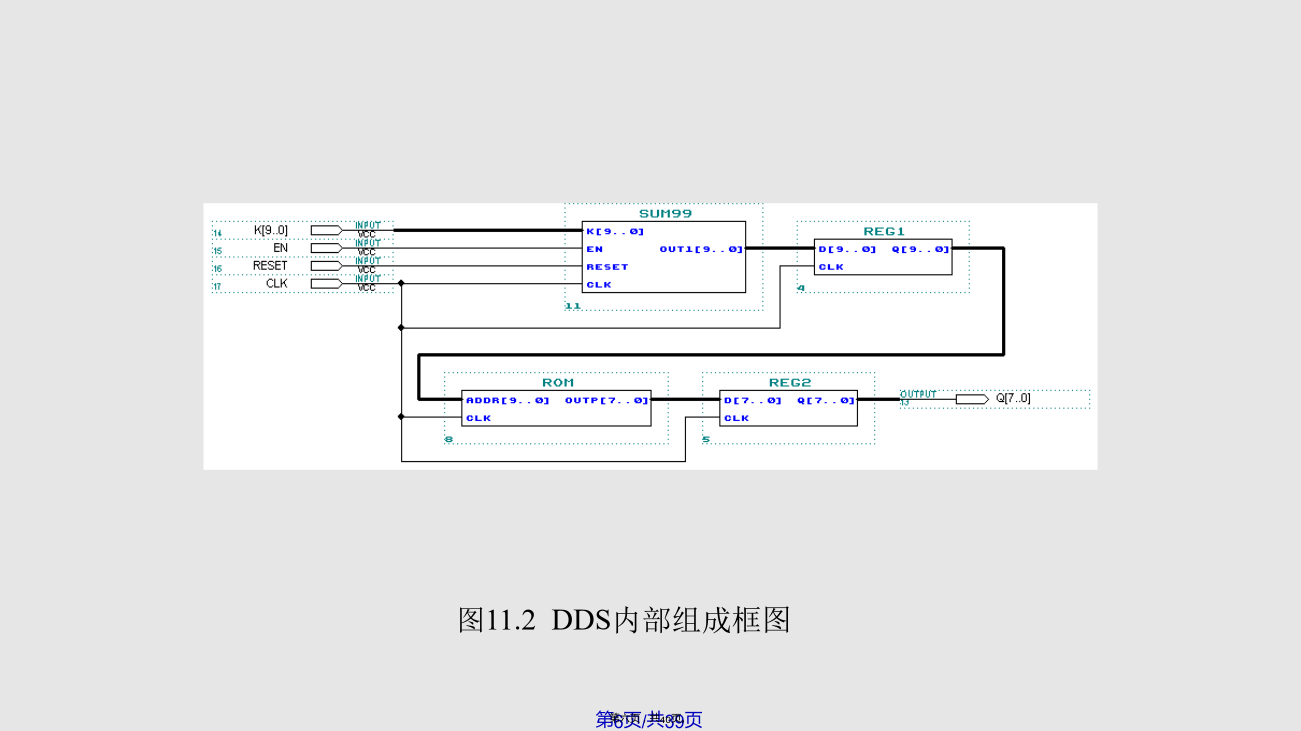

DDS技术是一种把一系列数字形式的信号通过DAC转换成模拟形式的信号合成技术,目前使用最广泛的一种DDS方式是利用高速存储器作查找表,然后通过高速DAC输出已经用数字形式存入的正弦波。DDS技术具有频率切换时间短(<20ns),频率分辨率高(0.01Hz),频率稳定度高,输出信号的频率和相位可以快速程控切换,输出相位可连续,可编程以及灵活性大等优点,它以有别于其他频率合成方法的优越性能和特点成为现代频率合成技术中的姣姣者。DDS广泛用于接受机本振、信号发生器、仪器、通信系统、雷达系统等,尤其适合跳频无线通

直接数字频率合成器.docx

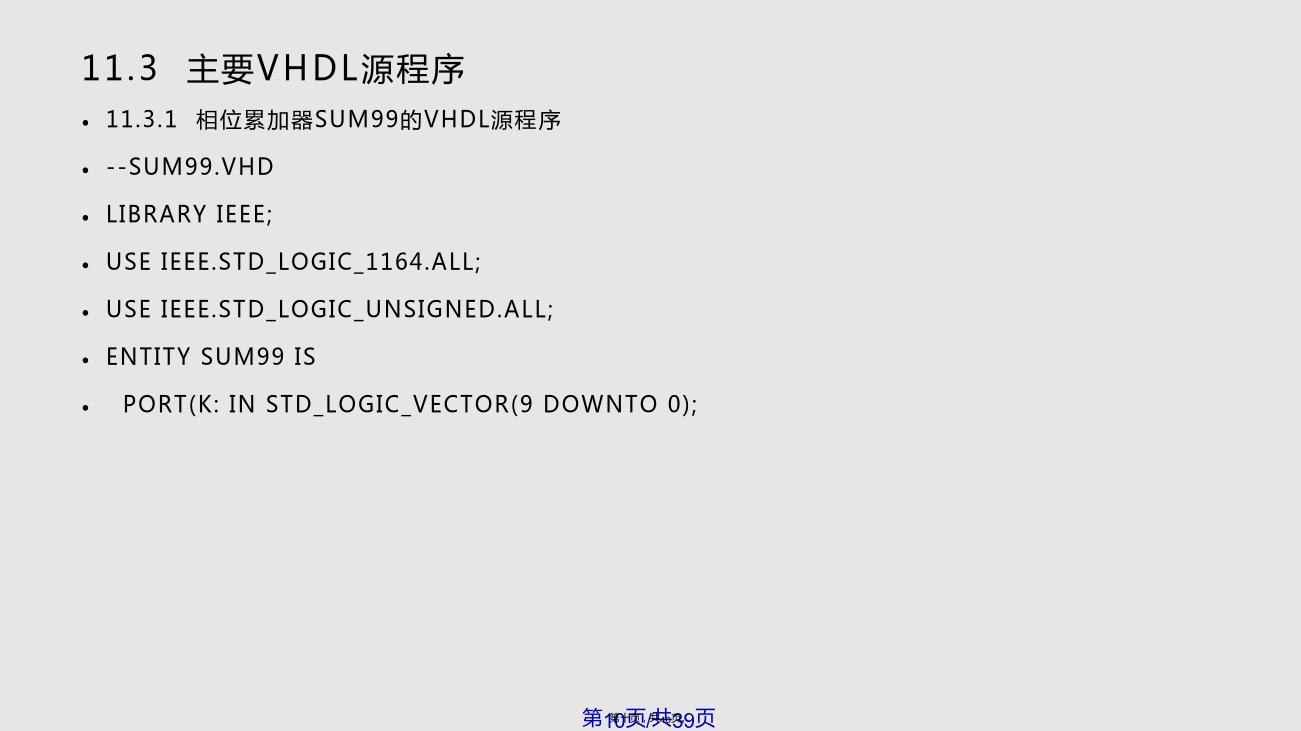

EDA设计II实验名称:直接数字频率合成器学号:0804480122姓名:田冬院系:电子工程与光电技术学院专业:信息对抗技术指导老师:蒋立平时间:2011年6月1日目录摘要关键词¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨设计基本要求¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨方案论证¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨各子模块设计原理说明波形存储器模块¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨相位累加器模块¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨相位调节器¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨波形输出模块¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨¨频

直接数字频率合成器quartus.docx

电子线路课程设计直接数字频率合成器学号:姓名:2011年11月摘要本篇论文主要讲了用eda设计dds。用quartus软件模拟仿真电路,并下载到芯片。使电路能输出正余弦波,并可调节频率和相位。并在这基础上进行一部分扩展,如能输入矩形三角形波。关键词eda设计ddsquartusAbstract:ThisreportintroducestheEDAdesigniscompletedwithDirectDigitalSynthesisDDSprocess.ThisdesignusesDDSQuartusII7

直接数字频率合成器开题报告.doc

毕业设计(论文)开题报告题目基于FPGA的直接数字频率合成专业名称通信工程班级学号09042138学生姓名周忠指导教师刘敏填表日期2013年1月8日一、选题的依据及意义:直接数字频率合成器(DirectDigitalFrequencySynthesizer)是一种基于全数字技术从相位概念出发直接合成所需波形的一种频率合成技术。其

直接数字频率合成器开题报告.doc

毕业设计(论文)开题报告题目基于FPGA的直接数字频率合成专业名称通信工程班级学号09042138学生姓名周忠指导教师刘敏填表日期2013年1月8日一、选题的依据及意义:直接数字频率合成器(DirectDigitalFrequencySynthesizer)是一种基于全数字技术从相位概念出发直接合成所需波形的一种频率合成技术。其