一种基于FPGA的手套机机头电磁铁控制方法.pdf

Th****84

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种基于FPGA的手套机机头电磁铁控制方法.pdf

本发明公布了一种基于FPGA的手套机机头电磁铁控制方法,该方法包括单片机控制方法和FPGA控制方法的实现;单片机通过FSMC来发送电磁铁状态信号;并且FPGA使用FSMC接收模块来接收控制信号,再通过延时计数器处理信号,然后循环状态机不断轮询处理后的信号,产生最终的电磁铁控制输出信号。本发明大幅简化了手套机机头电磁铁控制算法的复杂度,提高了控制实时性,并从硬件的设计角度减少了烧毁电磁铁的概率。

一种手套机的机头驱动装置.pdf

本发明公开了一种手套机的机头驱动装置,包括机架,机架的两端设有人字墙板,机架的一侧安装有驱动电机,驱动电机的动力轴上连接有驱动轮,机架的另一侧安装有从动轮,驱动轮和从动轮之间连接有同步带,同步带上固定连接有连接座,连接座上固定连接有两根钢丝绳,机架的两端和人字墙板两端上均连接有供钢丝绳穿过的滑轮装置,钢丝绳上固定连接有机头。本发明通过驱动电机带动与同步带连接的钢丝绳带动机头实现往复运动,整体结构简单,占用安装面积小,制造装配简单,便于安装维修,且传动稳定,生产效率高。

一种手套机机头传动装置.pdf

本发明提供一种手套机机头传动装置,包括机架和电机安装座,右人字墙板的两端底部分别设有第一固定座和第二固定座,左人字墙板的两端底部分别设有第三固定座和第四固定座;一传动主轴安装于第一固定座和第二固定座之间,所述传动主轴的两端分别设有第一主动轮和第二主动轮;第三固定座和第四固定座内分别设有第一从动轮和第二从动轮;第一主动轮通过第一同步带连接所述第一从动轮,第二主动轮通过第二同步带连接第二从动轮;电机带轮通过第三同步带连接所述同步带轮;前机头通过第一传动块与第一同步带传动连接,后机头通过第二传动块与第二同步带传

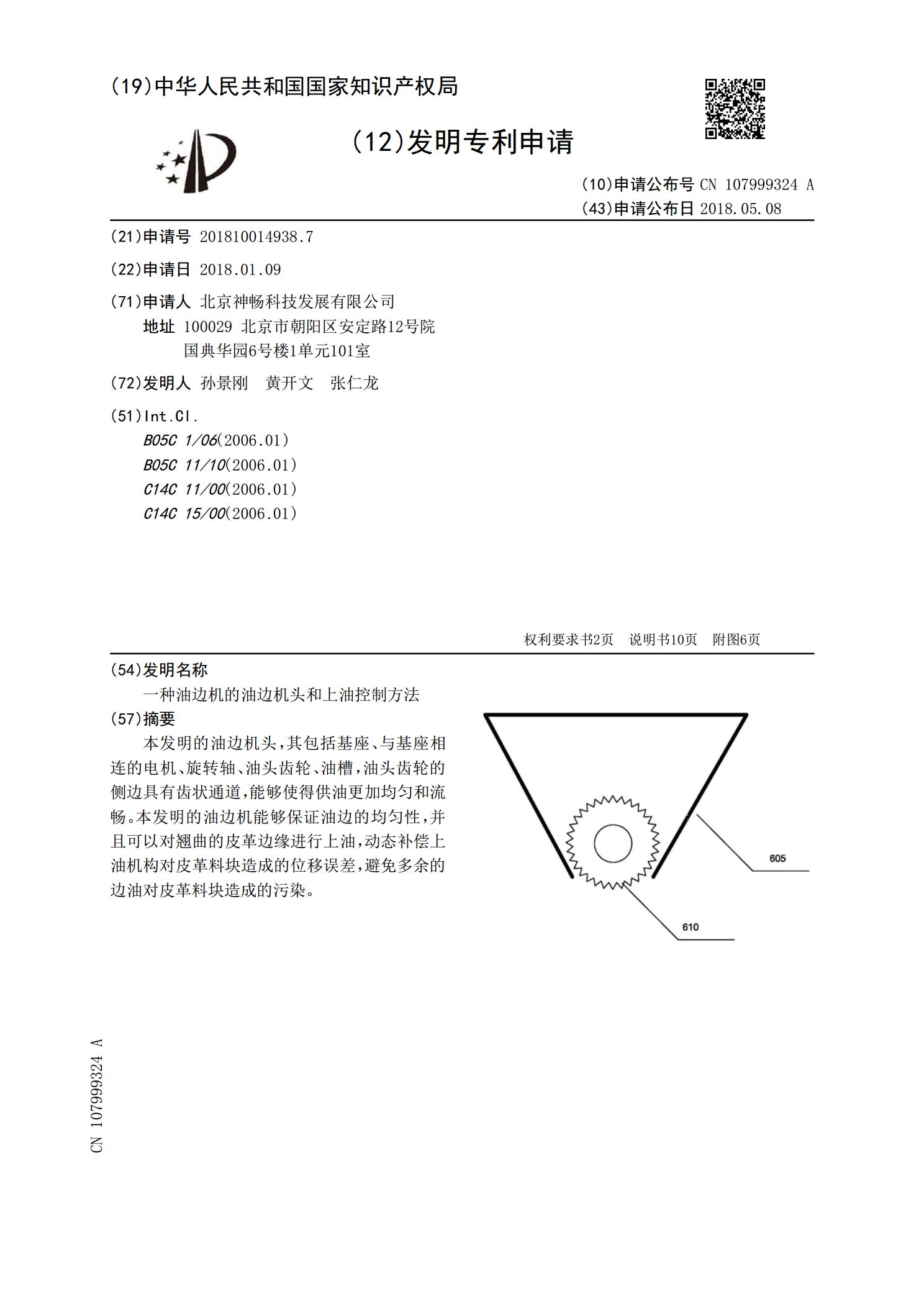

一种油边机的油边机头和上油控制方法.pdf

本发明的油边机头,其包括基座、与基座相连的电机、旋转轴、油头齿轮、油槽,油头齿轮的侧边具有齿状通道,能够使得供油更加均匀和流畅。本发明的油边机能够保证油边的均匀性,并且可以对翘曲的皮革边缘进行上油,动态补偿上油机构对皮革料块造成的位移误差,避免多余的边油对皮革料块造成的污染。

基于ARM的手套机控制器设计.docx

基于ARM的手套机控制器设计Title:DesignofanARM-BasedGloveControllerforHandGestureRecognitionAbstract:Inrecentyears,gesturerecognitionhasgainedsignificantattentionasameansofhuman-computerinteraction.Theabilitytocontroldevicesthroughhandgesturescangreatlyenhanceuserexpe