微机原理 第4章+存储器系统.ppt

qw****27

亲,该文档总共54页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

微机原理 第4章+存储器系统.ppt

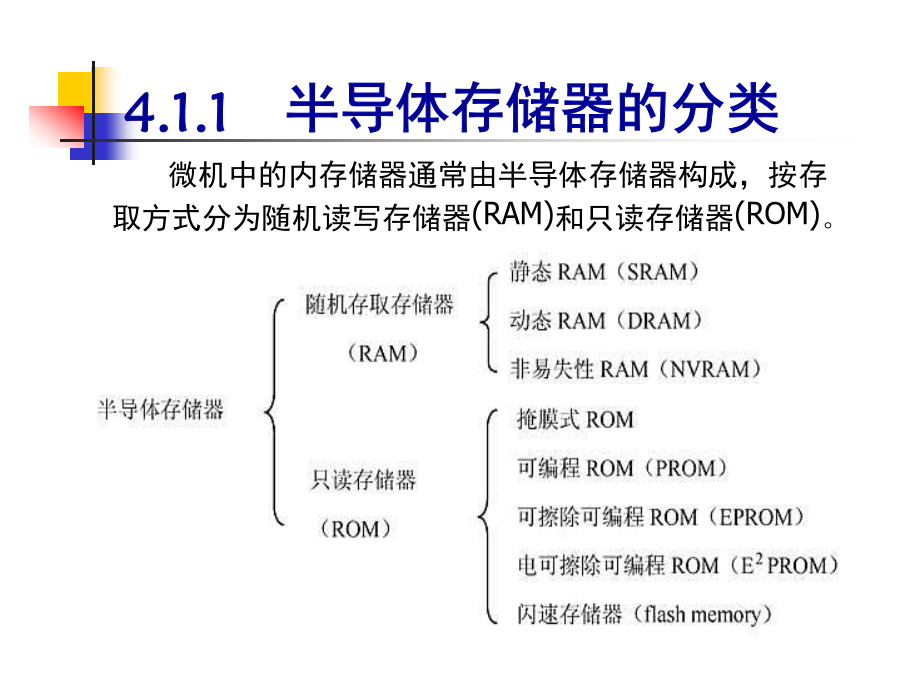

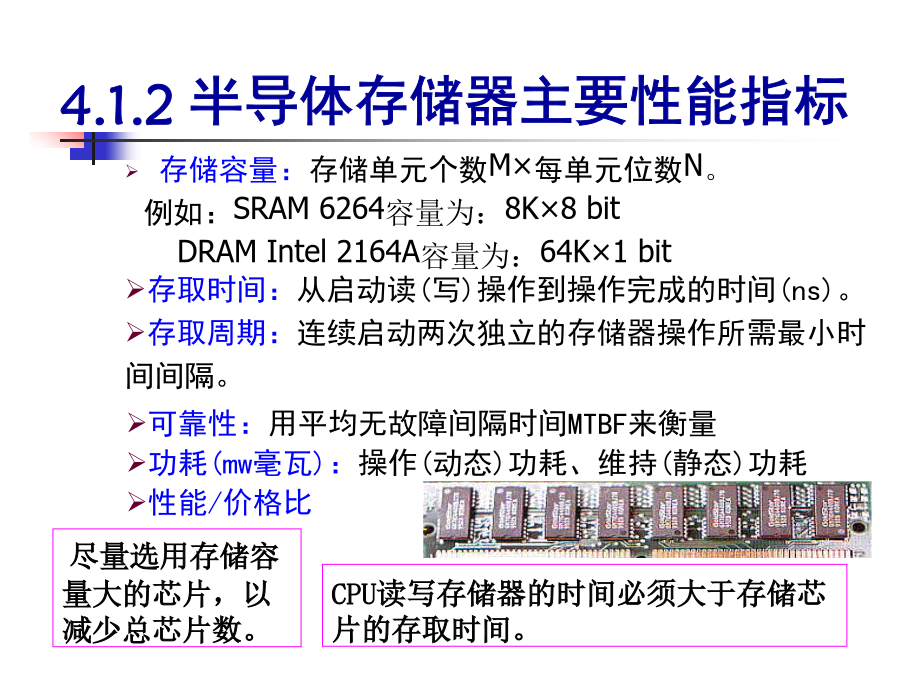

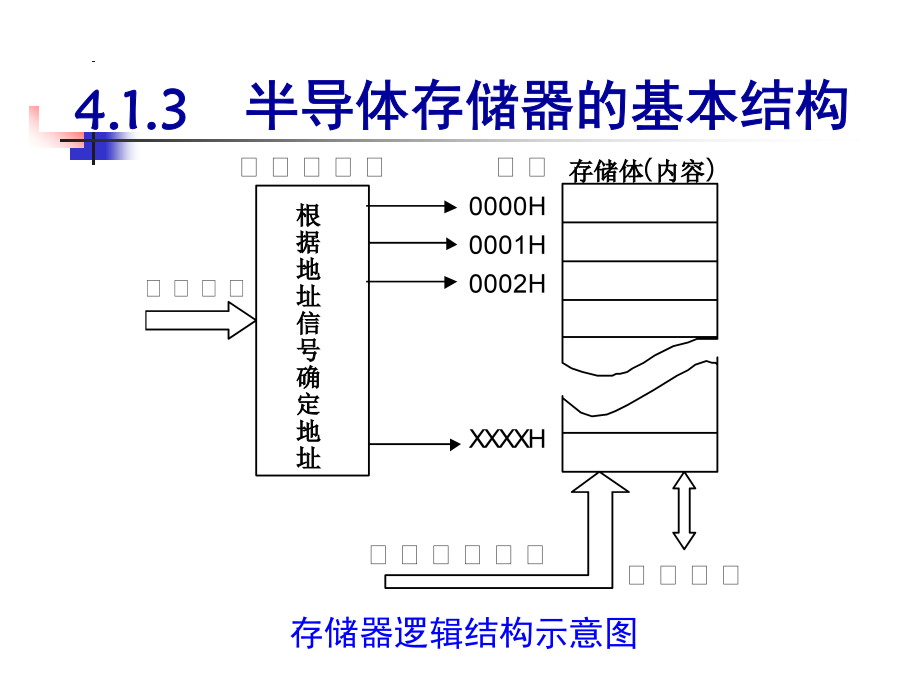

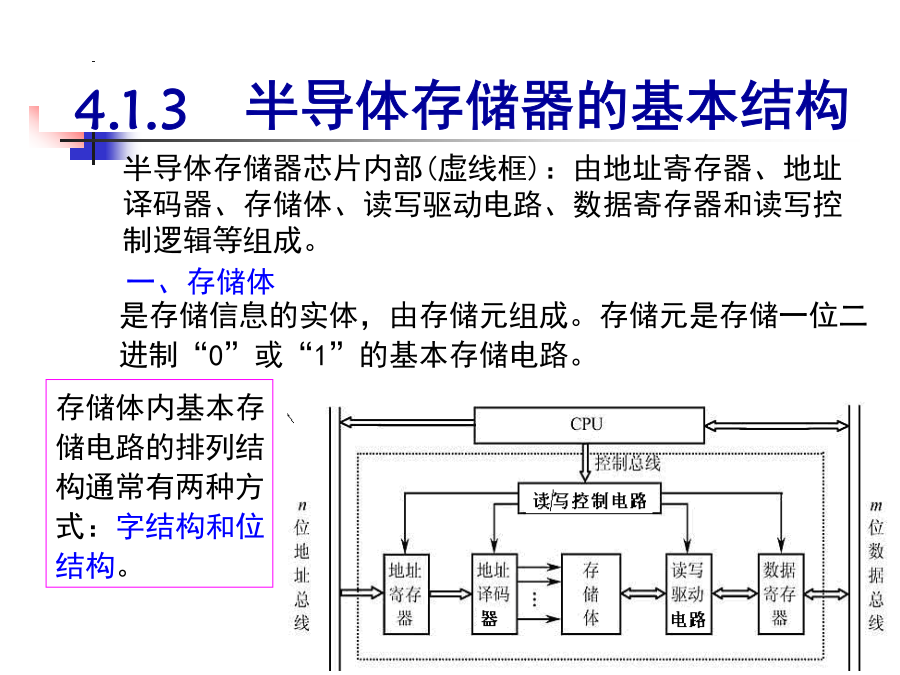

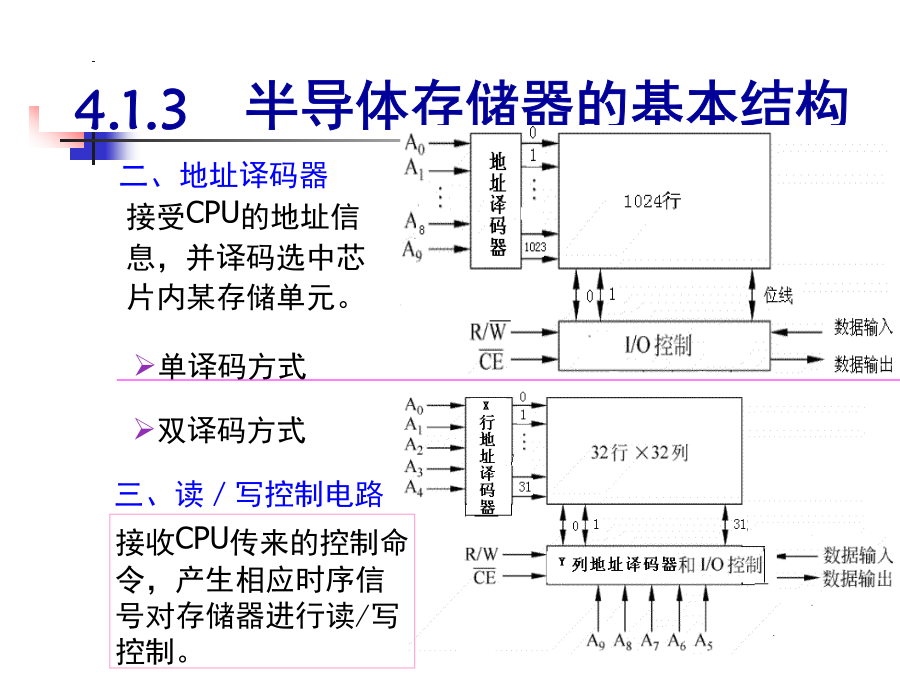

第4章本章重点4.1存储器概述4.1.1半导体存储器的分类根据存储器芯片内部基本单元电路的结构不同,RAM又分为:(1)静态随机读写存储器SRAM(1)掩膜式ROM采用掩膜工艺(即光刻图形技术)一次性直接写入的。4.1.2半导体存储器主要性能指标4.1.3半导体存储器的基本结构4.1.3半导体存储器的基本结构4.1.3半导体存储器的基本结构4.2随机读写存储器RAM4.2随机读写存储器RAM4.2随机读写存储器RAM4.2随机读写存储器RAM4.2随机读写存储器RAM(2)部分地址译码4.2随机读写存储器

微机原理及应用第5章——存储器.ppt

第五章存储器第二节随机存取存储器RAM2.典型SRAM芯片二、动态随机存取存储器(DRAM)三、8086对存储器的读/写时序(b)写周期第三节半导体只读存储器ROMEPROM的使用技巧:4.E2PROM5.闪速存储器(FlashMemory)第四节存储器的扩展1.位数的扩展2.存储容量的扩展(2)译码法3.存储器逻辑设计举例二、主存储器与CPU的连接(2)与分时复用总线的8位CPU的连接(3)与准16位8088CPU的连接采用74LS373为地址锁存器,采用74LS245为数据收发器。3.主存储器芯片与8

微机接口 第5章存储器系统.ppt

第5章存储器系统主要内容:§5.1概述一、存储器系统1.存储器系统的一般概念2.两种存储系统Cache存储系统虚拟存储系统3.主要性能指标4.微机中的存储器二、半导体存储器1.半导体存储器2.内存储器的分类随机存取存储器(RAM)只读存储器(ROM)3.主要技术指标§5.2随机存取存储器一、静态存储器SRAM1.SRAM的特点2.典型SRAM芯片典型SRAM芯片6264芯片的主要引线6264的工作过程3.8088总线信号4.6264芯片与系统的连接5.存储器编址存储器地址6264芯片的编址存储器编址6.译

微机原理9微机接口存储器.ppt

第7章半导体存储器及其接口半导体存储器概述存储器的分类1、按存储介质分类半导体存储器、磁表面存储器、光表面存储器2、按存储器的读写功能分类随机存取存储器RAM:可读可写、断电丢失只读存储器ROM:正常只读、断电不丢失3、按用途分类内存储器、外存储器4、按在微机系统中的作用分类主存储器、辅助存储器、高速缓冲存储器5、按制造工艺双极型:速度快、集成度低、功耗大MOS型:速度慢、集成度高、功耗低半导体存储器的分类只读存储器ROM随机读写存储器RAM分类存储器的基本性能指标随机读写存储器:静态RAM(SRAM)基

微机存储器系统.ppt

6.1概述6.1.1存储系统的层次结构6.1.2存储器的分类6.1.3存储器的基本组成6.1.4存储器的技术指标6.2半导体读写存储器6.2.1静态RAM6.2.2动态RAM6.2.3存储器的工作时序6.1.1存储系统的层次结构存储器的分类存储器的基本组成6.2.1静态RAM2.静态RAM组成VF5存储器的工作时序掩膜式ROM有双极型和MOS型两种类型可编程、可擦除的只读存储器——EPROM6.4.13.常用的译码电路行地址和列地址的形成RAS和CAS的产生存储器RASCAS小结