考研必备计算机组成原理第2章 计算机的逻辑部件.ppt

qw****27

亲,该文档总共88页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

考研必备计算机组成原理第2章 计算机的逻辑部件.ppt

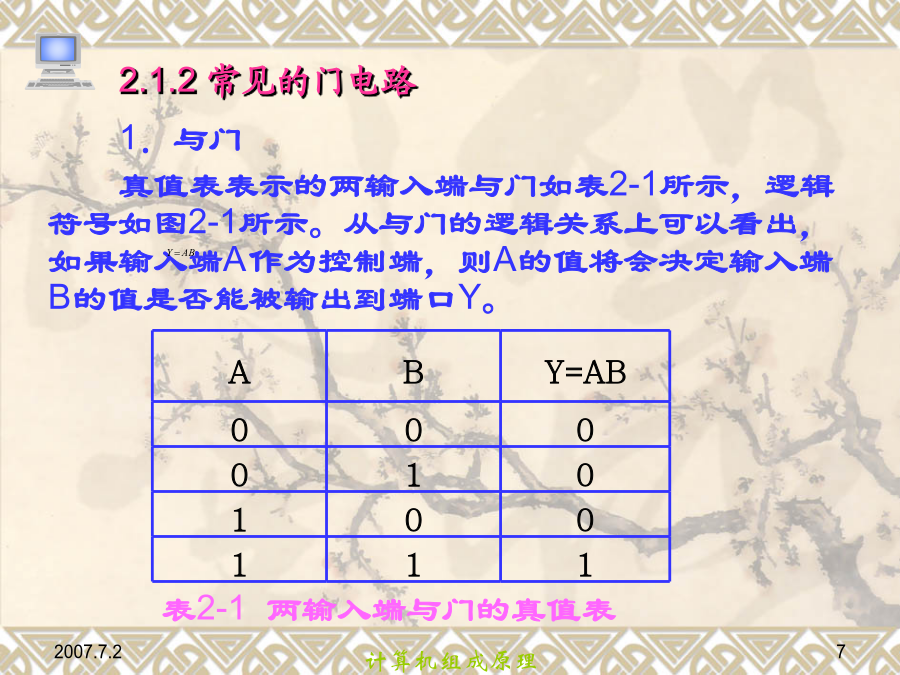

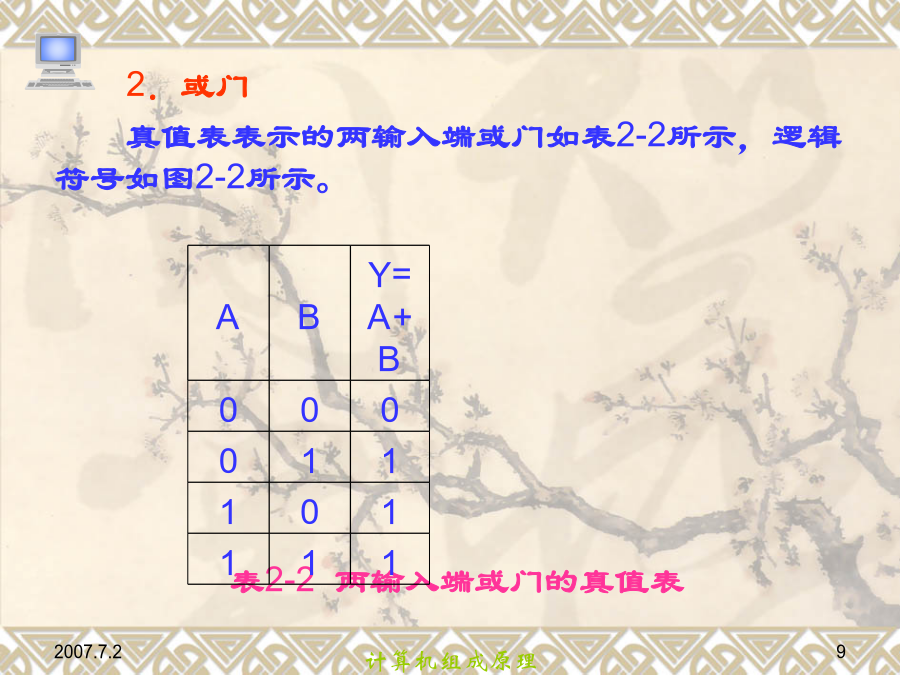

第2章计算机的逻辑部件计算机的逻辑部件本章要点:2.1.1逻辑代数的基本知识通常电子系统中都含有模拟和数字两种模块。和模拟电路相比较,在存储、分析或传输信号时,数字电路更具优越性。在数字电路中,常用二进制数来量化连续变化的模拟信号,而二进制数正好是用数字1和0来表示的。这里的0和1不是十进制数中的数字,逻辑0和逻辑1不代表数值大小,仅表示相互矛盾、相互对立的两种逻辑状态,这样就可借助复杂的数字系统来实现信号的存储、分析和传输。2.逻辑电平2.1.2常见的门电路(a)国外符号(b)国标符号图2-1两输入端与

考研必备计算机组成原理第2章 计算机的逻辑部件费.ppt

第2章计算机的逻辑部件计算机的逻辑部件本章要点:2.1.1逻辑代数的基本知识通常电子系统中都含有模拟和数字两种模块。和模拟电路相比较,在存储、分析或传输信号时,数字电路更具优越性。在数字电路中,常用二进制数来量化连续变化的模拟信号,而二进制数正好是用数字1和0来表示的。这里的0和1不是十进制数中的数字,逻辑0和逻辑1不代表数值大小,仅表示相互矛盾、相互对立的两种逻辑状态,这样就可借助复杂的数字系统来实现信号的存储、分析和传输。2.逻辑电平2.1.2常见的门电路(a)国外符号(b)国标符号图2-1两输入端与

计算机组成原理第2章计算机的逻辑部件.ppt

第二章计算机的逻辑部件2.1布尔代数的基础知识与逻辑二、逻辑代数的公式和定理(3)基本定理(A+B)(A+C)=AA+AB+AC+BC(4)常用公式互补率A+A=12.2逻辑函数的化简:代数化简法:(P16)代数化简法是直接利用布尔代数的基本公式和规则进行化简的一种方法。例:化简逻辑函数F=A·B+Ā·C+B·C·DF=AB+ĀC+BCD=(AB+ĀC+BC)+BCD=(AB+ĀC)+(BC+BCD)=(AB+ĀC)+BC=AB+ĀC卡诺图化简法:(P17)逻辑函数的最小项及其性质逻辑函数的最小项表达式用

计算机组成原理与系统结构 第2章 逻辑部件基础.ppt

第2章逻辑部件基础本章主要内容:2.1计算机中常用的组合逻辑电路2.2时序逻辑电路2.3时序逻辑电路设计基础--有限状态机理论2.4阵列逻辑电路2.1计算机常用组合逻辑电路常见的组合逻辑电路有加法器、算术逻辑单元、译码器、数据选择器等。2.1.1加法器2.全加器下面以4位超前进位加法器为例来说明,其逻辑图如图2-6所示。2.1.2算术逻辑单元图2-916位快速ALU2.1.3数值比较器2.1.4数据选择器根据逻辑图可以写T574(1/2)的输出表达式。2.1.5译码器2.2时序逻辑电路2.2.1触发器图2

计算机组成原理课件 考研必备.ppt

计算机组成原理为配合由高等教育出版社出版的面向21世纪课程教材《计算机组成原理》教学和自学的需要,随书出版了《计算机组成原理》配套课件。为了配合该教材的第2版,本课件在保留原课件特色的基础上,做了相应的补充和修改。该课件与《计算机组成原理》第2版教材在体系上完全一致,它以课堂教学为依托,帮助读者边阅读边思考,通过点击鼠标,逐行显示精练的文字和简明的图表,既可从文稿中对教材的重点和难点加深理解,又可从视图中看到动画演示效果,形象地理解各种电路的工作原理和设计思路。新版课件提供了章目录和节目录。操作上除了顺序