印刷电路板及其制造方法.pdf

17****27

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

印刷电路板及其制造方法.pdf

(19)中华人民共和国国家知识产权局(12)发明专利说明书(10)申请公布号CN102577642A(43)申请公布日2012.07.11(21)申请号CN201080045505.X(22)申请日2010.08.05(71)申请人LG伊诺特有限公司地址韩国首尔(72)发明人金镇秀南明和徐英郁安致熙(74)专利代理机构北京鸿元知识产权代理有限公司代理人许向彤(51)Int.CIH05K3/18H05K3/20权利要求说明书说明书幅图(54)发明名称印刷电路板及其制造方法(57)摘要本发明提供一种嵌入式印刷

柔性印刷电路板及其制造方法.pdf

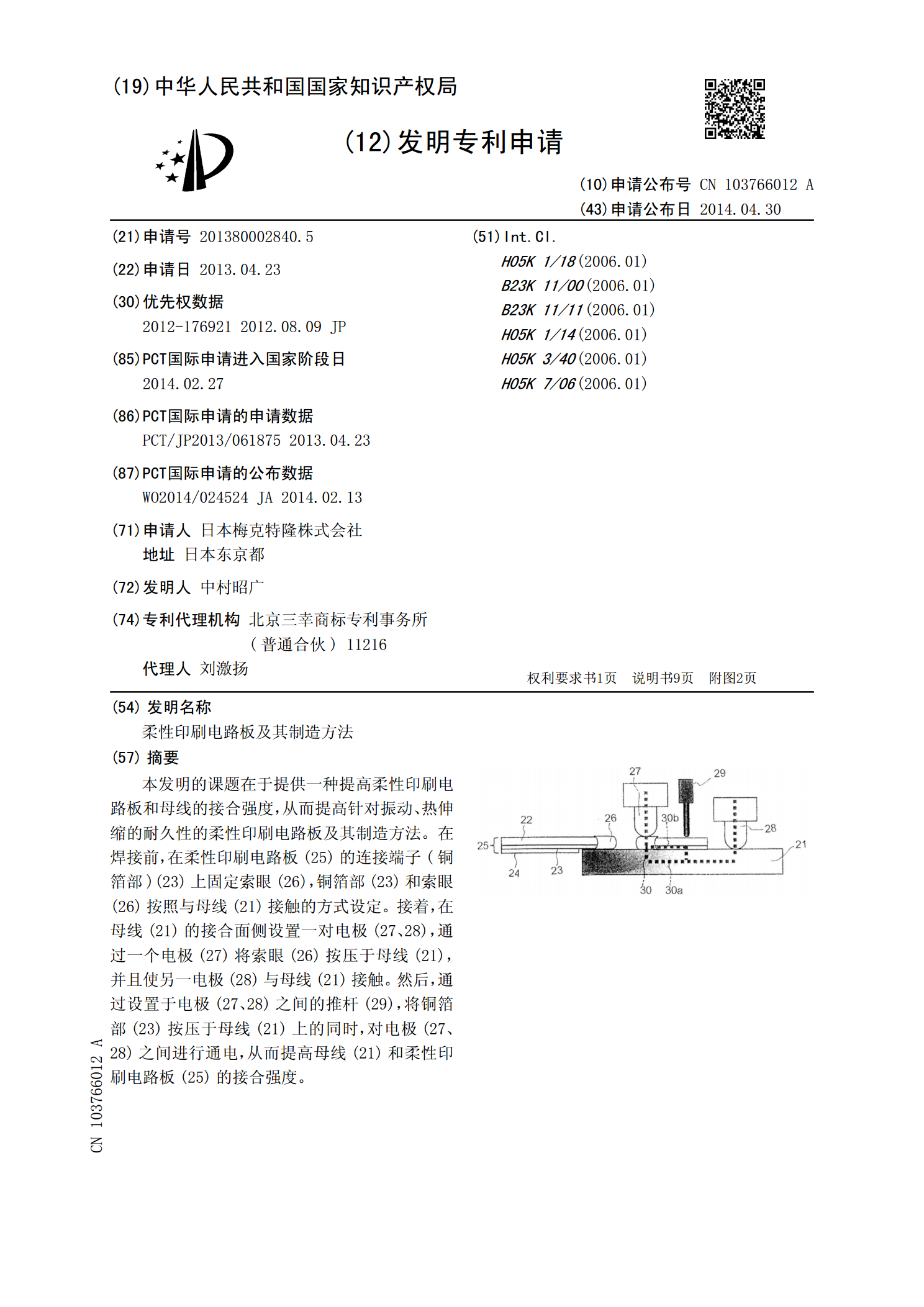

本发明的课题在于提供一种提高柔性印刷电路板和母线的接合强度,从而提高针对振动、热伸缩的耐久性的柔性印刷电路板及其制造方法。在焊接前,在柔性印刷电路板(25)的连接端子(铜箔部)(23)上固定索眼(26),铜箔部(23)和索眼(26)按照与母线(21)接触的方式设定。接着,在母线(21)的接合面侧设置一对电极(27、28),通过一个电极(27)将索眼(26)按压于母线(21),并且使另一电极(28)与母线(21)接触。然后,通过设置于电极(27、28)之间的推杆(29),将铜箔部(23)按压于母线(21)上

柔性印刷电路板及其制造方法.pdf

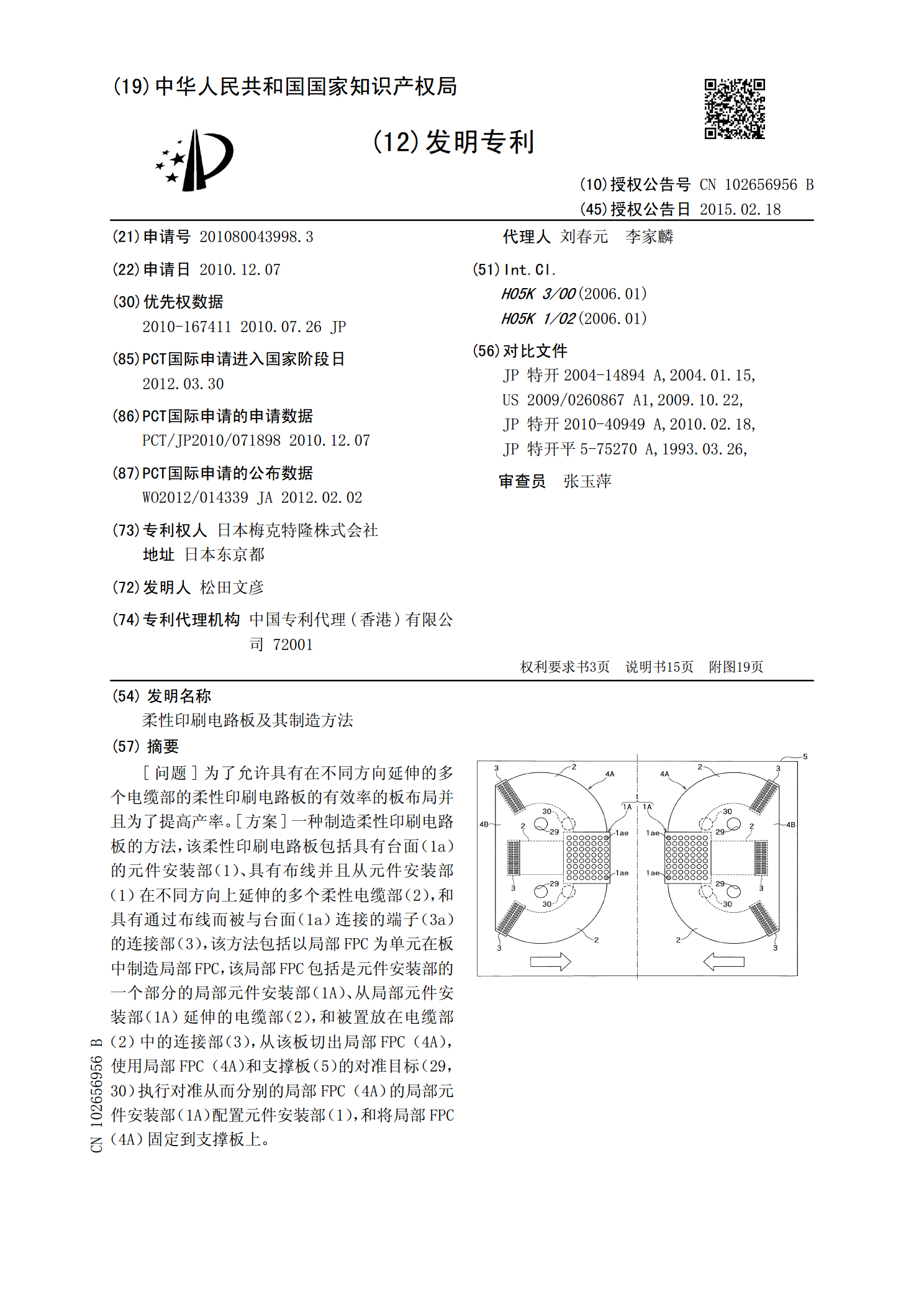

为了允许具有在不同方向延伸的多个电缆部的柔性印刷电路板的有效率的板布局并且为了提高产率。本发明公布了一种制造柔性印刷电路板的方法,该柔性印刷电路板包括具有台面(1a)的元件安装部(1)、具有布线并且从元件安装部(1)在不同方向上延伸的多个柔性电缆部(2),和具有通过布线而被与台面(1a)连接的端子(3a)的连接部(3),该方法包括以局部FPC为单元在板中制造局部FPC,该局部FPC包括是元件安装部的一个部分的局部元件安装部(1A)、从局部元件安装部(1A)延伸的电缆部(2),和被置放在电缆部(2)中的连接

金属基印刷电路板及其制造方法.pdf

本发明涉及一种金属基印刷电路板的制作方法,该方法包括步骤:提供金属基板,对所述金属基板的表面进行粗化处理;提供粘合层和印刷电路板;将所述粘合层和所述印刷电路板依序叠合在所述金属基板的粗化表面;对叠合的金属基板、粘合层和印刷电路板进行热压合,使所述印刷电路板通过所述粘合层粘合在所述金属基板的粗化表面。本发明还提供一种上述方法制得的金属基印刷电路板。本发明金属基印刷电路板及其制作方法具有制作工艺简单、产品散热及机械性能高的优点。

覆铜板、印刷电路板及其制造方法.pdf

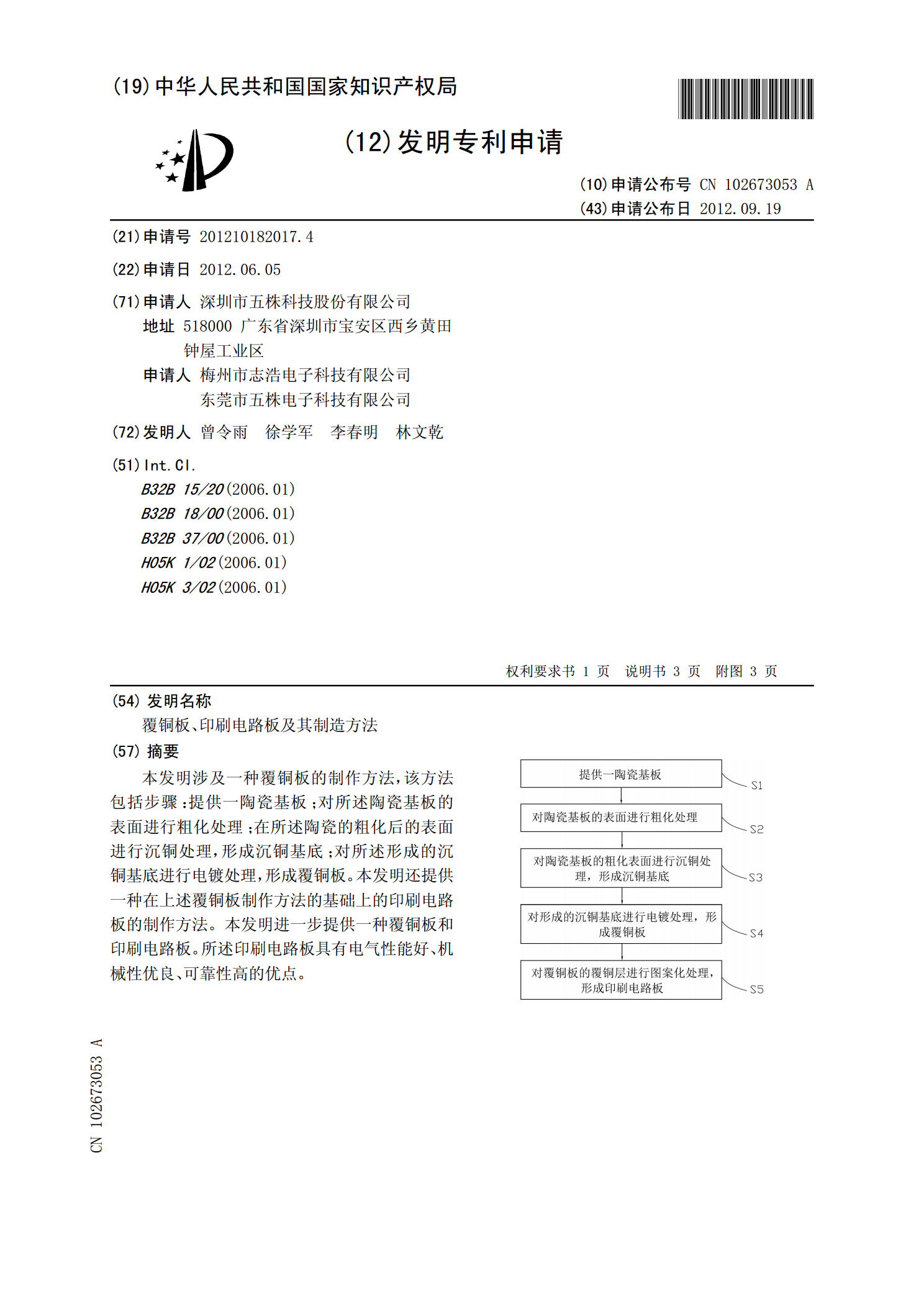

本发明涉及一种覆铜板的制作方法,该方法包括步骤:提供一陶瓷基板;对所述陶瓷基板的表面进行粗化处理;在所述陶瓷的粗化后的表面进行沉铜处理,形成沉铜基底;对所述形成的沉铜基底进行电镀处理,形成覆铜板。本发明还提供一种在上述覆铜板制作方法的基础上的印刷电路板的制作方法。本发明进一步提供一种覆铜板和印刷电路板。所述印刷电路板具有电气性能好、机械性优良、可靠性高的优点。