微机原理与接口技术 ch5存储器.ppt

kp****93

亲,该文档总共49页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

微机原理与接口技术 ch5存储器.ppt

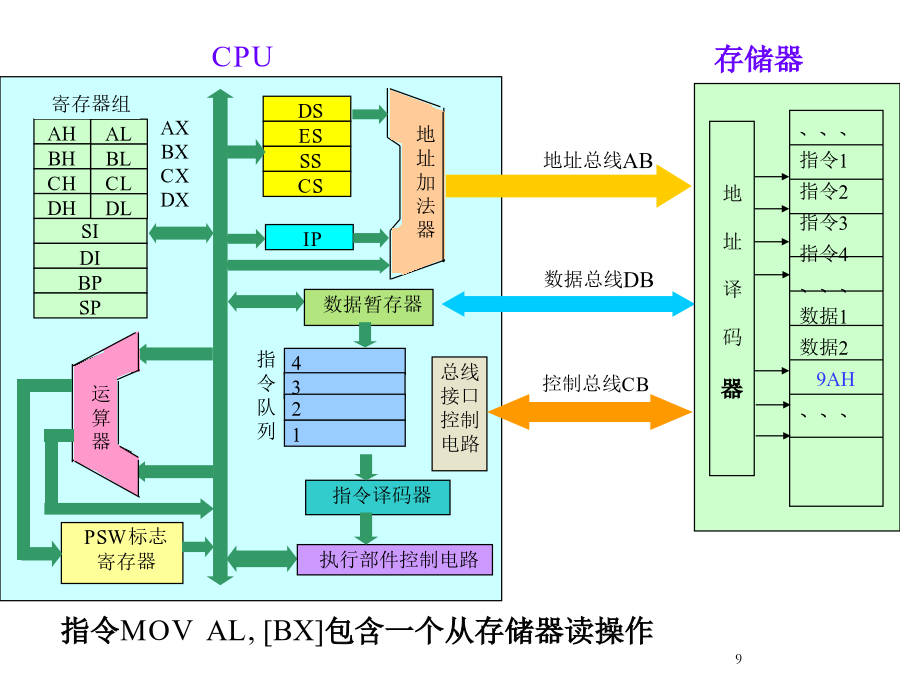

微型计算机原理与应用第五章半导体存储器第五章半导体存储器主要内容学习目标知识点重点难点5.1概述5.1.1存储系统的基本概念DS5.1.2存储器的分类按存放信息原理不同5.1.2存储器的分类5.1.2存储器的分类5.1.3存储器的主要性能指标5.1.4存储器的组成结构静态随机存取存储器SRAM动态随机存取存储器DRAM5.2.1静态随机存取存储器SRAM5.2.1静态随机存取存储器SRAM5.2.1静态随机存取存储器SRAM5.2.2动态随机存取存储器DRAM5.2.2动态随机存取存储器DRAM5.2.2

微机原理与接口技术-存储器.ppt

第一节微型计算机存储器存储器按物理介质不同,可分为磁表面存储器、光盘存储器和半导体存储器三大类二、微型计算机存储器系统主存储器通常安装在主机系统板上,也称为内部存储器。主存储器直接和CPU交换信息,存放当前正在运行中的程序和数据。微型计算机主存储器由半导体存储器RAM和ROM组成,目前装机容量一般在64MB~256MB。三、存储器的主要技术指标第二节半导体存储器一、随机存储器RAM常用的静态RAM(1)静态RAM6116(2)静态RAM62642、动态存储器DRAMDRAM是一种以电荷形式来存储信息的半导

微机原理9微机接口存储器.ppt

第7章半导体存储器及其接口半导体存储器概述存储器的分类1、按存储介质分类半导体存储器、磁表面存储器、光表面存储器2、按存储器的读写功能分类随机存取存储器RAM:可读可写、断电丢失只读存储器ROM:正常只读、断电不丢失3、按用途分类内存储器、外存储器4、按在微机系统中的作用分类主存储器、辅助存储器、高速缓冲存储器5、按制造工艺双极型:速度快、集成度低、功耗大MOS型:速度慢、集成度高、功耗低半导体存储器的分类只读存储器ROM随机读写存储器RAM分类存储器的基本性能指标随机读写存储器:静态RAM(SRAM)基

ch5 存储器与IO接口原理.ppt

2024/8/202024/8/202024/8/202024/8/202024/8/202024/8/202024/8/20只读存储器(ROM)2024/8/202024/8/20存储系统的层次结构2024/8/20静态RAM的结构典型SRAM芯片SRAM工作过程SRAM的读时序SRAM的写时序存储容量的扩展2024/8/202024/8/20动态随机存储器(SDRAM)SDRAM结构SDRAM工作时序SDRAM存储器及其接口2024/8/202024/8/20NANDFlash简介NANDFlash结

微机原理与接口存储器RAM及.pptx

第6章半导体存储器6.1存储器及半导体存储器的分类外存:把通过接口电路与系统相连的存储器称为外存储器,简称外存,如硬盘、软盘和光盘等。特点:存储容量大而存取速度较慢,且掉电数据不丢失。作用:外存用来存放当前暂不被CPU处理的程序或数据,以及一些需要永久性保存的信息。通常将外存归入计算机外部设备,外存中存放的信息必须调入内存后才能被CPU使用。早期的内存使用磁芯。随着大规模集成电路的发展,半导体存储器集成度大大提高,成本迅速下降,存取速度大大加快,所以在微型计算机中,目前内存一般都使用半导体存储器。6.1.