基于PowerPC架构多核处理器嵌入式系统硬件设计.pdf

qw****27

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

基于PowerPC架构多核处理器嵌入式系统硬件设计.pdf

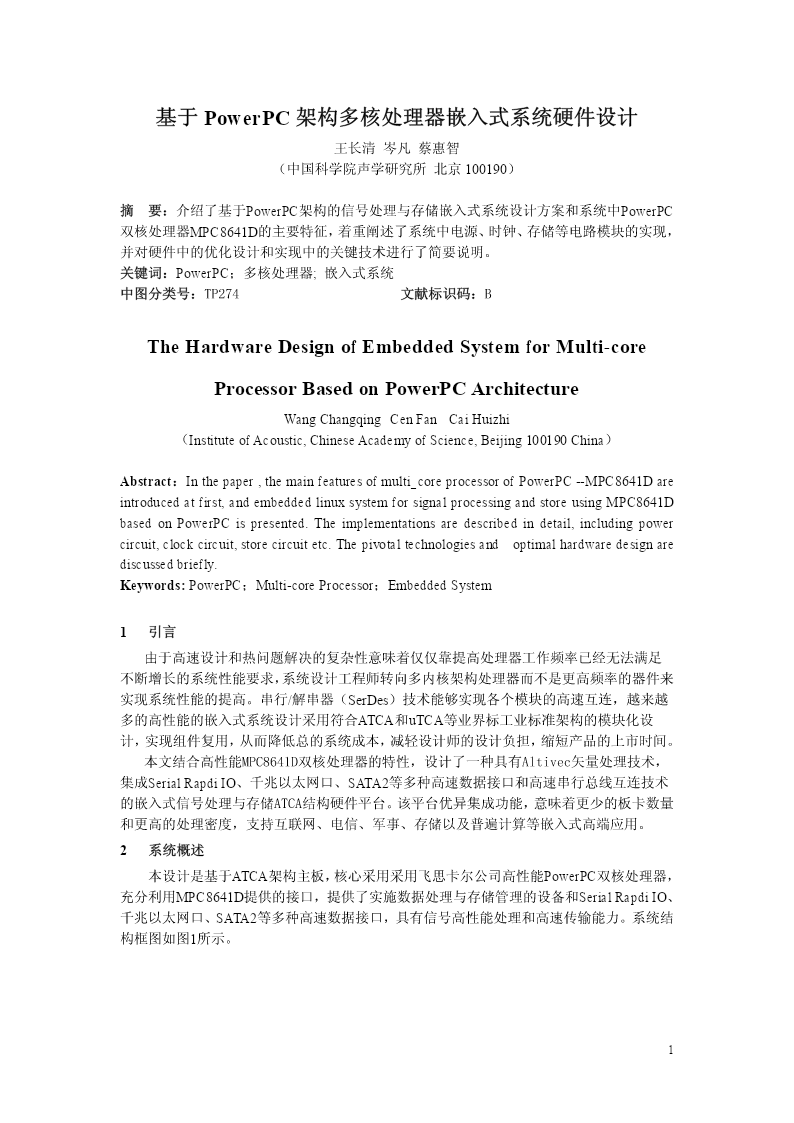

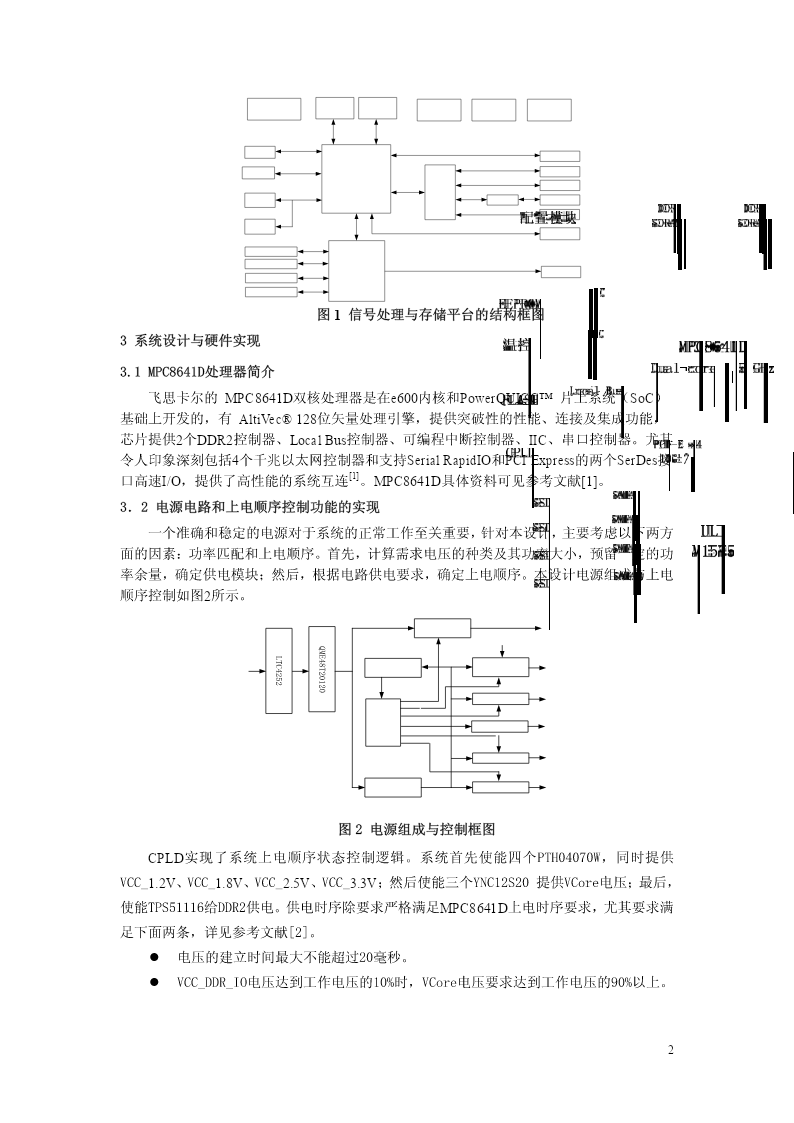

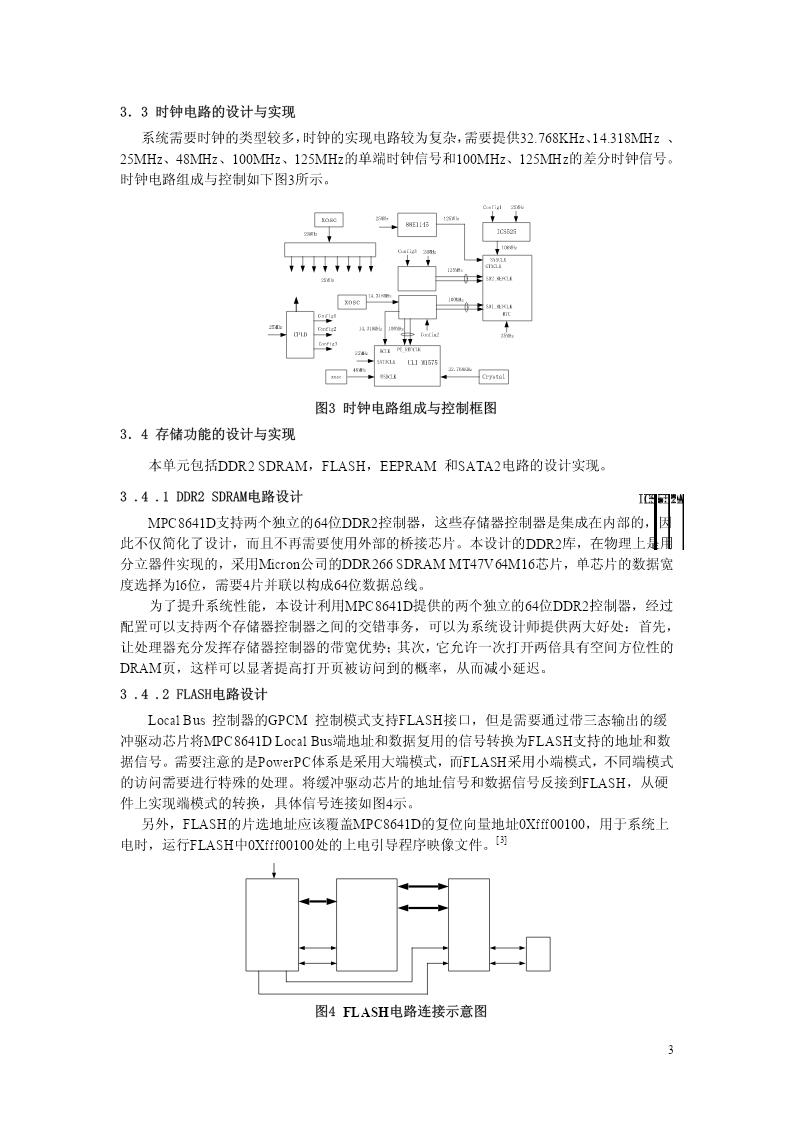

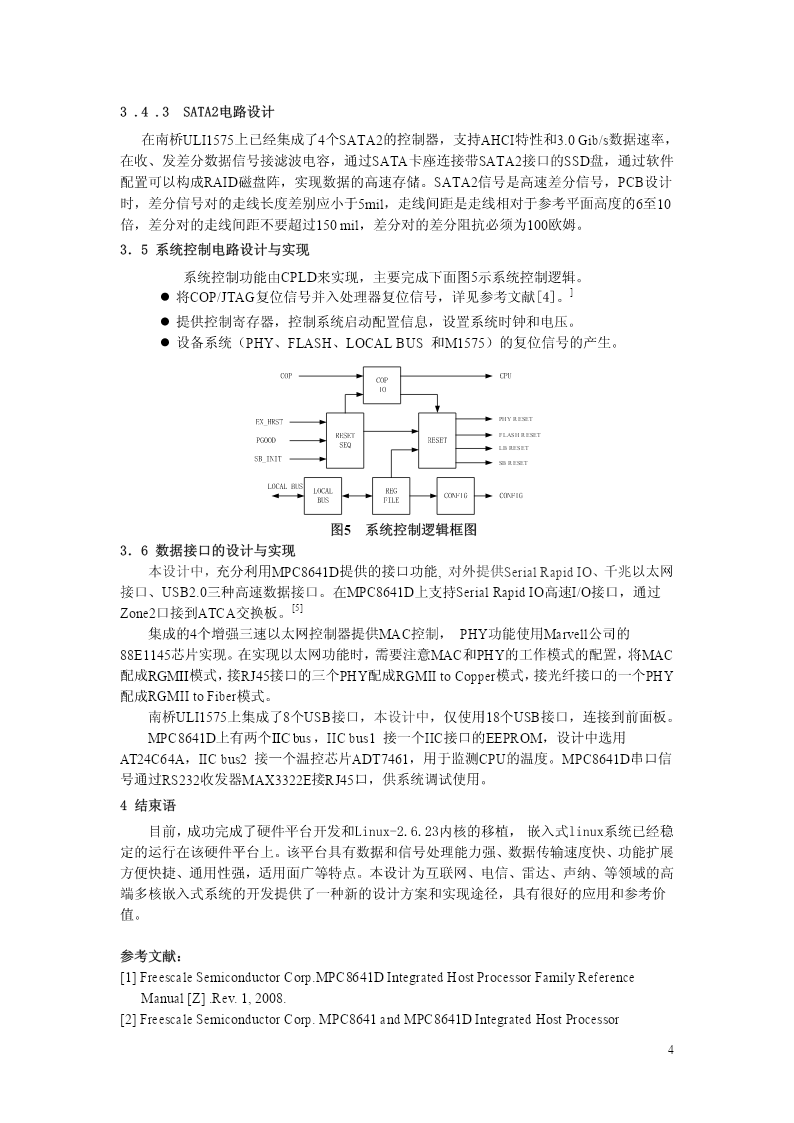

基于PowerPC架构多核处理器嵌入式系统硬件设计王长清岑凡蔡惠智(中国科学院声学研究所北京100190)摘要:介绍了基于PowerPC架构的信号处理与存储嵌入式系统设计方案和系统中PowerPC双核处理器MPC8641D的主要特征,着重阐述了系统中电源、时钟、存储等电路模块的实现,并对硬件中的优化设计和实现中的关键技术进行了简要说明。关键词:PowerPC;多核处理器;嵌入式系统中图分类号:TP274文献标识码:BTheHardwareDesignofEmbeddedSystemforMulti-cor

基于多核架构的图像处理器设计.docx

基于多核架构的图像处理器设计随着科技的不断进步和发展,我们已经进入了一个多核心时代。在这个时代,处理器设计变得越来越重要,它们是许多不同类型的计算机应用程序的重要组成部分。对于基于图像处理的应用程序来说,处理器的设计尤其重要。本文将探讨基于多核架构的图像处理器设计。首先,需要了解图像处理的基本原理。图像处理是对数字图像进行操作的一种方法,其目的是对图像中的信息进行增强或改变。图像处理方法包括图像滤波、图像增强、形态学处理、图像分割、图像变换等。在现代数字媒体和计算机视觉应用中,图像处理技术已经广泛应用于各

基于PowerPC架构的信号处理与存储嵌入式系统设计方案.docx

基于PowerPC架构的信号处理与存储嵌入式系统设计方案基于PowerPC架构的信号处理与存储嵌入式系统设计方案摘要嵌入式系统在现代科技中扮演了重要的角色,它们广泛应用于各种应用场景,如通信、测量、控制等。本文提出了一种基于PowerPC架构的信号处理与存储嵌入式系统设计方案。该方案利用PowerPC架构的高性能和可靠性,结合信号处理和存储技术,实现了高效的数据处理和存储功能。该方案具有较高的可扩展性和灵活性,适用于各种信号处理和存储应用。本文详细介绍了系统的硬件设计和软件开发流程,以及系统的性能评估结果

基于PowerPC的嵌入式系统设计.docx

http://www.cdtarena.com基于PowerPC的嵌入式系统设计随着科学技术的发展,嵌入式处理器在通信设备、消费电子、军用电子等领域有了广泛的应用,而且对处理器的处理速度、功耗及工作温度都有了更加严格的要求,尤其在汽车电子、军用电子等方面的应用。Freescale公司的MlPC5200B是一款紧凑型、低功率的嵌入式处理器,与其他的嵌入式处理器相比具有独特之处,能满足上述的性能要求。MP(25200B集成有高性能的MPC603e内核,该内核采用超标量体系结构,能在400MHz的频率和一40~

基于PowerPC处理器的嵌入式Linux系统构建研究.docx

基于PowerPC处理器的嵌入式Linux系统构建研究随着智能设备的不断普及,嵌入式系统已经成为现代生活中不可或缺的一部分。基于PowerPC处理器的嵌入式Linux系统构建是当前热门的研究领域之一,本篇论文将着重探讨这个问题的背景、原理和实现。I.嵌入式系统概述嵌入式系统是一种特殊的计算机系统,通常被嵌入到其他设备中以执行特定任务。与桌面计算机或服务器不同,嵌入式系统的硬件资源和软件资源都严格限制。嵌入式系统常常要求具有低功耗、小体积、高性能和高可靠性等特性,因此在设计和实现时需要充分考虑这些方面的问题