数码管译码芯片驱动和单片机IO口介绍.docx

kp****93

亲,该文档总共15页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

数码管译码芯片驱动和单片机IO口介绍.docx

8051引脚现在我们介绍8051单片机引脚及功能,8051系列各种芯片的引脚是相互兼容的,8051、8751、8031引脚均40脚双列直插封装形式。当然,不同芯片之间引脚也略有差异。8051单片机是高性能单片机,因受到引脚数目限制,所以不少引脚具有第二功能,各引脚功能简要说明如下:VCC(40脚)电源端+5VVSS(20脚)接地端365小站制作时钟电路引脚XTAL2(18引脚)接外部晶体和微调电容。在8051片内它是振荡电路反相放大器的输出端,振荡电路的频率就是晶体固有频率。若需要采用外部时钟电路时,该引

IO驱动电路及芯片.pdf

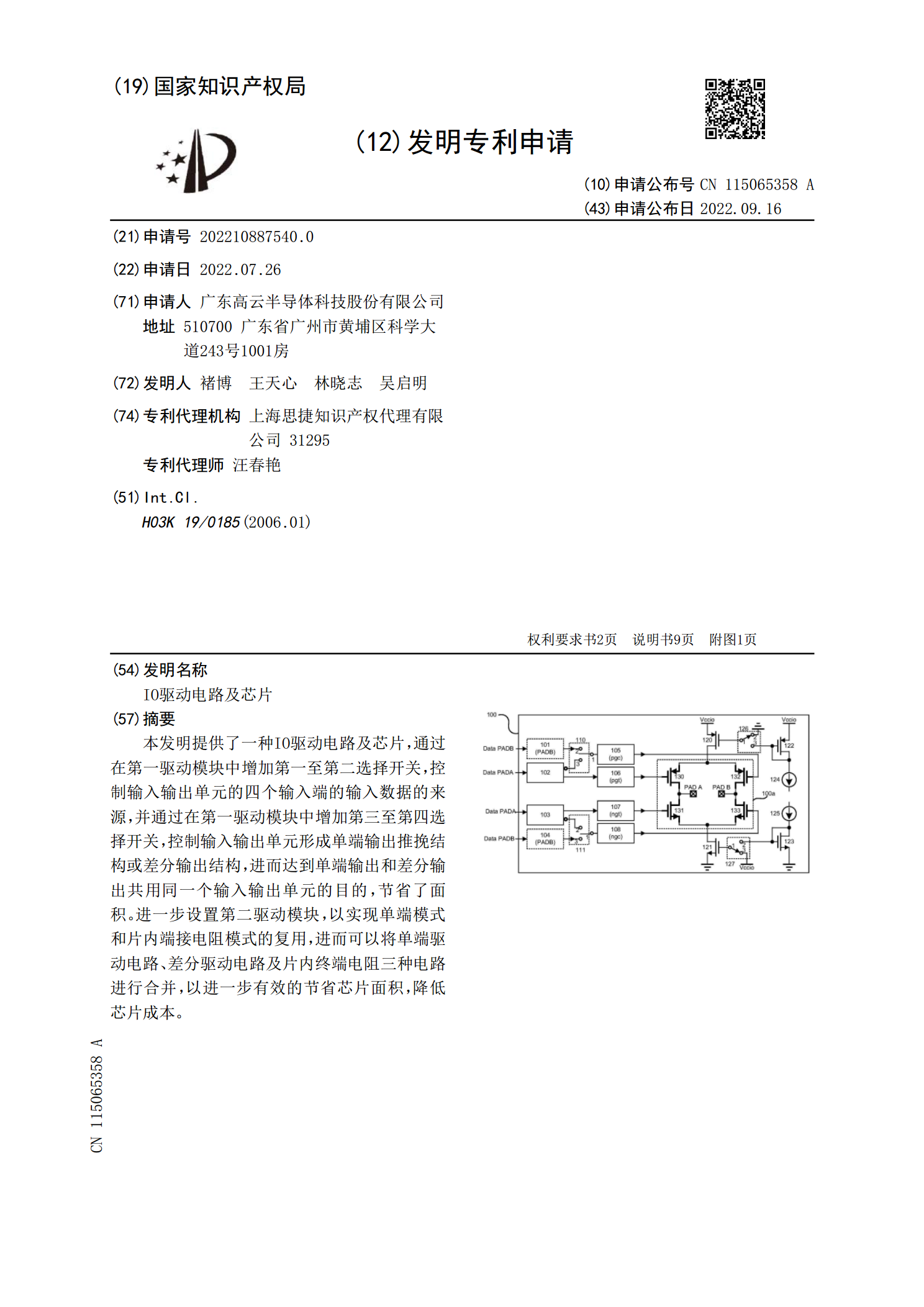

本发明提供了一种IO驱动电路及芯片,通过在第一驱动模块中增加第一至第二选择开关,控制输入输出单元的四个输入端的输入数据的来源,并通过在第一驱动模块中增加第三至第四选择开关,控制输入输出单元形成单端输出推挽结构或差分输出结构,进而达到单端输出和差分输出共用同一个输入输出单元的目的,节省了面积。进一步设置第二驱动模块,以实现单端模式和片内端接电阻模式的复用,进而可以将单端驱动电路、差分驱动电路及片内终端电阻三种电路进行合并,以进一步有效的节省芯片面积,降低芯片成本。

数码管驱动芯片汇总.doc

原来用:PT6965一:TM1638价钱:元/一只、元/一只2、封装:SOP283、连接CPU:DIO、STB、CLK二:PT69641、价钱:元/一只、元/一只、元/一只2、封装:SOP283、连接CPU:DIO、STB、CLK三:ETK62011、价钱:元/一只、元/一只2、封装:SOP283、连接CPU:OSC、STB、CLK、DOUT、DIN四:HT16K331、价钱:20sop:24sop:28sop:、2封装:SOP20、SOP24、SOP28五:

用单片机IO口直接驱动段式LCD的方法.doc

用单片机IO口直接驱动段式LCD的方法用IO口驱动段式LED(数码管)的方法相信大家比较清楚,但用IO口直接驱动段式LCD的方法相对复杂一些。在网上搜了一下单片机IO口驱动段式LCD的方法,大部分资料讲得不够清晰、具体,而且简单问题复杂化。后来查了LCD的显示原理,结合网上的相关介绍,发现IO口直接驱动段式LCD原理比较简单,用几句话就可以描述清楚:1.LCD和LED的显示原理不一样:LED是加正向电压发光,而LCD必须交替加正、反向电压才会持续显示(可以做个实验,如果把恒定电压加到LCD的一段上,该段会

51单片机IO口介绍ppt课件.ppt

第一讲什么是单片机?单片机能做什么?学单片机需要什么基础?与以前所学的知识关联很少;只需要掌握很基本的数电模电知识;对各种器件的概念基本上是从0开始;如果要用C语言编程,需具备简单的C语言基础;所有人都站在了同一起跑线上;几点预备知识◆单板机将CPU芯片、存储器芯片、I/O接口芯片和简单的I/O设备(小键盘、LED显示器)等装配在一块印刷电路板上,再配上监控程序(固化在ROM中),就构成了一台单板微型计算机(简称单板机)。单板机的I/O设备简单,软件资源少,使用不方便。早期主要用于微型计算机原理的教学及简