第4章存储器和高速缓存技术.ppt

kp****93

亲,该文档总共98页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

第4章存储器和高速缓存技术.ppt

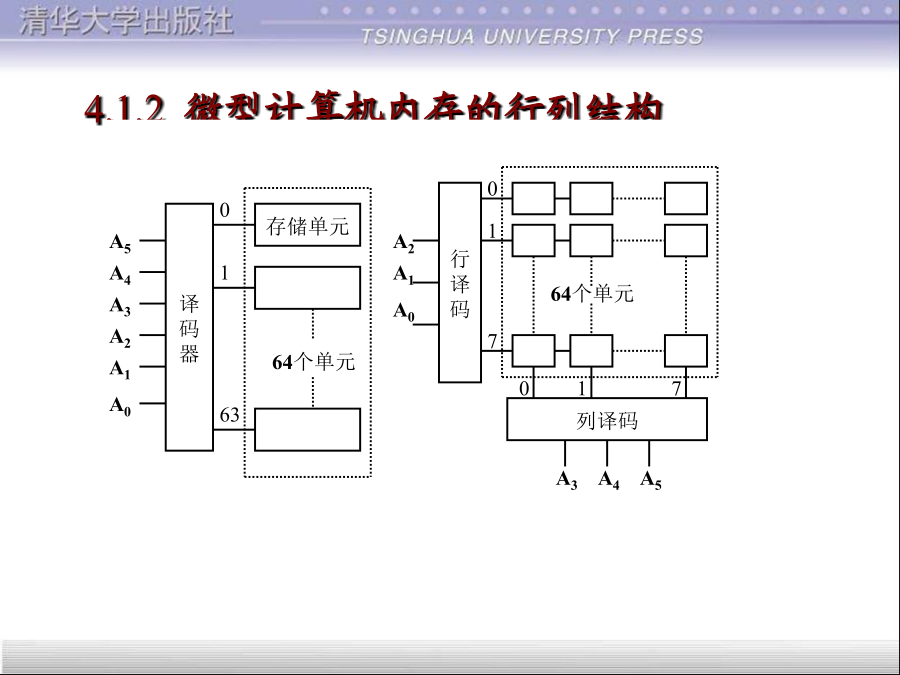

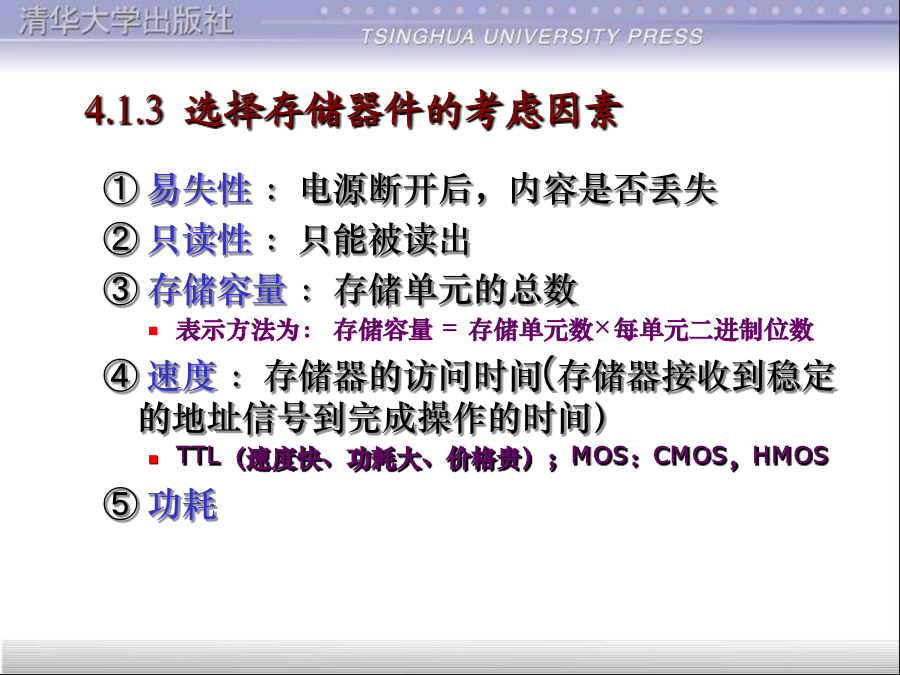

第4章存储器、存储管理和高速缓存技术本章重点:第4章存储器、存储管理和高速缓存技术4.1存储器和存储器件4.1.1存储器的分类4.1.2微型计算机内存的行列结构4.1.2微型计算机内存的行列结构图4.132行×32列组成的矩阵和外部的连接4.1.3选择存储器件的考虑因素4.1.4随机存取存储器RAMSRAM基本存储电路DRAM基本存储电路图4.2DRAM控制器的原理图4.1.5只读存储器ROMROM的分类:1.掩膜ROM2.可编程只读存储器PROM3.EPROM图4.3Intel2764EPROM的外形和

存储器跟高速缓存技术.ppt

第4章存储器和高速缓存技术4.1存储器和存储器件4.1.1存储器的分类4.1.2微型计算机内存的行列结构32行×32列组成的矩阵和外部的连接:4.1.3选择存储器件的考虑因素4.1.4随机存取存储器RAMDRAM控制器的原理图4.1.5只读存储器ROMROM的分类闪烁存储器的特点:闪烁存储器的分类:闪烁存储器的命令:4.1.6存储器在系统中的连接考虑和使用举例存储器芯片片选信号的构成方法:2.SRAM的使用举例3.DRAM和DRAM控制器的使用举例4.1.7存储器的数据宽度扩充和字节数扩充扩充存储器的数据

存储器高速缓存管理.pdf

本文中描述了用于管理非易失性存储装置中的IS内存的技术及与其一起使用的方法。所述非易失性存储装置可包含非易失性内存,其中所述非易失性内存的一部分被指定为中间存储器(IS)内存且所述非易失性内存的另一部分被指定为主存储器(MS)内存。所述IS内存可具有比所述MS内存更低的读取及写入时延。主机装置可在具有优先级地址中的一个的主机数据接收优先级以优先于其它主机数据保留在IS内存中的指示下将优先级地址提供到内存控制器。

高速缓存存储器访问.pdf

多处理器数据处理系统包括支持多个处理器内核的多个垂直高速缓存层级结构、系统存储器和系统互连。响应于来自第一处理器内核的加载‑和‑保留请求,支持第一处理器内核的第一高速缓存存储器在系统互连上发布对加载‑和‑保留请求的目标高速缓存行的存储器访问请求。响应于存储器访问请求并且在接收对于存储器访问请求的系统范围的一致性响应之前,第一高速缓存存储器通过高速缓存‑到‑高速缓存干预从第二垂直高速缓存层级结构中的第二高速缓存存储器接收目标高速缓存行以及对存储器访问请求的系统范围的一致性响应的早期指示。响应于早期指示并在接

存储器感知预取和高速缓存旁路系统和方法.pdf

描述了与存储器管理相关的系统、设备和方法。举例来说,这些可包含:第一存储器层级,其包含存储器阵列(28)中的存储器页;第二存储器层级,其包含高速缓存(24)、预取缓冲器(32)或这两者;以及存储器控制器(34),其确定与所述存储器阵列(28)中由存储器存取请求定为目标的存储器页相关联的状态信息。所述状态信息可包含指示所述存储器页的当前激活状态的第一参数,以及指示后续存储器存取请求将所述存储器页定为目标的统计似然度(例如,置信度)的第二参数。当与所述存储器页相关联的所述第一参数指示所述存储器页被激活且与所述