存储器装置及其写入方法.pdf

淑然****by

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

存储器装置及其写入方法.pdf

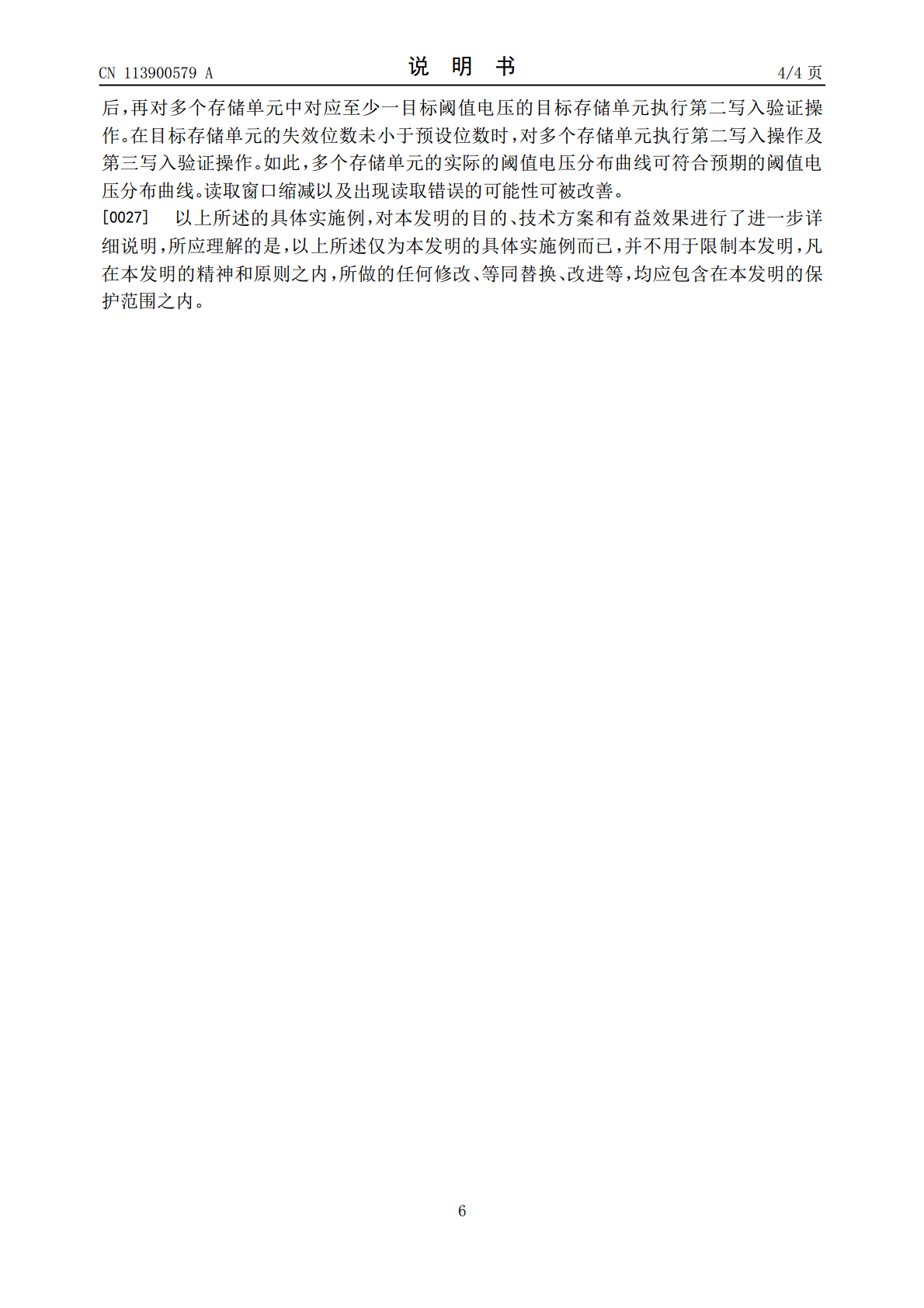

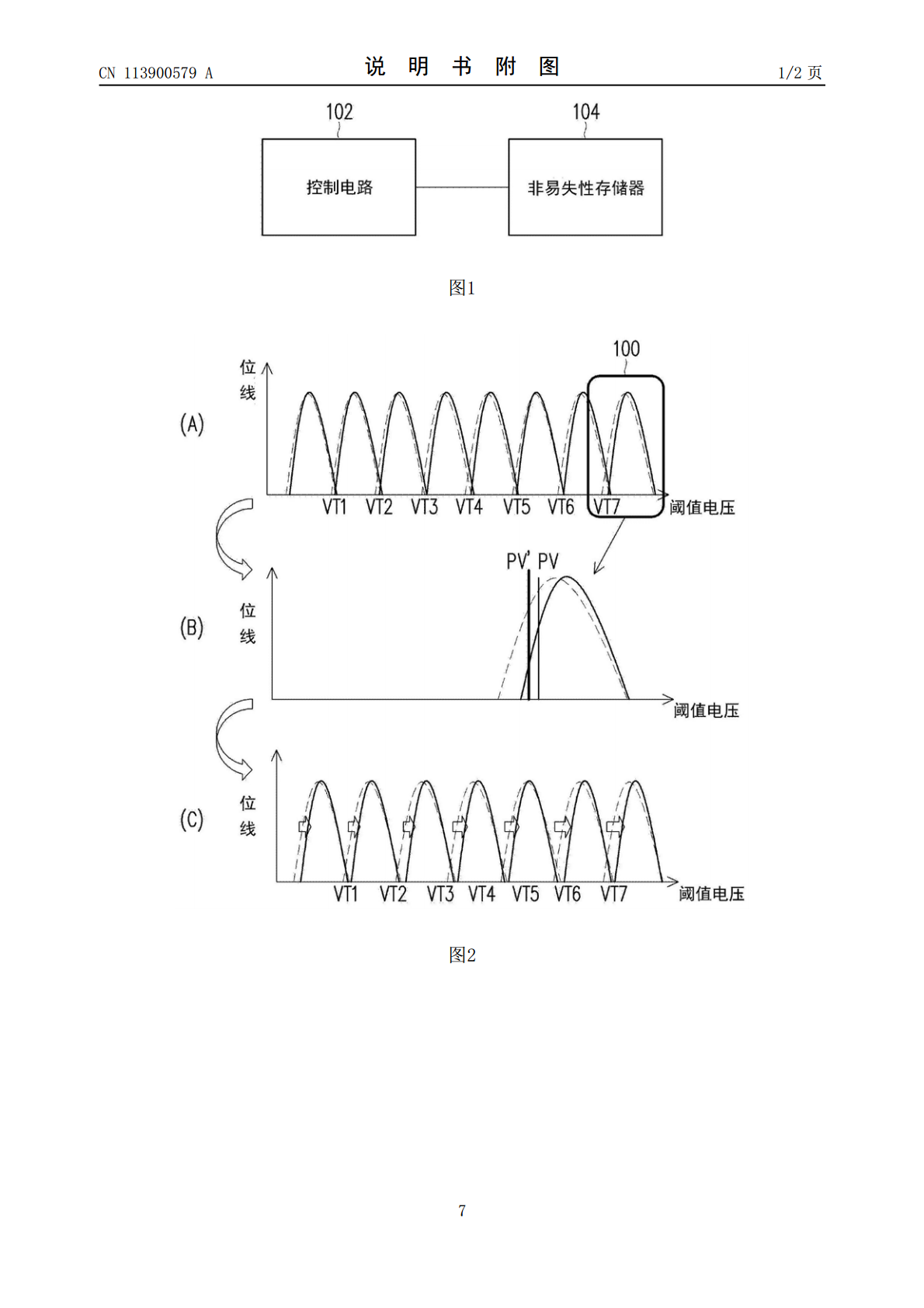

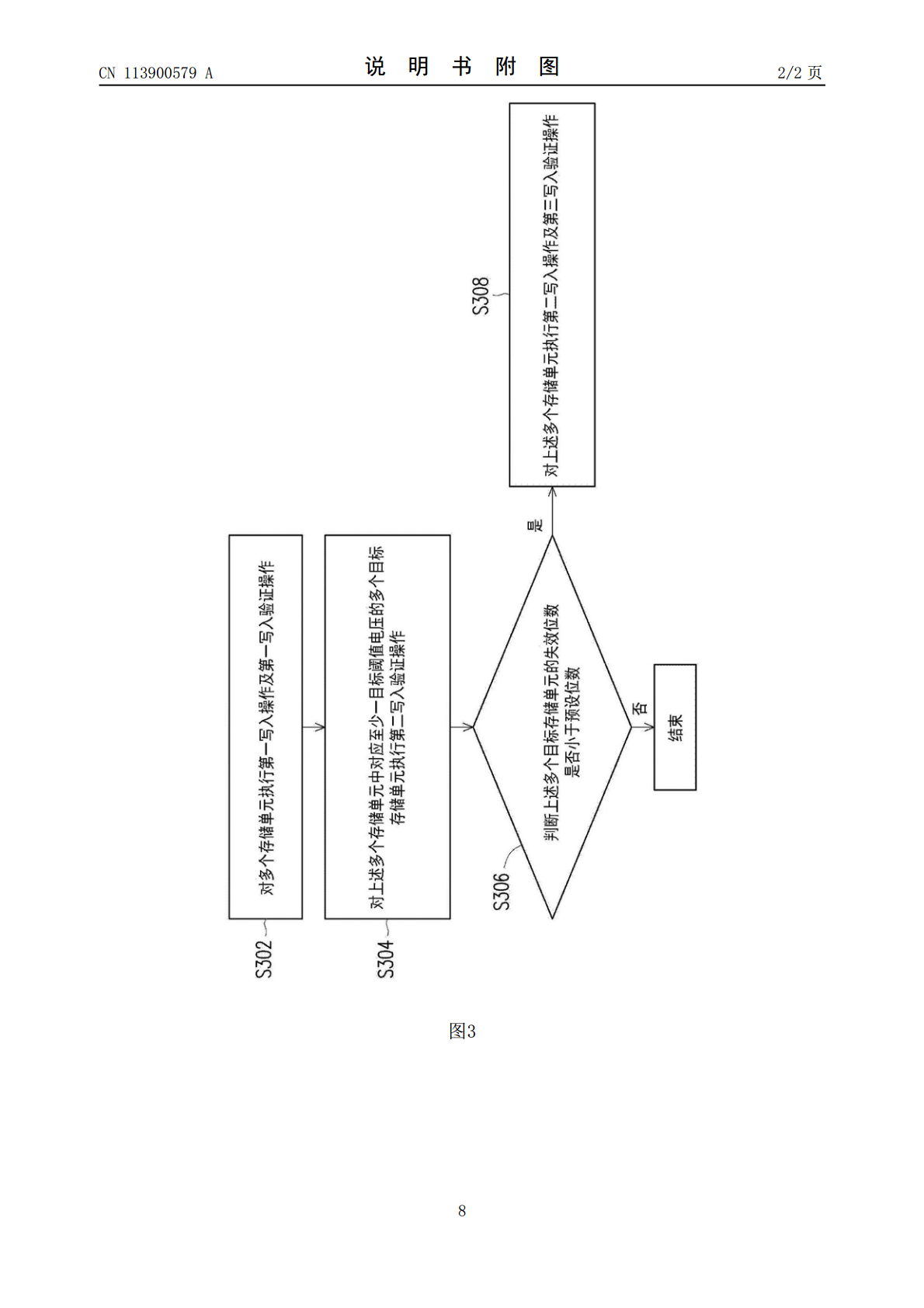

本发明公开了一种存储器装置及其写入方法。控制电路对非易失性存储器的多个存储单元执行第一写入操作及第一写入验证操作,于上述多个存储单元通过第一写入验证操作后,对上述多个存储单元中对应至少一目标阈值电压的多个目标存储单元执行第二写入验证操作,于上述多个目标存储单元的失效位数未小于预设位数时,对上述多个存储单元执行第二写入操作及第三写入验证操作。

用于写入数据的电阻式存储器装置及其操作方法.pdf

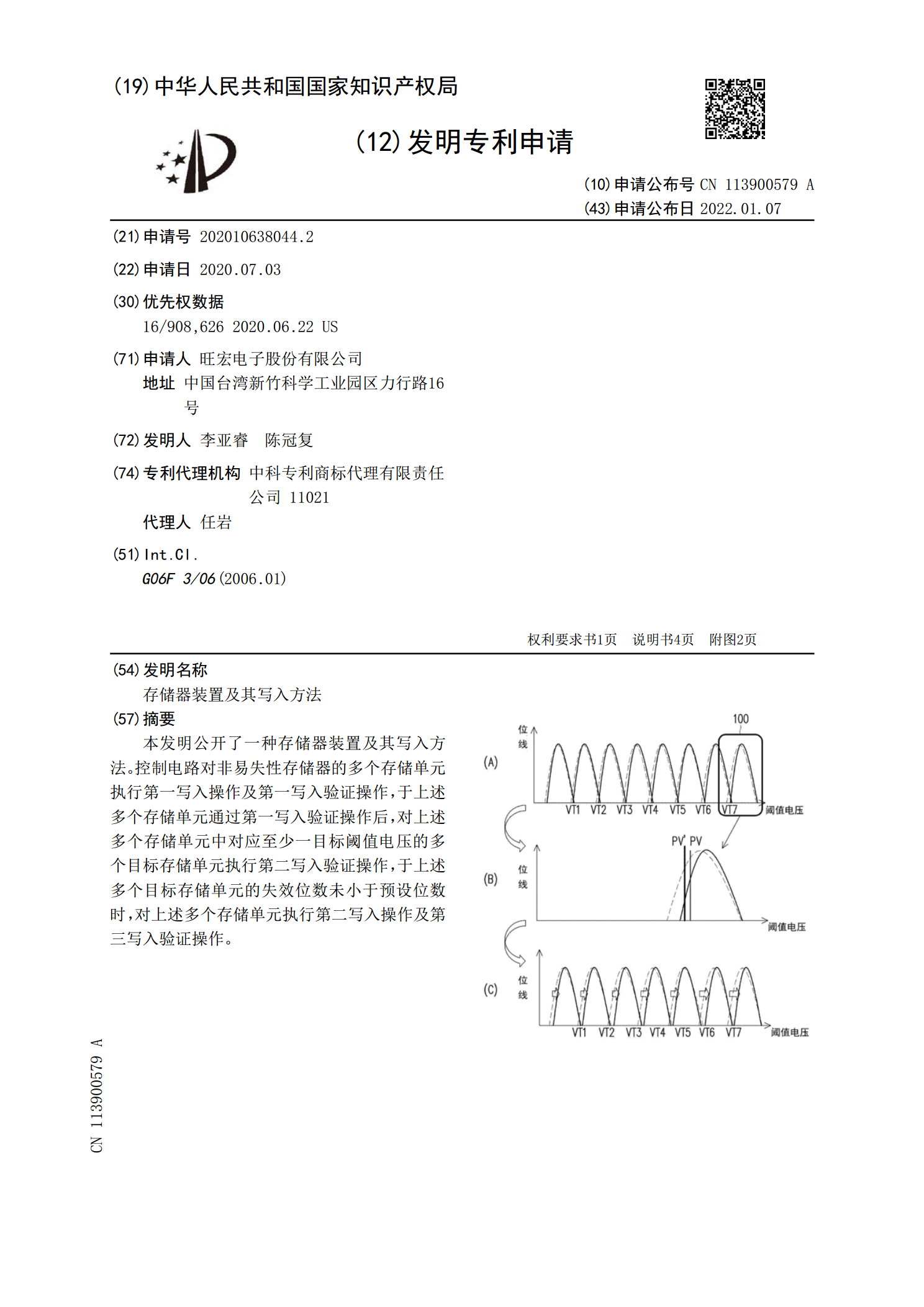

提供了用于写入数据的电阻式存储器装置及其操作方法。所述电阻式存储器装置包括:电阻式单元,连接在第一位线与第一源极线之间;参考单元,包括参考电阻器,并且连接在第二位线与第二源极线之间;以及写入驱动器,可切换地连接到第一位线或第一源极线,可切换地连接到第二位线或第二源极线。写入驱动器包括比较器,比较器被配置为:通过将第一源极线的电压与第二源极线的电压进行比较或将第一位线的电压与第二位线的电压进行比较来将已写入电阻式单元中的先前数据与目标数据进行比较,并且在将先前数据与目标数据进行比较之后确定目标数据是否被写入

Flash存储器的数据写入方法、读取方法和装置.pdf

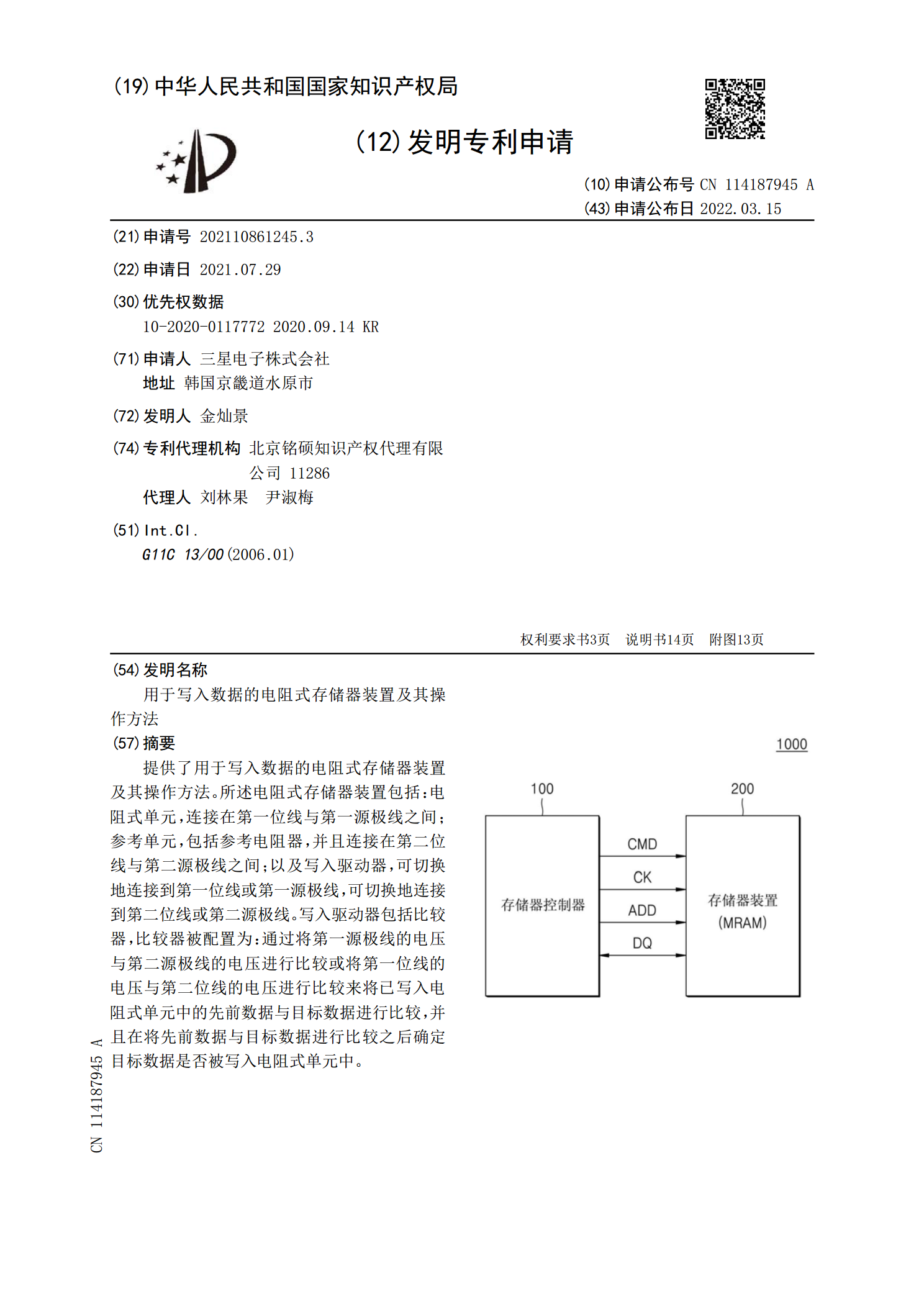

本发明公开了一种Flash存储器的数据写入方法、读取方法和装置。该方法包括以下步骤:步骤S1,读取第一目标页的数据;步骤S2,根据包含的第一信息,确定第一目标页是否被写入过:若第一目标页未被写入过,则将第一目标页的前一页确定为第一目标页,跳转到步骤S1;若第一目标页被写入过,则执行步骤S3;步骤S3,根据第一目标页的数据和要写入的数据,确定写入页;步骤S4,向写入页写入要写入的数据。本发明能够通过标志信息找出未被写入的空白页,每次写入都将数据写在相邻的空白页上,能够充分利用扇区中的页,减少了擦除的次数,提

数据写入方法、存储器控制器与存储器储存装置.pdf

本发明提供一种数据写入方法、存储器控制器与存储器储存装置。此方法用于控制可复写式非易失性存储器模块,其包括两个存储单元。此方法包括:配置多个逻辑地址以映射至上述两个存储单元中至少部分的实体擦除单元;接收来自主机系统的写入指令,其指示将数据写入至一个上述的逻辑地址;将此数据写入至上述两个存储单元中的一个实体擦除单元;判断此实体擦除单元是属于哪一个存储单元;以及若此实体擦除单元属于其中一个存储单元,将数据写入时,擦除另一个存储单元中的一个实体擦除单元。因此,可以增加主机系统写入数据至存储器储存装置的速度。

带存储装置、及其写入方法.pdf

本发明提供小事务的带写入方法。对于固定长度的数据集,(步骤1)将第1文件作为多个DS向带写入;将最后的DS的DS编号作为#N(DS#N)和将WP编号作为#M(WP#M)保管;(步骤2)对包括第1文件的上述最后的DS(DS#N,WP#M)的后续的DS,填入上述最后的第1文件及第2文件,并依次以DS为单位向带写入;对包括第2文件的上述DS按顺序作为DS#N,DS#N+1…及WP#M+1在存储器中保管。(步骤3)填入残留的第1、第2、或第3文件,以WP#M+2以DS#N,复写WP#M的DS#N;第2文件及第3文