一种FMCW激光测距光源非线性校正系统和方法.pdf

书生****35

亲,该文档总共19页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种FMCW激光测距光源非线性校正系统和方法.pdf

本发明公开了一种FMCW激光测距光源非线性校正系统和方法,属于激光雷达、激光测距、激光三维扫描等领域,解决现有技术无法准确提取目标位置,从而影响对目标的探测识别等问题。本发明首先初始化半导体激光器LD、SOA和FPGA;再对经过SOA放大的锯齿波或三角波光源信号使用光电探测器PD进行采集并传输到FPGA主控单元进行处理,处理后输出功率反馈控制信号到SOA驱动控制器;对经过系统中的马赫‑增德尔干涉仪产生的拍频信号使用PD进行采集并传输到FPGA主控单元进行处理,处理后输出迭代后的锯齿波或三角波调制信号对LD

一种调频连续波干涉激光光源非线性校正方法.pptx

汇报人:CONTENTS调频连续波干涉激光光源非线性校正方法概述调频连续波干涉激光光源的原理非线性校正的必要性校正方法的基本思路调频连续波干涉激光光源非线性校正方法的具体步骤采集干涉图计算干涉图相位差构建非线性校正模型实施非线性校正调频连续波干涉激光光源非线性校正方法的效果评估校正前后的干涉图对比校正前后相位差的变化校正后激光光源性能的提升调频连续波干涉激光光源非线性校正方法的优势与局限性优势分析局限性分析改进方向调频连续波干涉激光光源非线性校正方法的应用前景在光学测量领域的应用在激光雷达系统中的应用在量

一种激光测距方法、对焦方法、激光测距系统及对焦系统.pdf

本发明涉及测距领域,公开了一种激光测距方法、对焦方法、激光测距系统及对焦系统,包括:向反射镜发射入射角为δ的入射光线α,入射光线α经反射镜反射产生第一反射光线β,第一反射光线β照射待测物体;摄取第二反射光线θ并在激光成像面生成激光图像,第二反射光线θ为第一反射光线β照射于待测物体表面后产生的返回光线γ,再通过反射镜反射产生;基于激光图像根据几何三角定理计算测量距离A。以入射光线α的发射点和第二反射光线θ的接收点的连线L为底边,以入射光线α与第二反射光线θ延长线的相交角为顶角构成的三角形的底边的高与测量距离

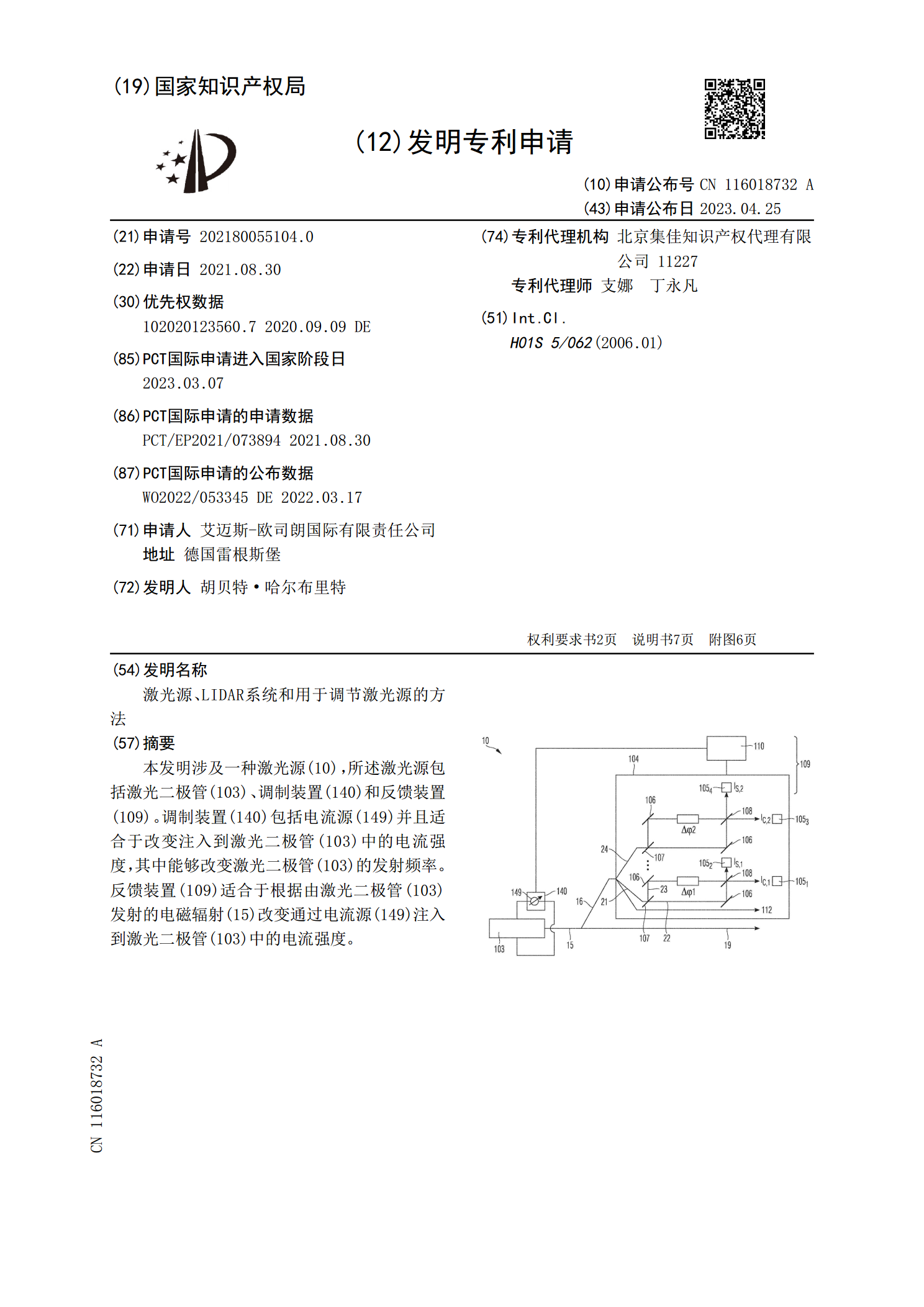

激光源、LIDAR系统和用于调节激光源的方法.pdf

本发明涉及一种激光源(10),所述激光源包括激光二极管(103)、调制装置(140)和反馈装置(109)。调制装置(140)包括电流源(149)并且适合于改变注入到激光二极管(103)中的电流强度,其中能够改变激光二极管(103)的发射频率。反馈装置(109)适合于根据由激光二极管(103)发射的电磁辐射(15)改变通过电流源(149)注入到激光二极管(103)中的电流强度。

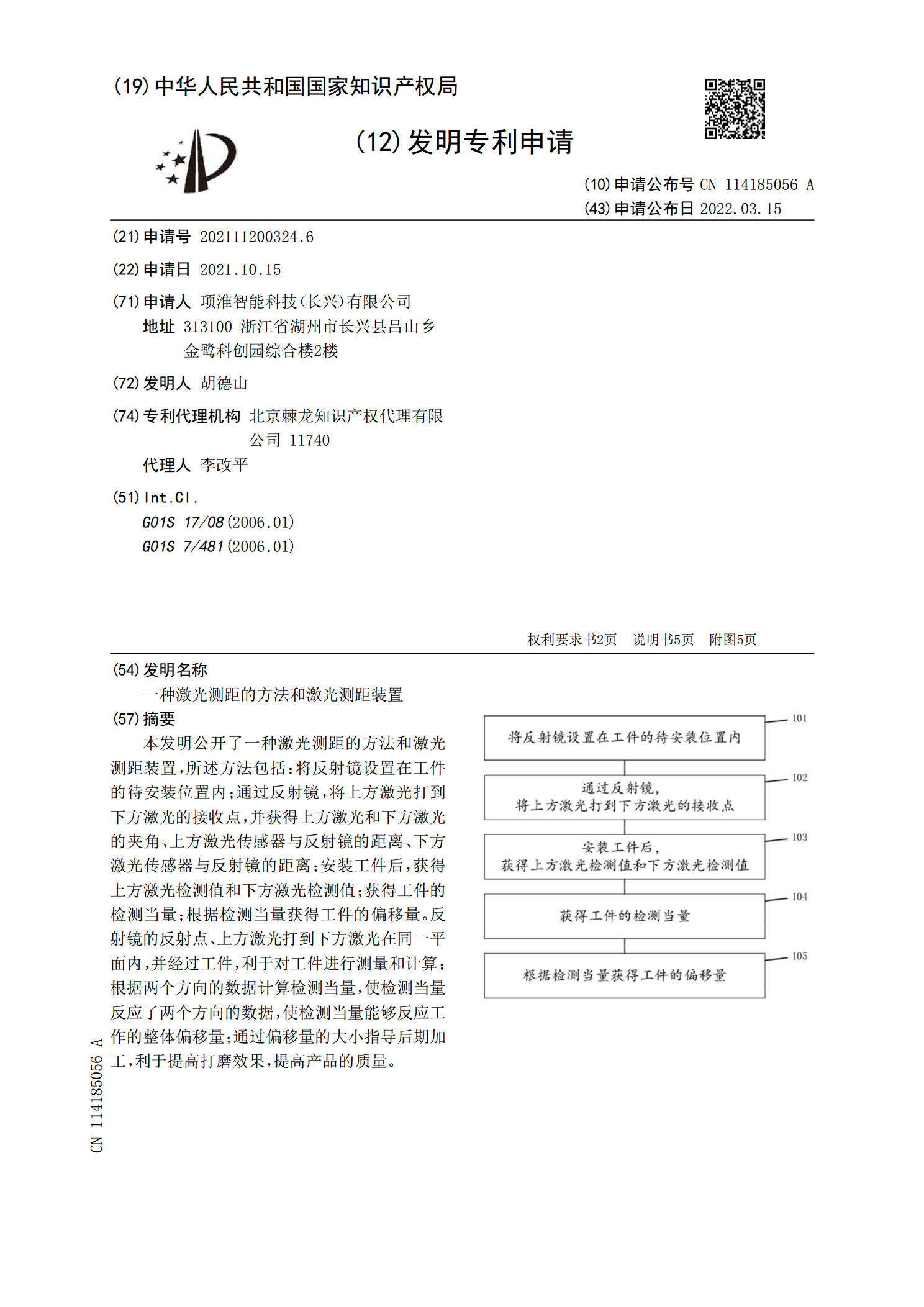

一种激光测距的方法和激光测距装置.pdf

本发明公开了一种激光测距的方法和激光测距装置,所述方法包括:将反射镜设置在工件的待安装位置内;通过反射镜,将上方激光打到下方激光的接收点,并获得上方激光和下方激光的夹角、上方激光传感器与反射镜的距离、下方激光传感器与反射镜的距离;安装工件后,获得上方激光检测值和下方激光检测值;获得工件的检测当量;根据检测当量获得工件的偏移量。反射镜的反射点、上方激光打到下方激光在同一平面内,并经过工件,利于对工件进行测量和计算;根据两个方向的数据计算检测当量,使检测当量反应了两个方向的数据,使检测当量能够反应工作的整体偏