芯片的模块引脚布线方法、装置、电子设备及存储介质.pdf

绮兰****文章

亲,该文档总共20页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

芯片的模块引脚布线方法、装置、电子设备及存储介质.pdf

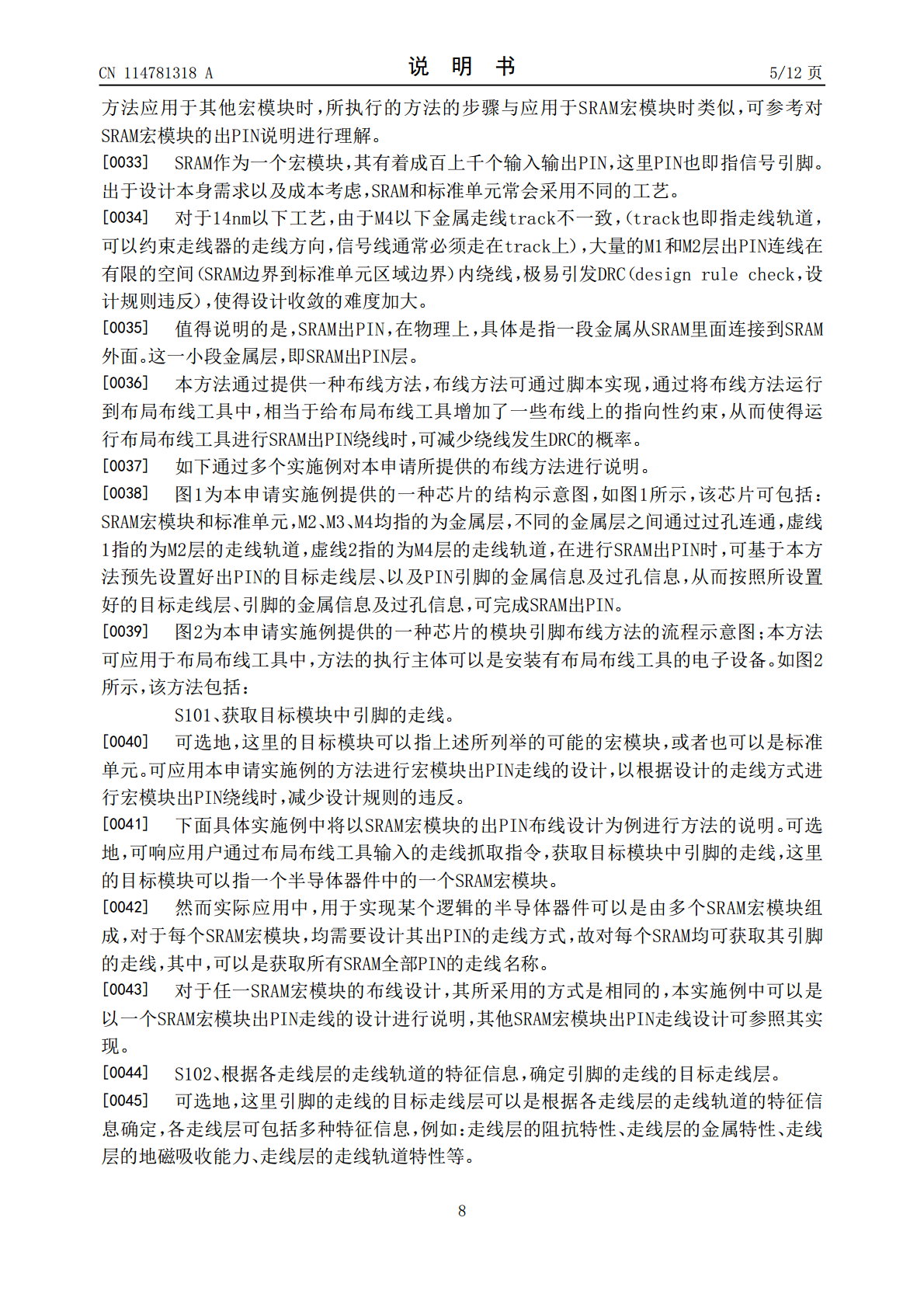

本申请提供一种芯片的模块引脚布线方法、装置、电子设备及存储介质,涉及芯片技术领域。该方法包括:获取目标模块中引脚的走线;根据各走线层的走线轨道的特征信息,确定引脚的走线的目标走线层;按照目标走线层、引脚金属信息以及引脚过孔信息,生成引脚的走线的实际布线结果;根据实际布线结果的验证结果,确定目标模块的目标布线结果。本方法通过宏模块和标准单元在各层的走线轨道的特性确定目标走线层,以使得SRAM出PIN绕线时按照目标走线层进行绕线时,由于在目标走线层,SRAM宏模块和标准单元的走线轨道是一致的,从而以目标走线层

一种芯片布线设计方法、装置、存储介质及电子设备.pdf

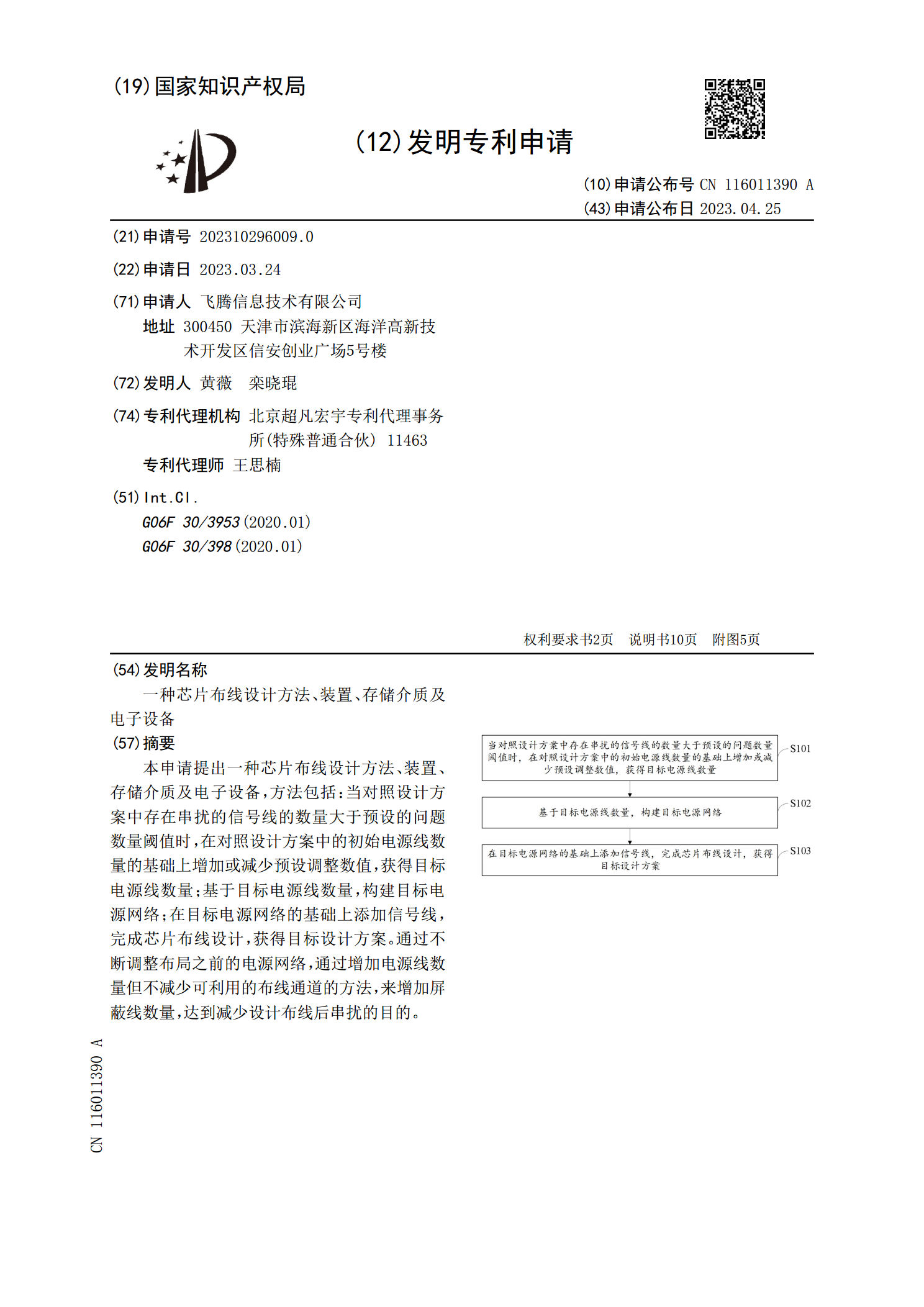

本申请提出一种芯片布线设计方法、装置、存储介质及电子设备,方法包括:当对照设计方案中存在串扰的信号线的数量大于预设的问题数量阈值时,在对照设计方案中的初始电源线数量的基础上增加或减少预设调整数值,获得目标电源线数量;基于目标电源线数量,构建目标电源网络;在目标电源网络的基础上添加信号线,完成芯片布线设计,获得目标设计方案。通过不断调整布局之前的电源网络,通过增加电源线数量但不减少可利用的布线通道的方法,来增加屏蔽线数量,达到减少设计布线后串扰的目的。

芯片、引脚操作方法、可读存储介质和电子设备.pdf

本发明实施例提供了一种芯片、引脚操作方法、存储介质和设备,涉及电子技术领域,芯片包括控制器和GPIO引脚,以及与目标GPIO引脚对应的第一输出寄存器,第一输出寄存器中的第一目标位与目标GPIO引脚连接,并且第一输出寄存器未连接除目标GPIO引脚之外的其他GPIO引脚;控制器与第一输出寄存器连接,用于在获取到控制目标GPIO引脚的位数据的情况下,若位数据的操作地址与第一输出寄存器对应,则向第一目标位写入位数据,以改变目标GPIO引脚的状态。为GPIO引脚配置一个独立的输出寄存器,在操作GPIO引脚时,可以直

芯片设计方法、装置、芯片、电子设备及存储介质.pdf

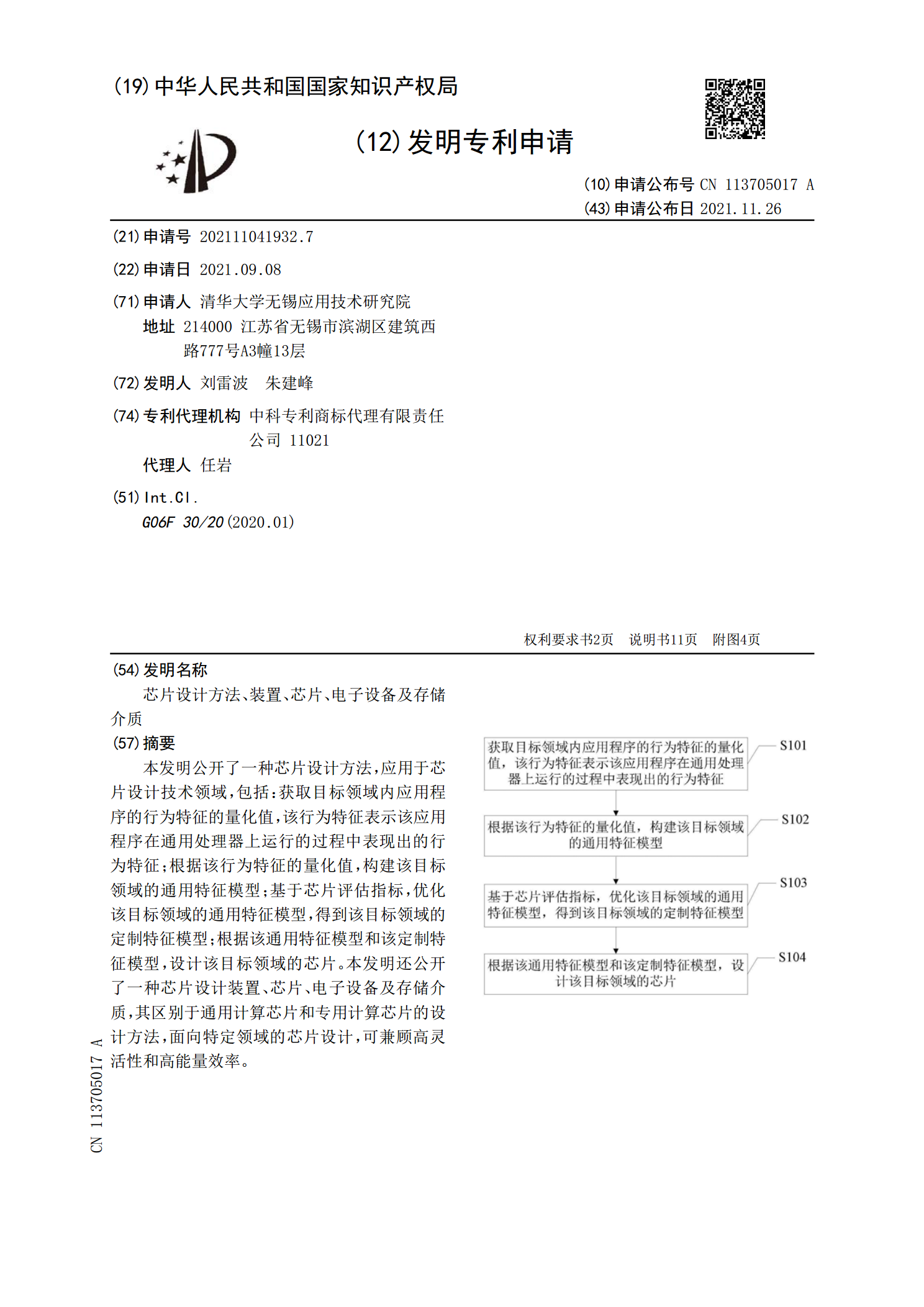

本发明公开了一种芯片设计方法,应用于芯片设计技术领域,包括:获取目标领域内应用程序的行为特征的量化值,该行为特征表示该应用程序在通用处理器上运行的过程中表现出的行为特征;根据该行为特征的量化值,构建该目标领域的通用特征模型;基于芯片评估指标,优化该目标领域的通用特征模型,得到该目标领域的定制特征模型;根据该通用特征模型和该定制特征模型,设计该目标领域的芯片。本发明还公开了一种芯片设计装置、芯片、电子设备及存储介质,其区别于通用计算芯片和专用计算芯片的设计方法,面向特定领域的芯片设计,可兼顾高灵活性和高能量

芯片验证方法、装置、电子设备及存储介质.pdf

本公开提出一种芯片验证方法、装置、电子设备及存储介质,其中,该方法包括:获取待验证芯片的性能数据的传输时段;根据传输时段,确定至少一个第一子时段以及各第一子时段中的第二子时段;根据各第一子时段对应的时长和设定目标性能指标,确定对应的第一子时段中的第二子时段的期望目标性能指标;根据各设定目标性能指标以及各期望目标性能指标,运行待验证芯片,以得到待验证芯片在各所述第一子时段的监测目标性能指标,由此,通过第一子时段的设定目标性能指标以及第二子时段的期望目标性能,可使待验证芯片在各第一子时段的监测目标性能指标,符