像素驱动电路及像素驱动方法.pdf

fu****级甜

亲,该文档总共19页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

像素驱动电路及像素驱动方法.pdf

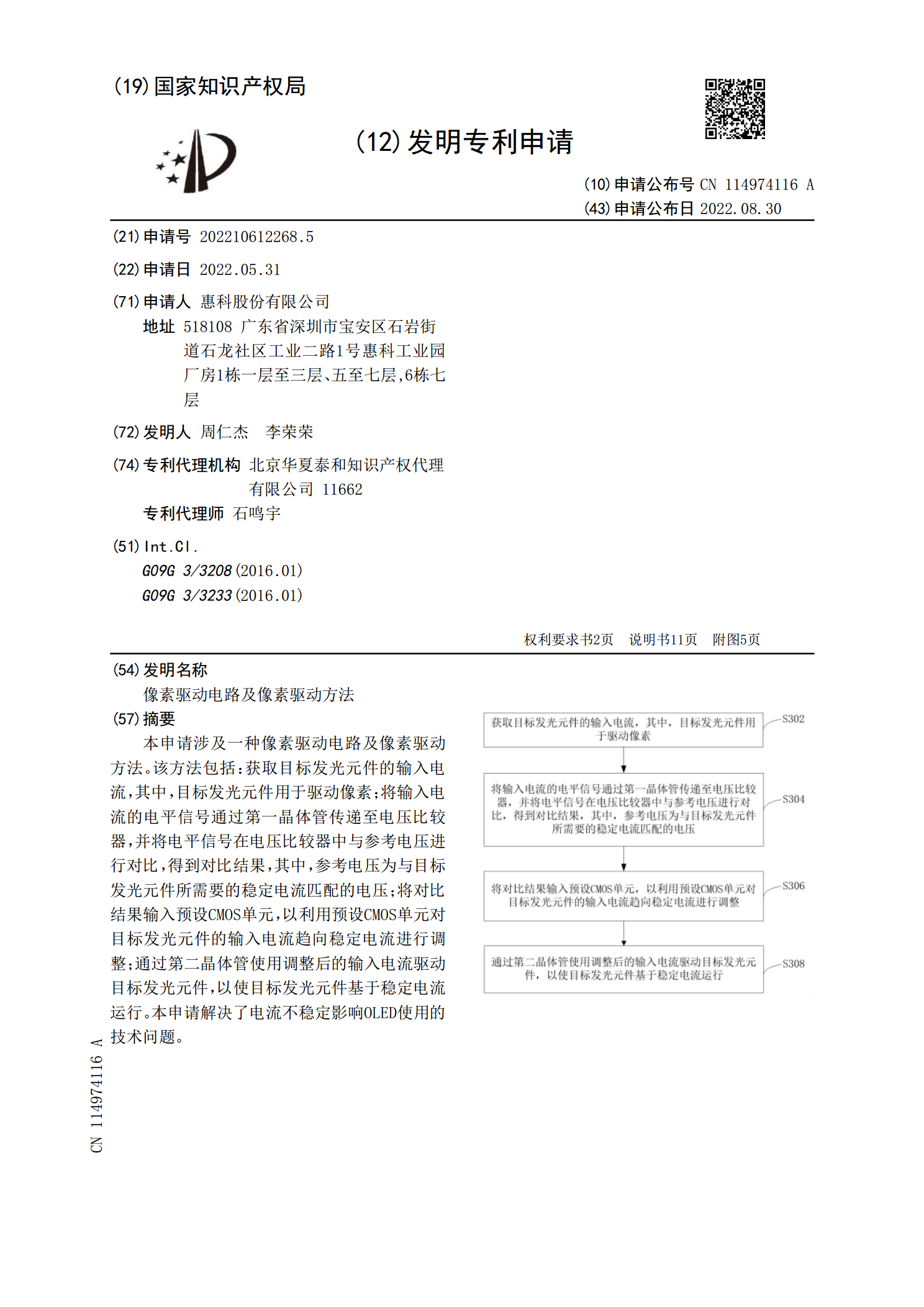

本申请涉及一种像素驱动电路及像素驱动方法。该方法包括:获取目标发光元件的输入电流,其中,目标发光元件用于驱动像素;将输入电流的电平信号通过第一晶体管传递至电压比较器,并将电平信号在电压比较器中与参考电压进行对比,得到对比结果,其中,参考电压为与目标发光元件所需要的稳定电流匹配的电压;将对比结果输入预设CMOS单元,以利用预设CMOS单元对目标发光元件的输入电流趋向稳定电流进行调整;通过第二晶体管使用调整后的输入电流驱动目标发光元件,以使目标发光元件基于稳定电流运行。本申请解决了电流不稳定影响OLED使用的

一种像素驱动方法及像素驱动电路.pdf

本发明提供了一种像素驱动方法及像素驱动电路,涉及显示技术领域。其中,所述方法包括:在息屏情况下,向像素的薄膜晶体管的栅极输入第一电压并持续预设时长;所述第一电压大于或等于所述薄膜晶体管的阈值电压;向所述栅极输入第二电压,进入手势唤醒模式;所述第二电压小于所述阈值电压。在本发明实施例中,可以在进入手势唤醒模式之前,通过第一电压开启像素的薄膜晶体管,从而释放像素内的残留电荷,使得像素内不再满足电荷守恒,如此,进入手势唤醒模式后栅极电压的变化,不会造成像素电压的抬升,进而能够避免抬升电压所形成的电场对液晶的极化

像素电路驱动方法、像素驱动装置以及显示装置.pdf

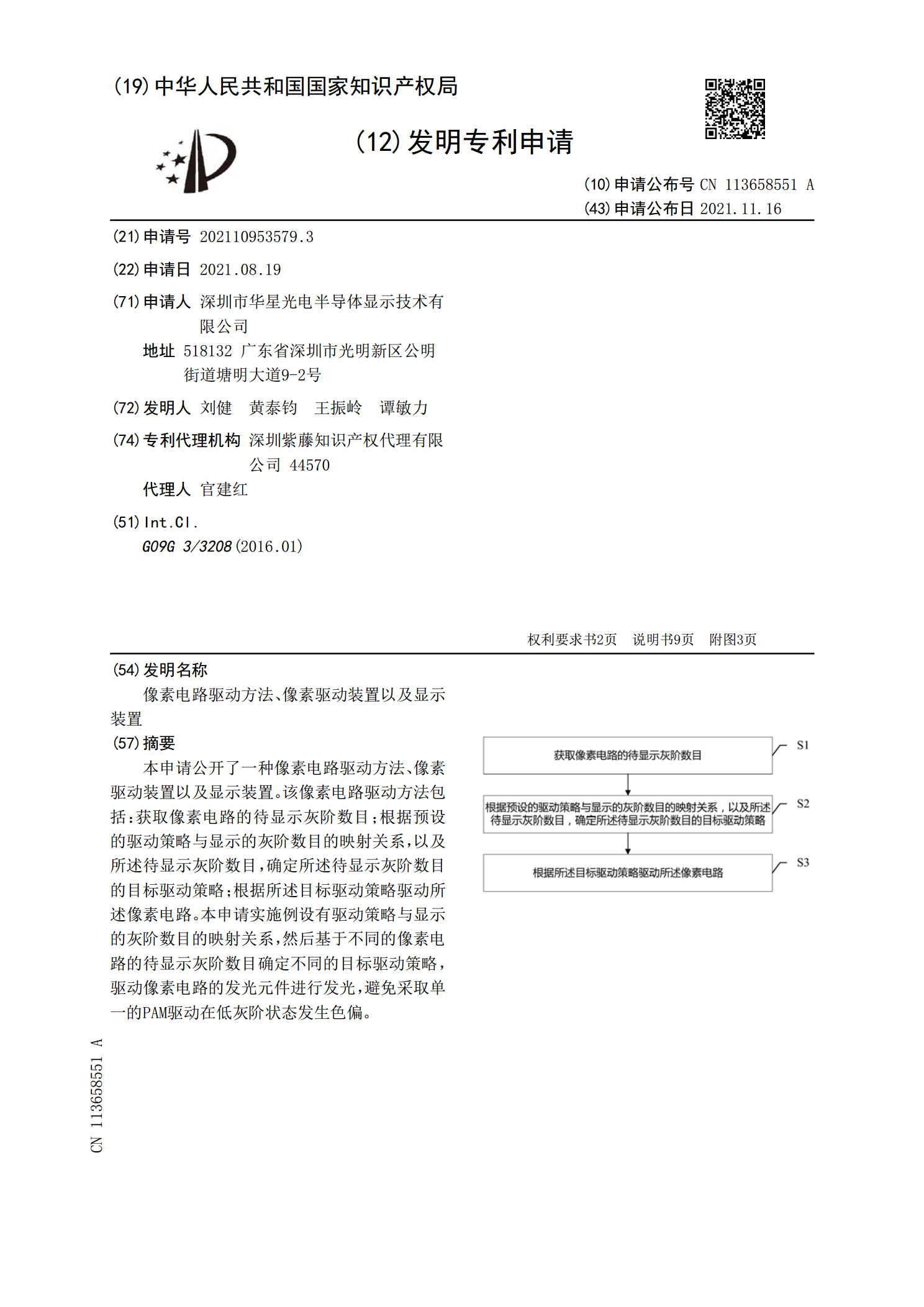

本申请公开了一种像素电路驱动方法、像素驱动装置以及显示装置。该像素电路驱动方法包括:获取像素电路的待显示灰阶数目;根据预设的驱动策略与显示的灰阶数目的映射关系,以及所述待显示灰阶数目,确定所述待显示灰阶数目的目标驱动策略;根据所述目标驱动策略驱动所述像素电路。本申请实施例设有驱动策略与显示的灰阶数目的映射关系,然后基于不同的像素电路的待显示灰阶数目确定不同的目标驱动策略,驱动像素电路的发光元件进行发光,避免采取单一的PAM驱动在低灰阶状态发生色偏。

像素电路、像素电路驱动方法及显示装置.pdf

本发明涉及有机发光显示技术领域,具体涉及一种像素电路、驱动该像素电路的驱动方法以及包括该像素电路的显示装置。该像素电路包括至少两个电致发光元件,各个所述电致发光元件的第一极性的电极与一个电流控制端连接,各个所述电致发光元件的第二极性的电极与为所述电致发光元件供应驱动电流的驱动单元连接。本发明所提供的像素电路,通过设置至少两个独立控制的有机发光二极管,分别控制各个有机发光二极管轮流处于发光显示状态,避免了单一的有机发光二极管长期处于直流偏置发光状态,减缓了有机材料的极性化速度,使有机发光二极管阈值电压稳定,

像素驱动方法、驱动电路及显示面板.pdf

本申请属于显示面板技术领域,具体涉及一种像素驱动方法、驱动电路以及显示面板;本申请的像素驱动方法包括:获取每列数据线对应的目标数据电压;基于各列数据线对应的目标数据电压计算出基准数据电压;在向各列数据线施加与其对应的目标数据电压之前,将基准数据电压施加至各列数据线上;在扫描之前,将各列数据线上的电压从基准数据电压调整至对应的目标数据电压。利用本申请的像素驱动方法,显示面板对应的各列数据线上的寄生电容所产生的总功率要小于将各列数据线上的电压从上一帧画面的遗留电压调整至对应的目标数据电压所产生的总功率,因此,