数字电路与逻辑设计习题6第六章时序逻辑电路.pdf

文库****品店

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

数字电路与逻辑设计习题6第六章时序逻辑电路.pdf

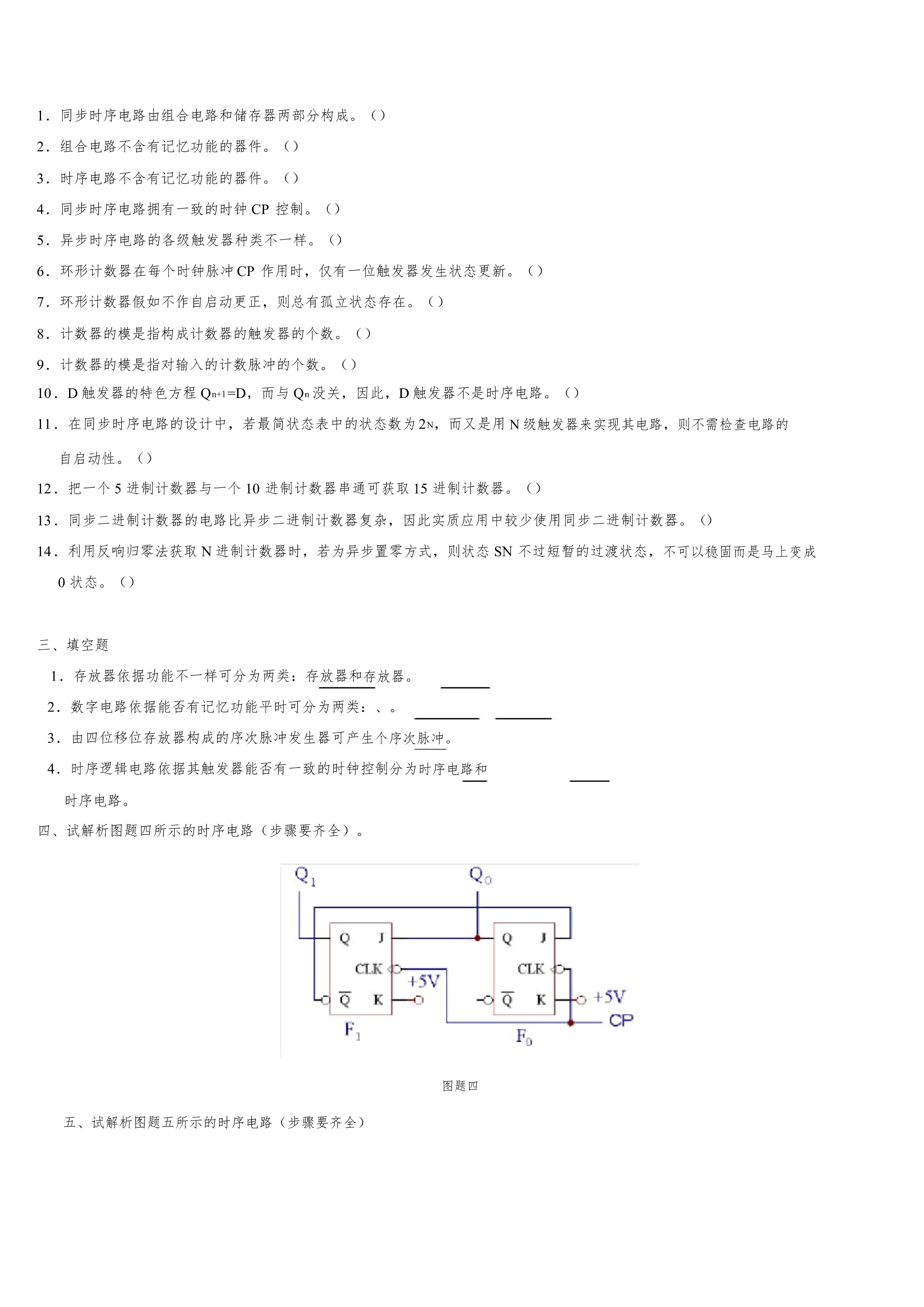

一、选择题1.同步计数器和异步计数器比较,同步计数器的明显长处是。A.工作速度高B.触发器利用率高C.电路简单D.不受时钟CP控制。2.把一个五进制计数器与一个四进制计数器串通可获取进制计数器。3.以下逻辑电路中为时序逻辑电路的是。A.变量译码器B.加法器C.数码存放器D.数据选择器4.N个触发器可以构成最大计数长度(进制数)为的计数器。5.N个触发器可以构成能存放位二进制数码的存放器。+16.五个D触发器构成环形计数器,其计数长度为。7.同步时序电路和异步时序电路比较,其差异在于后者。A.没有触发器B.

数字电路与逻辑设计习题-6第六章时序逻辑电路.pdf

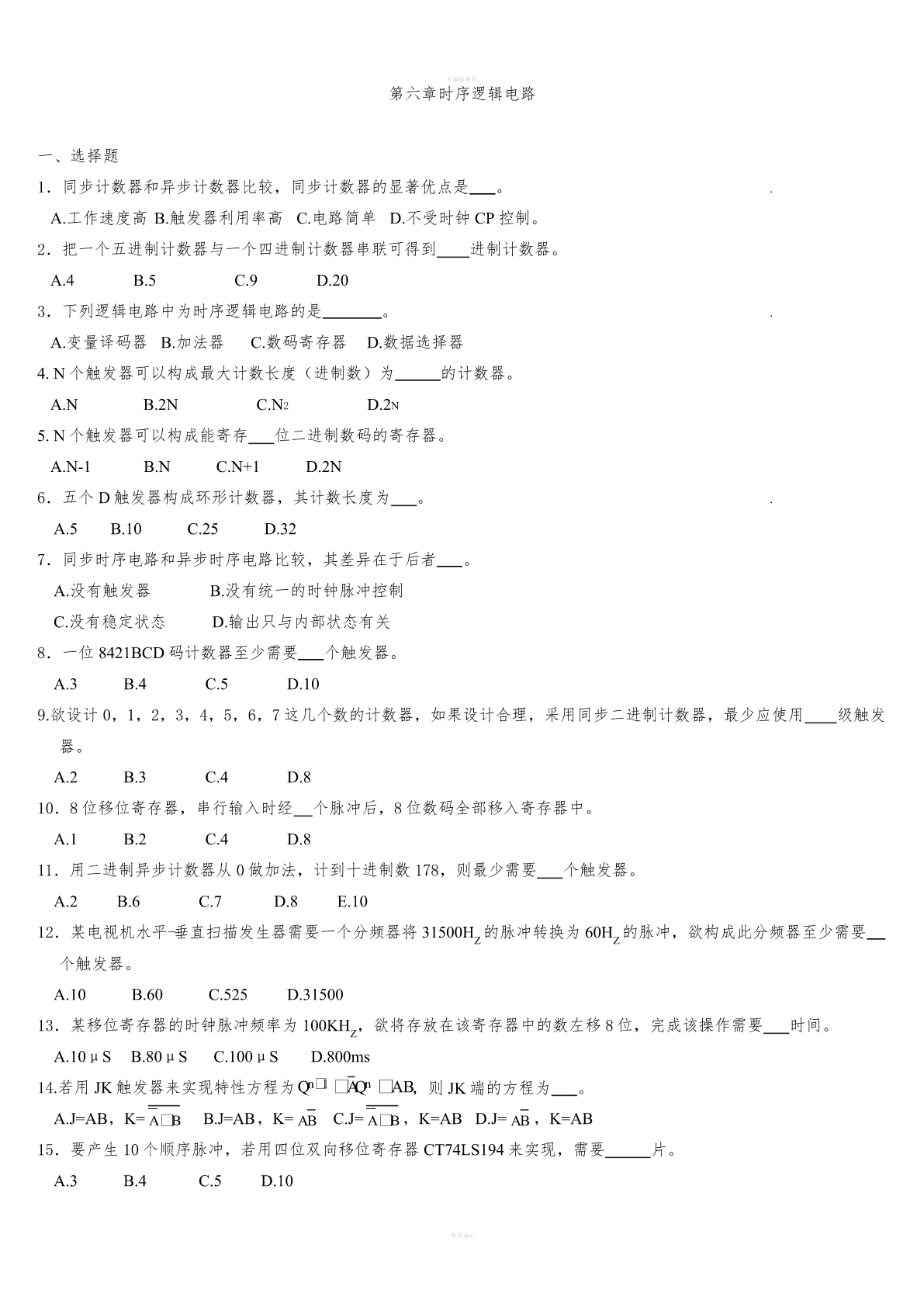

可编辑修改第六章时序逻辑电路一、选择题1.同步计数器和异步计数器比较,同步计数器的显著优点是。A.工作速度高B.触发器利用率高C.电路简单D.不受时钟CP控制。2.把一个五进制计数器与一个四进制计数器串联可得到进制计数器。A.4B.5C.9D.203.下列逻辑电路中为时序逻辑电路的是。A.变量译码器B.加法器C.数码寄存器D.数据选择器4.N个触发器可以构成最大计数长度(进制数)为的计数器。A.NB.2NC.N2D.2N5.N个触发器可以构成能寄存位二进制数码的寄存器。A.N-1B.NC.N+1D.2N6

数字电路与逻辑设计习题时序逻辑电路.docx

第六章时序逻辑电路选择题1.同步计数器和异步计数器比较,同步计数器的显著优点是。A.工作速度高B.触发器利用率高C.电路简单D.不受时钟CP控制。2.把一个五进制计数器与一个四进制计数器串联可得到进制计数器。A.4B.5C.9D.203.下列逻辑电路中为时序逻辑电路的是。A.变量译码器B.加法器C.数码寄存器D.数据选择器4.N个触发器可以构成最大计数长度(进制数)为的计数器。A.NB.2NC.N2D.2N5.N个触发器可以构成能寄存位二进制数码的寄存器。A.N-1B.NC.N+1D.2N6.五个D触发器

数字电路逻辑设计第六章时序逻辑电路.ppt

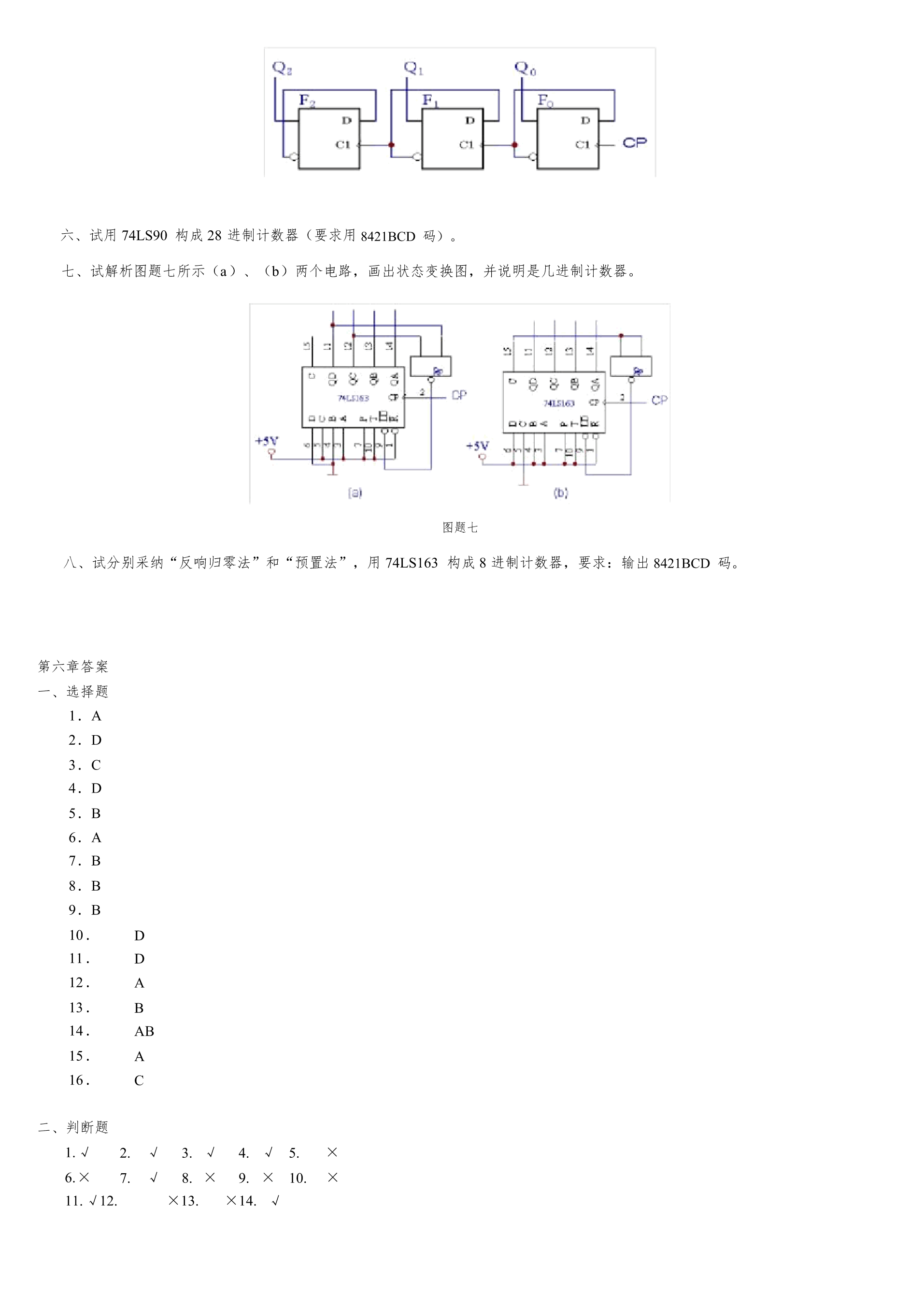

第六章时序逻辑电路第一节时序逻辑电路概述输入输出情况分析:外来输入:X、CP内部输入:Q外部输出:Z内部输出:Q由下列时序图可见,在相同的外部输入条件下,存储电路X=1,T=0的状态不同,输出结触发器保持果完全不同。与组合电路有明显的区别。Z为三者相与Q初始为0,则Z一直为0Q初始为1,Z如图可见Q的影响之大。时序电路输入输出关系概括时序电路可分为两大类:第二节时序逻辑电路分析一、时序逻辑电路的分析步骤(4)列出状态转移表,或画出状态转移图。(5)画出工作波形图。(6)总结概括电路功能。例7-1分析图示电

数字电路第六章时序逻辑电路练习题cao.doc

第六章时序逻辑电路复习练习题一、填空题:1.构造一个模6计数器需要个状态,个触发器。构成一个1位十进制同步加法计数器至少需要()个JK触发器,一个1位5进制同步加法计数器至少需要()个JK触发器。2.若要构成七进制计数器,最少用_________个触发器,它有______个无效状态。3.构成一异步进制加法计数器需要n个触发器,一般将每个触发器接成计数或T’型触发器。计数脉冲输入端相连,高位触发器的CP端与邻低位端相连。4.一个4位移位寄存器,经过4个时钟脉冲CP后,4位串行输入数码全部存入寄存器;再经过4