基于P-GaN帽层和Fin结构的增强型射频器件及其制备方法.pdf

萌运****魔王

亲,该文档总共17页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

基于P-GaN帽层和Fin结构的增强型射频器件及其制备方法.pdf

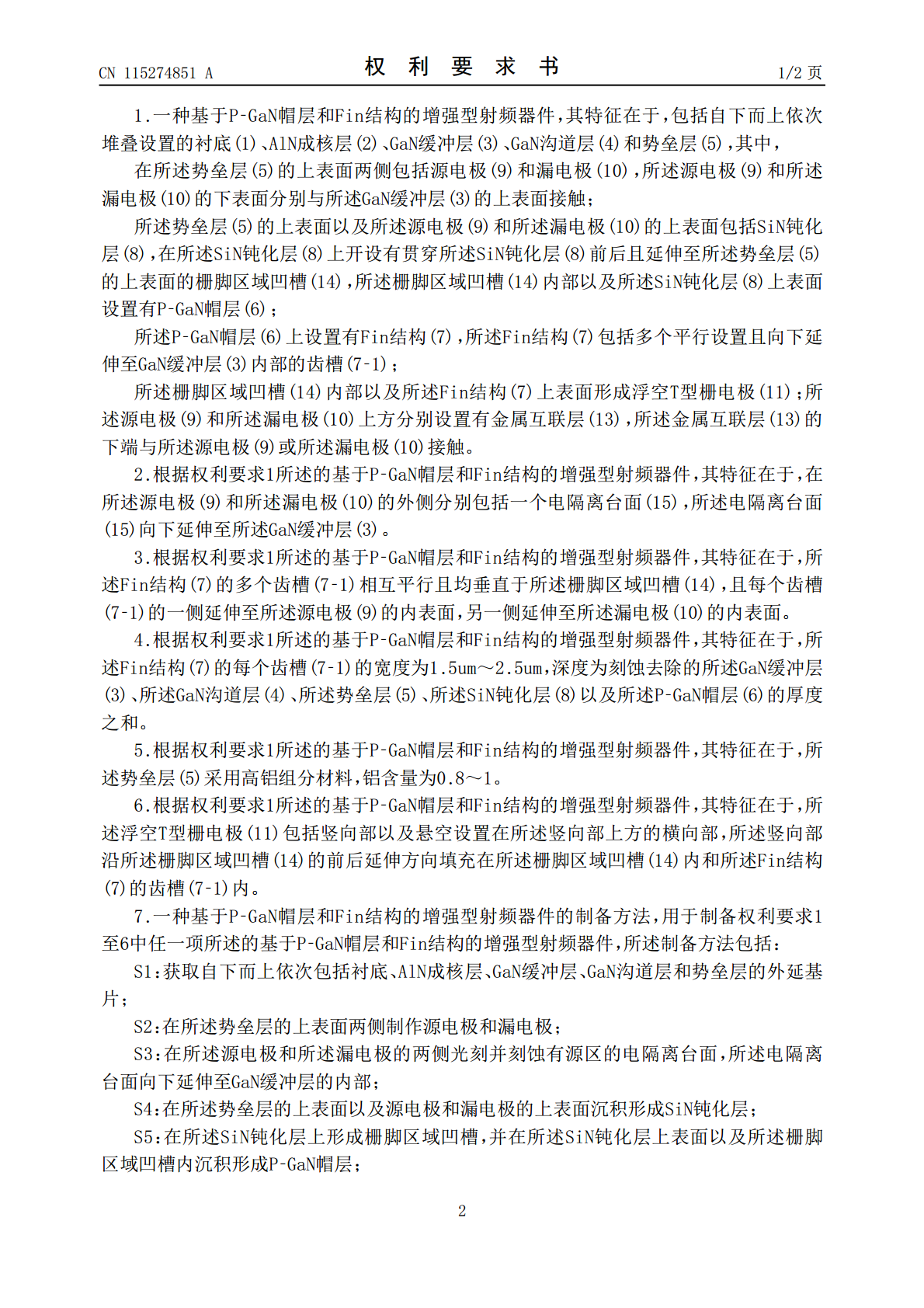

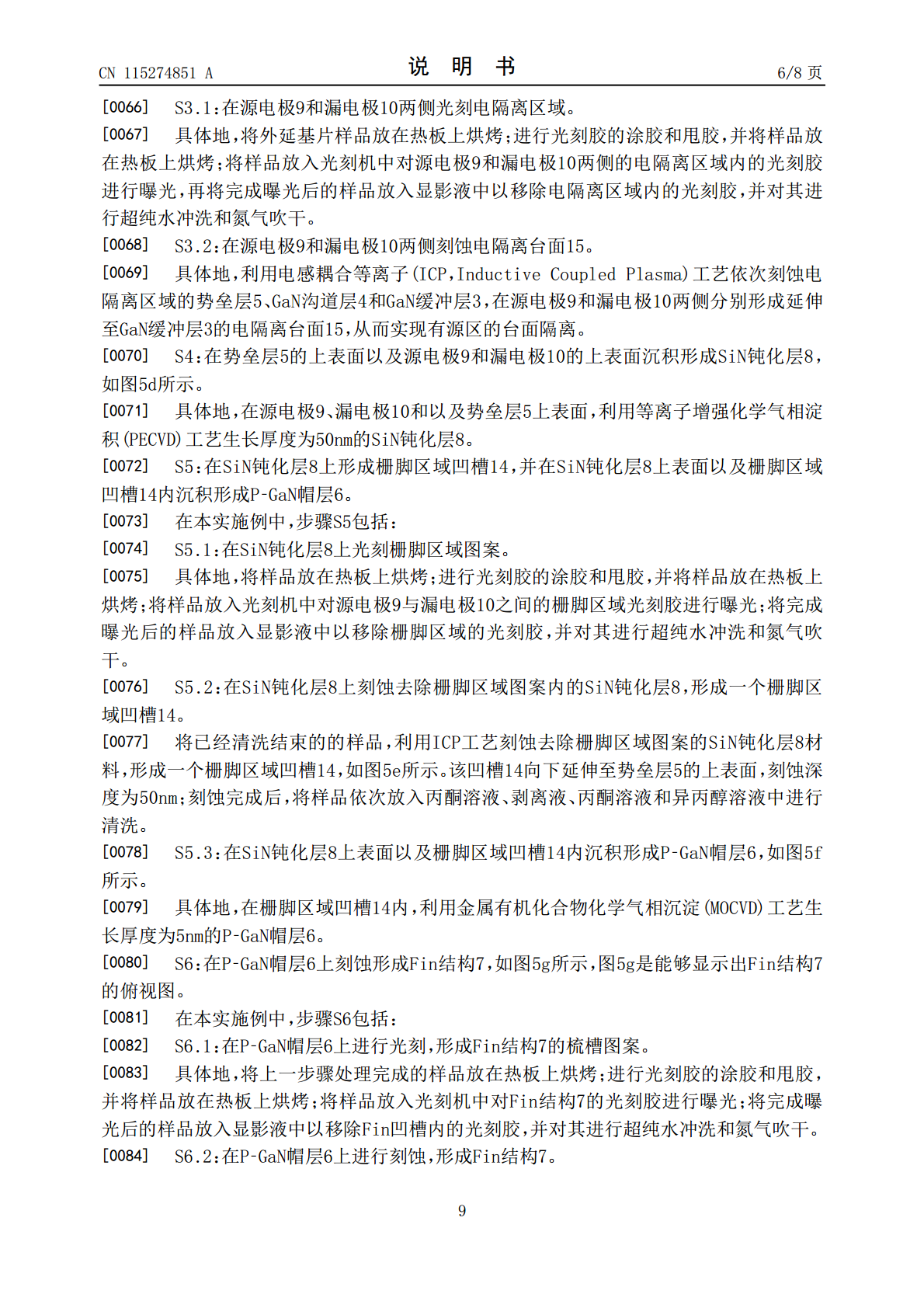

本发明公开一种基于P‑GaN帽层和Fin结构的增强型射频器件及其制备方法,所述器件包括自下而上依次堆叠设置的衬底、AlN成核层、GaN缓冲层、GaN沟道层和势垒层,其中,在势垒层的上表面两侧包括源电极和漏电极;势垒层的上表面以及源电极和漏电极的上表面包括SiN钝化层,在SiN钝化层上开设有栅脚区域凹槽,栅脚区域内部以及SiN钝化层上表面设置有P‑GaN帽层;P‑GaN帽层上设置有Fin结构;栅脚区域凹槽内部以及Fin结构上表面形成浮空T型栅电极;源电极和漏电极上方分别设置有金属互联层。本发明利用P‑GaN

膜层及其制备方法和发光器件及其制备方法.pdf

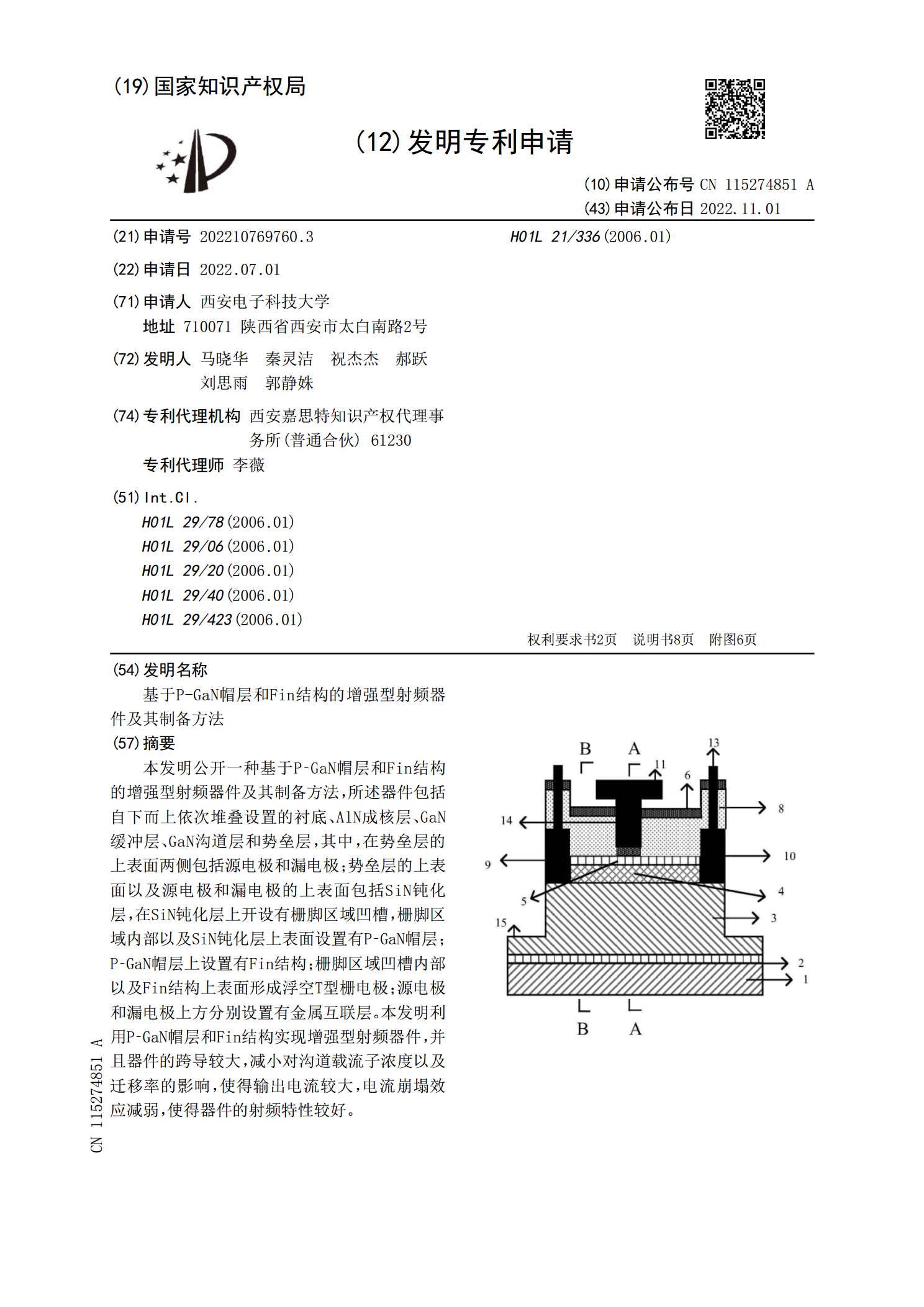

本申请涉及一种膜层及其制备方法和发光器件及其制备方法,属于发光器件技术领域。一种膜层的制备方法,包括将含硫有机物溶液涂覆于基底的表面形成溶液层,在溶液层上旋涂氧化锌溶液,再进行热处理;或将氧化锌溶液涂覆于基底的表面形成溶液层,在溶液层上旋涂含硫有机物溶液,再进行热处理。通过对电子传输层ZnO表面进行硫化,原位生成更为稳定的ZnS,形成复合的ZnO/ZnS层,该复合层增强了电子传输层的势垒高度,可以降低电子传输速率,有利于电荷注入平衡,提高了电子传输层的稳定性。

原位SiN帽层AlGaN/GaN异质结增强型器件及其制作方法.pdf

本发明公开了一种原位SiN帽层AlGaN/GaN异质结增强型器件及其制作方法,主要解决目前增强型高电子迁移率晶体管阈值电压均匀性及工艺重复性差的问题。其制作过程为:(1)在SiC或蓝宝石基片上生长本征GaN层,然后生长厚度为8~16nm、Al组分为25~35%的AlGaN势垒层;(2)在AlGaN势垒层表面生长原位SiN帽层,并进行栅槽刻蚀露出栅区域;(3)在露出栅区域的AlGaN势垒层表面淀积金属Ni和Al;(4)在800℃~860℃下采用快速热退火炉进行氧气环境的高温热处理,形成NiO和Al2O3层;

增强型MOSFET器件及其制备方法.pdf

本申请公开了一种增强型MOSFET器件,包括:衬底;N型GaN缓冲层,位于衬底的上方;U型GaN层,位于N型GaN缓冲层的上方;P型GaN层,位于U型GaN层的上方;N型Poly‑Si层,位于P型GaN层的上方;栅介质层,位于N型Poly‑Si层的上方;栅极,位于栅介质层的上方;源极,位于N型Poly‑Si层的上方;漏极,位于U型GaN层的上方,漏极和源极分别位于栅极两侧。本申请将N型Poly‑Si层直接形成在载流子浓度较低的U型GaN层上,再将漏极形成在N型Poly‑Si层上,采用此结构相当于形成漏极的

基于P型帽层低膝点电压的增强型AlGaN/GaN HEMT器件及方法.pdf

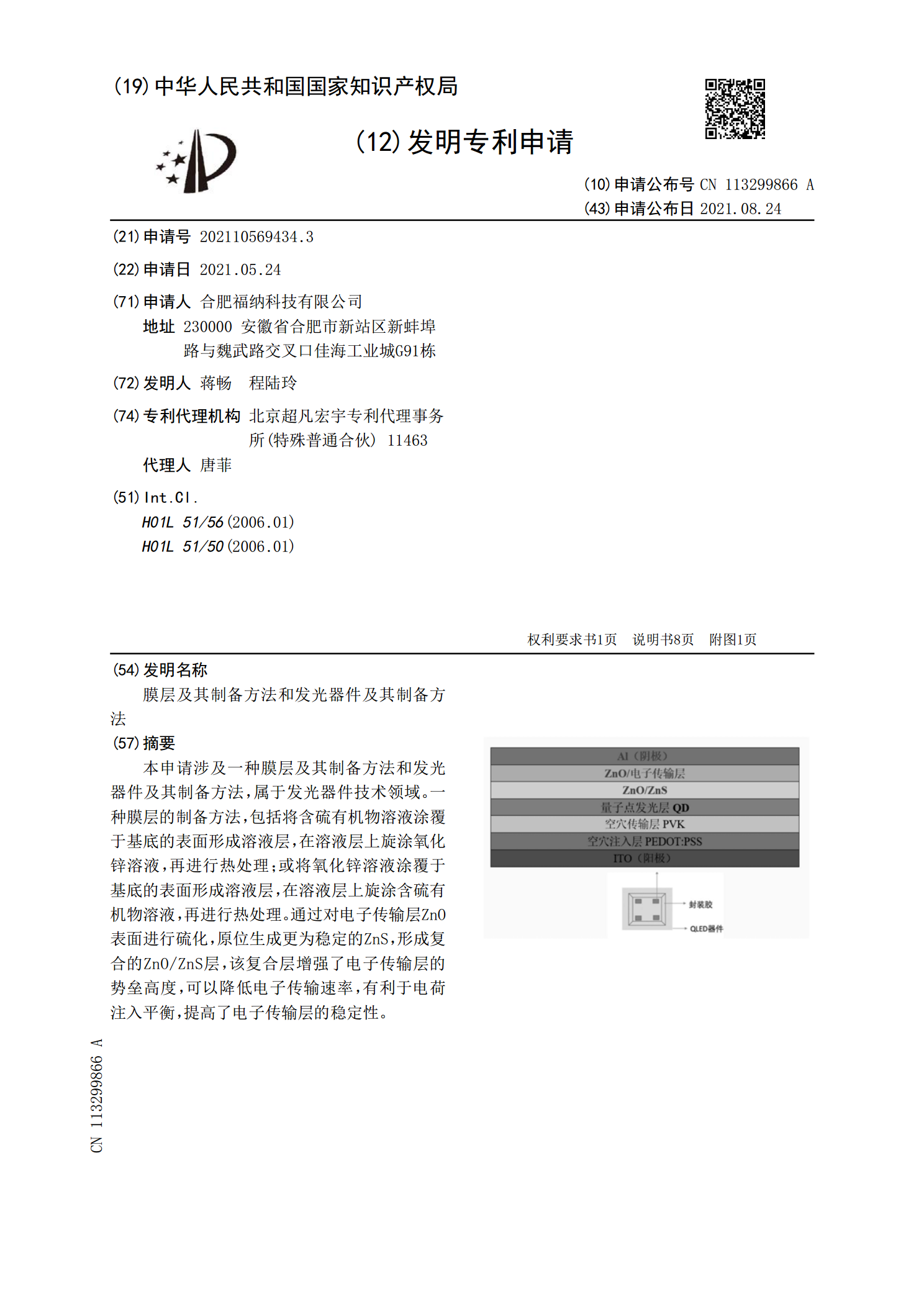

本发明公开了一种基于P型帽层低膝点电压的增强型AlGaN/GaNHEMT器件及方法。其器件包括自下而上依次设置的衬底、缓冲层、GaN沟道层、AlN中间层和AlGaN势垒层;AlGaN势垒层上方设有电子气恢复层,电子气恢复层上刻蚀或者腐蚀出源极区域、漏极区域以及栅极区域,栅极区域位于源极区域和漏极区域之间,其中,源极区域设有源电极,漏极区域设有漏电极,栅极区域设有栅区P型帽层和栅电极,栅电极位于栅区P型帽层上方。本发明在AlGaN势垒层上沉积兼容剥离工艺无刻蚀损伤的P型帽层,使栅区P型帽层和栅电极同步成型