半导体盲孔的检测方法.pdf

是你****韵呀

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体盲孔的检测方法.pdf

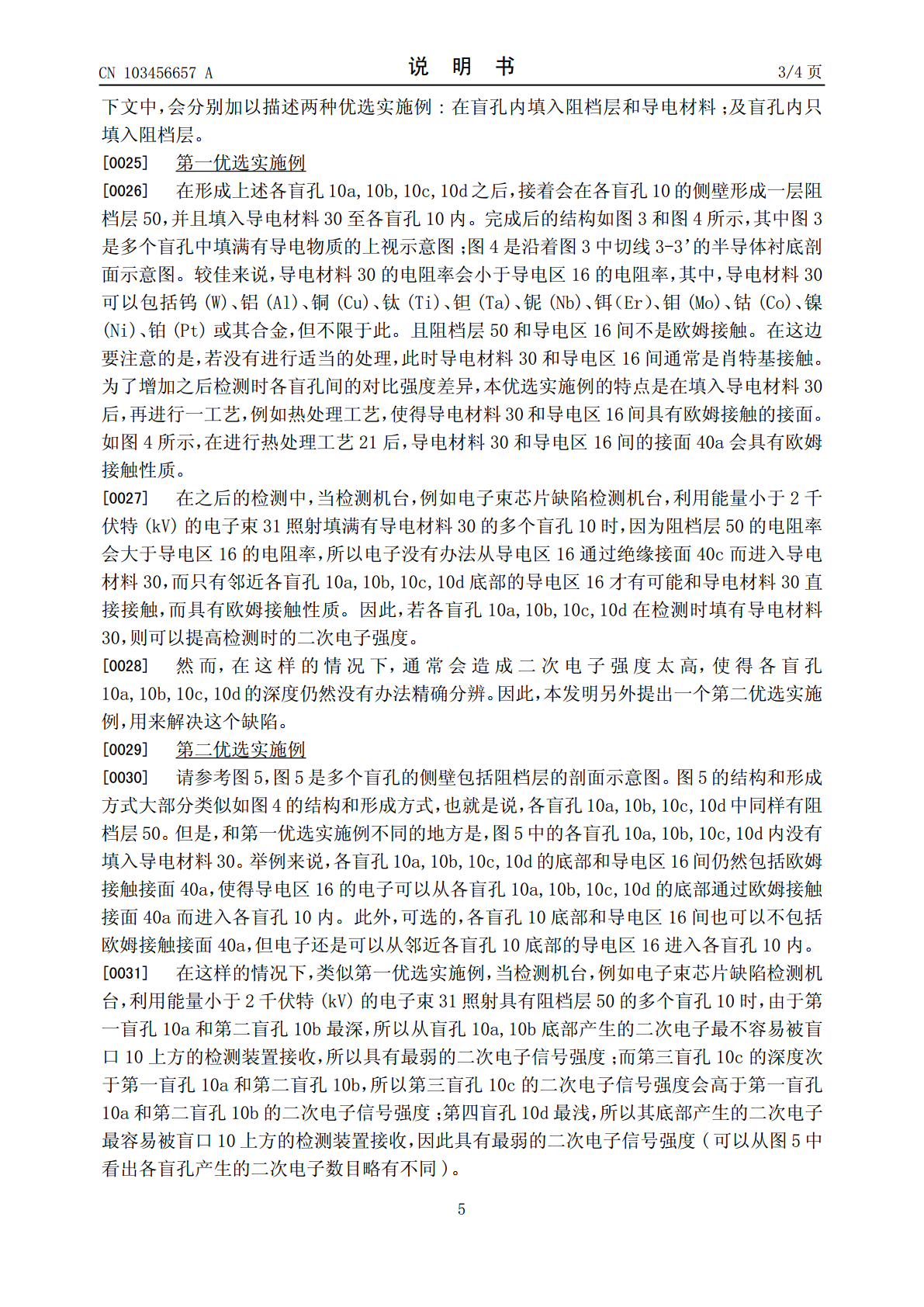

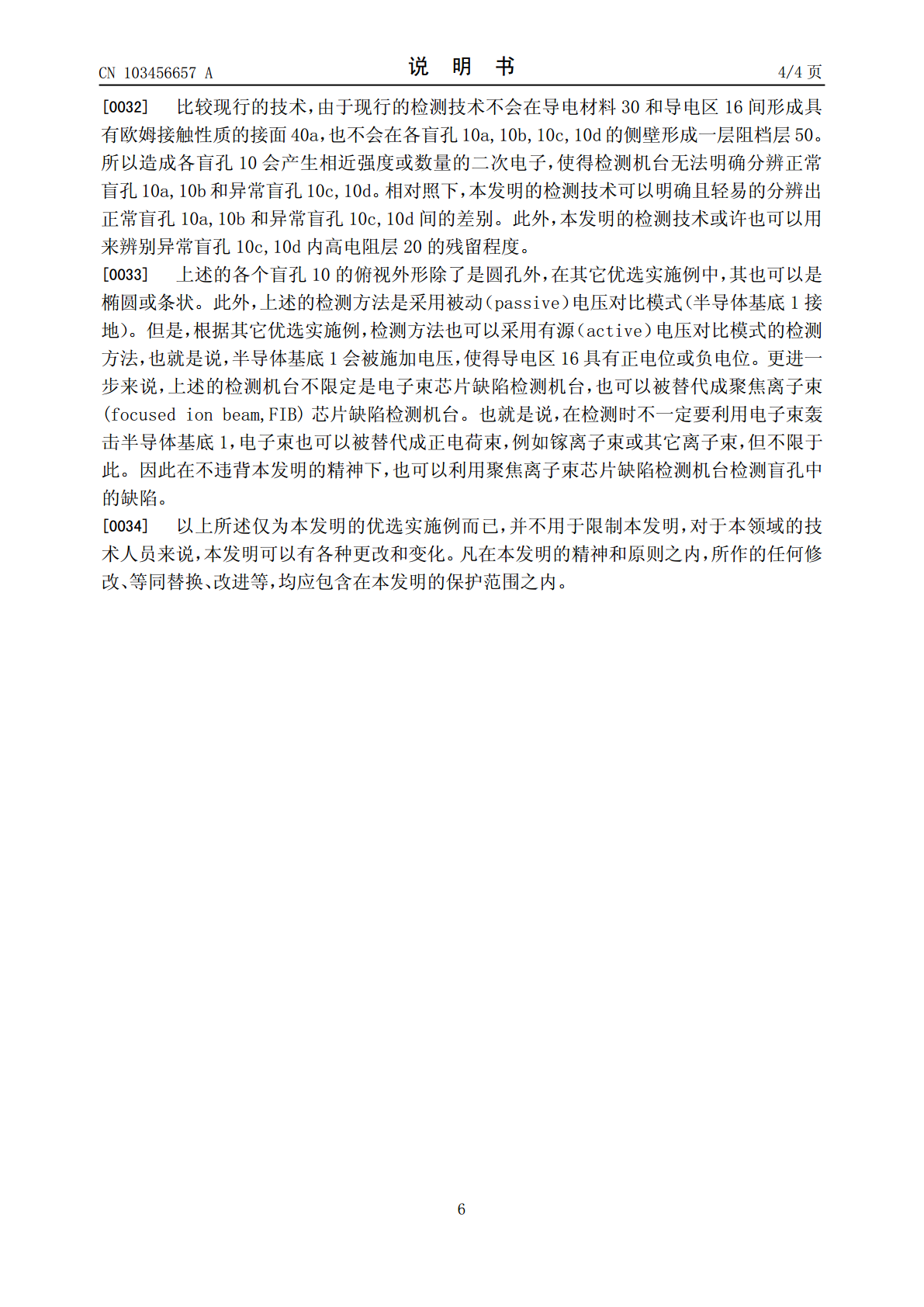

本发明公开了一种半导体盲孔的检测方法,包括提供一包括导电区的半导体衬底;形成多个暴露出导电区的盲孔,其特征在于电阻率大于导电区的高电阻层会位在至少一盲孔的部分或全部底部区域,且高电阻层和导电区的接触面不是欧姆接触;将导电材料填满多个盲孔,使导电材料和半导体衬底的接触面构成欧姆接触;及利用带电射线照射填满有所述导电材料的所述多个盲孔。

半导体盲孔的检测方法.pdf

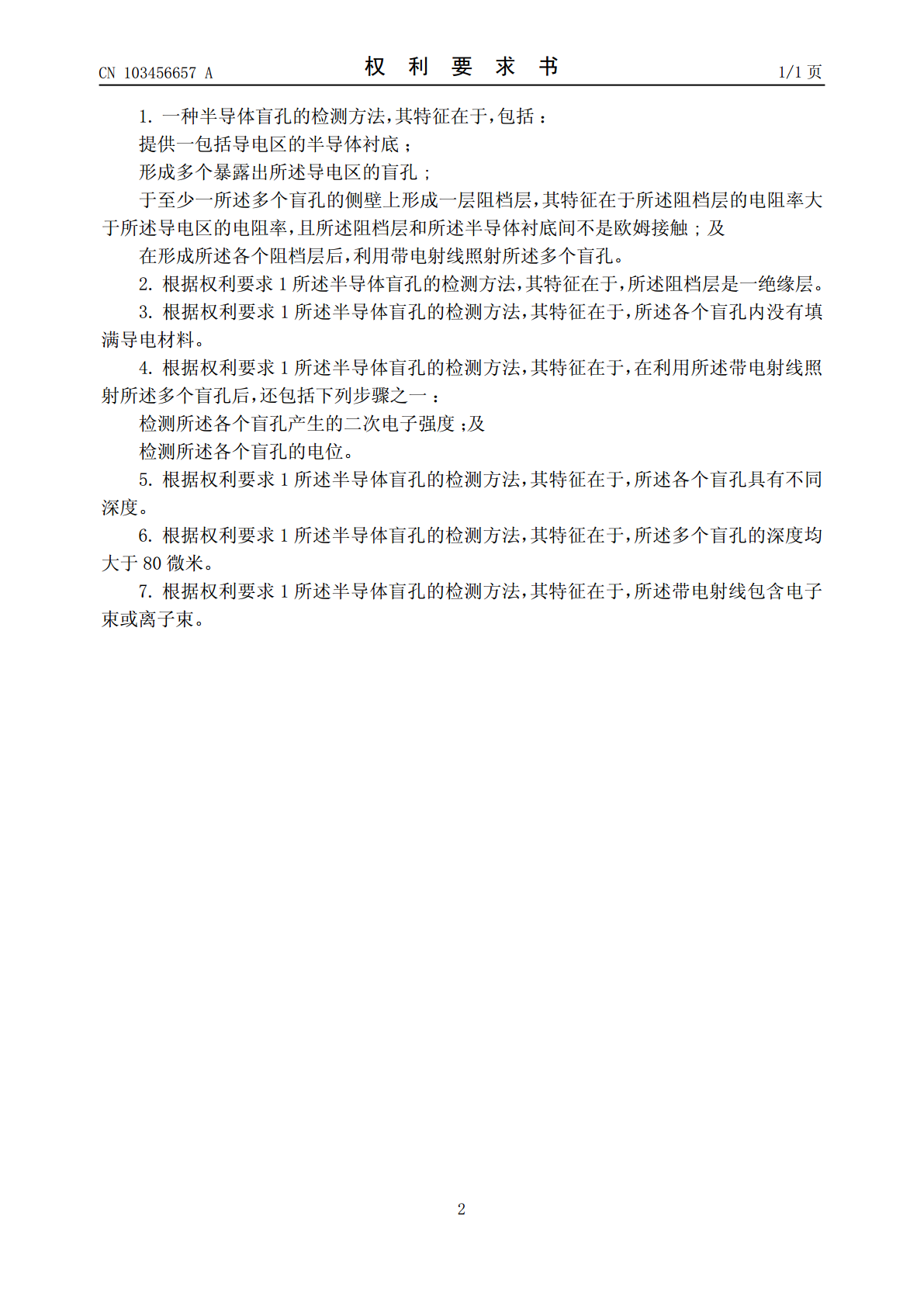

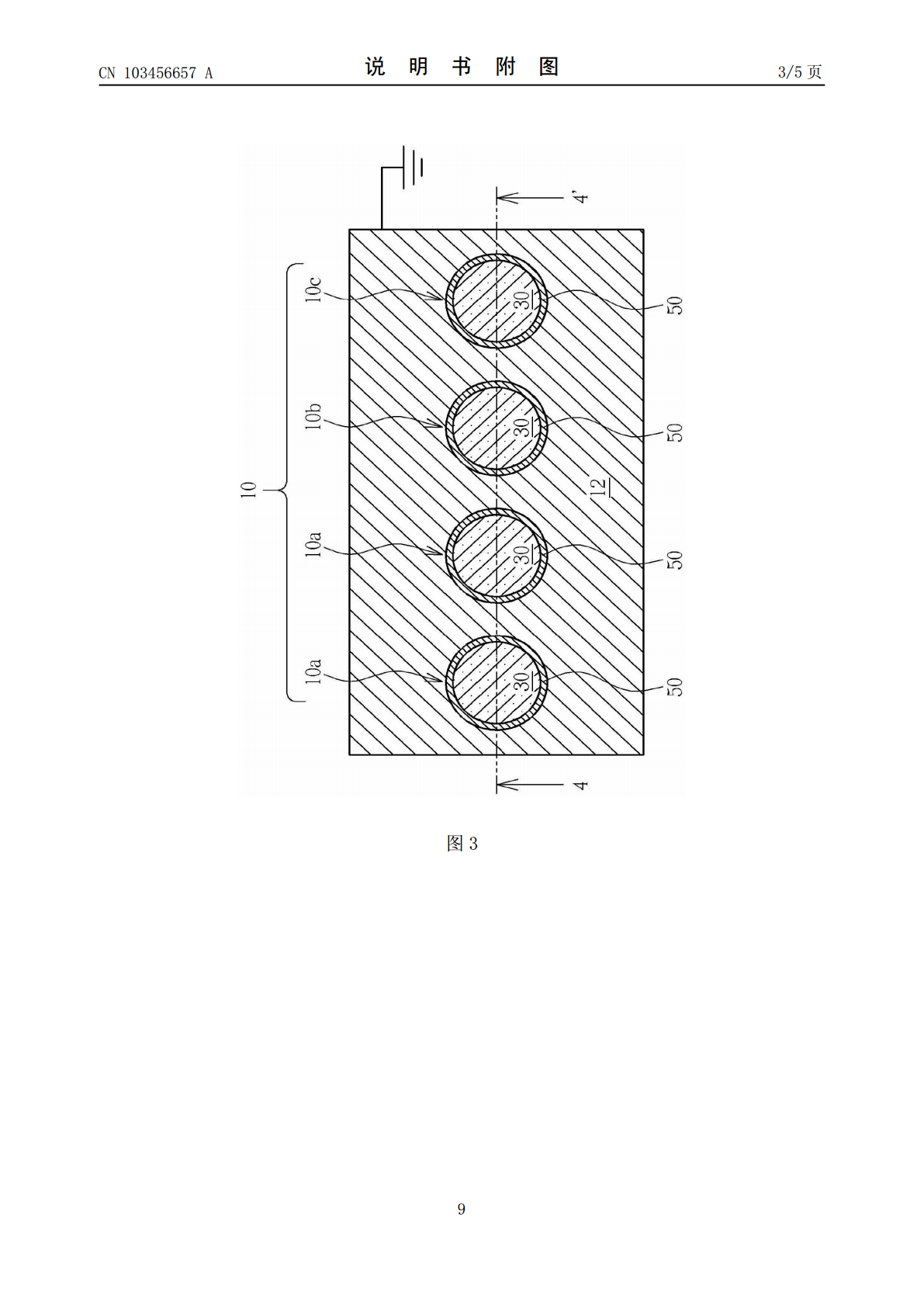

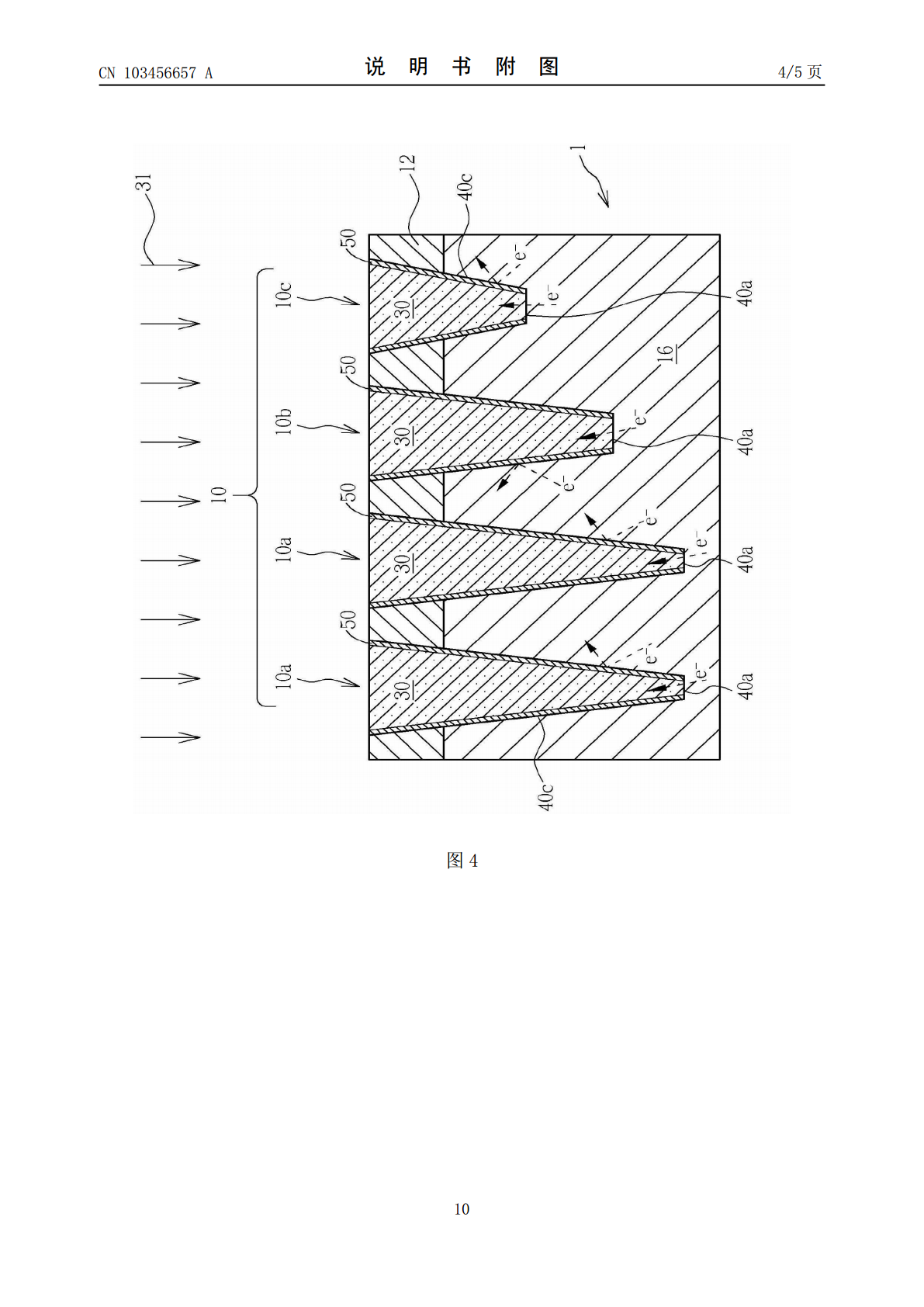

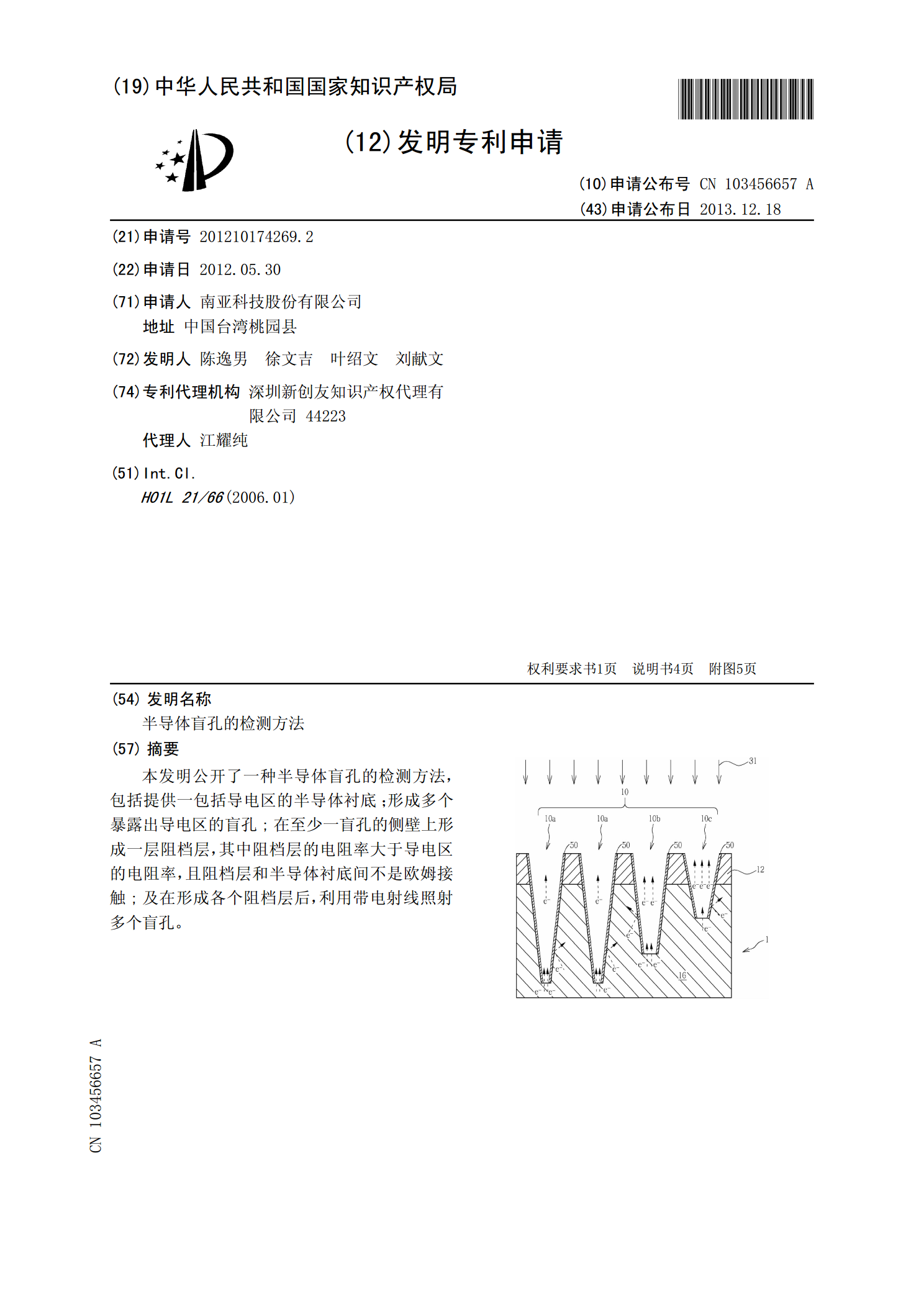

本发明公开了一种半导体盲孔的检测方法,包括提供一包括导电区的半导体衬底;形成多个暴露出导电区的盲孔;在至少一盲孔的侧壁上形成一层阻档层,其中阻档层的电阻率大于导电区的电阻率,且阻档层和半导体衬底间不是欧姆接触;及在形成各个阻档层后,利用带电射线照射多个盲孔。

半导体盲孔的检测方法.pdf

本发明公开了一种半导体盲孔的检测方法,包括提供一包括导电区的半导体基底;形成多个暴露出导电区的盲孔,其特征在于电阻率大于导电区的高电阻层会位在至少一盲孔的部分或全部底部区域,且高电阻层和导电区的接触面不是欧姆接触;将导电材料填满多个盲孔;进行一热处理工艺,使导电材料和半导体基底间形成欧姆接触;及利用带电射线照射填满有导电材料的多个盲孔。

半导体盲孔的检测方法.pdf

本发明公开了一种半导体盲孔的检测方法,包括提供一包括导电区的半导体基底;形成多个暴露出导电区的盲孔;在至少一所述多个盲孔的侧壁上形成一层阻档层,其中阻档层的电阻率大于导电区的电阻率;于各个盲孔的底部形成一层接触层;及在形成各个接触层后,利用带电射线照射多个盲孔。

半导体盲孔的检测方法.pdf

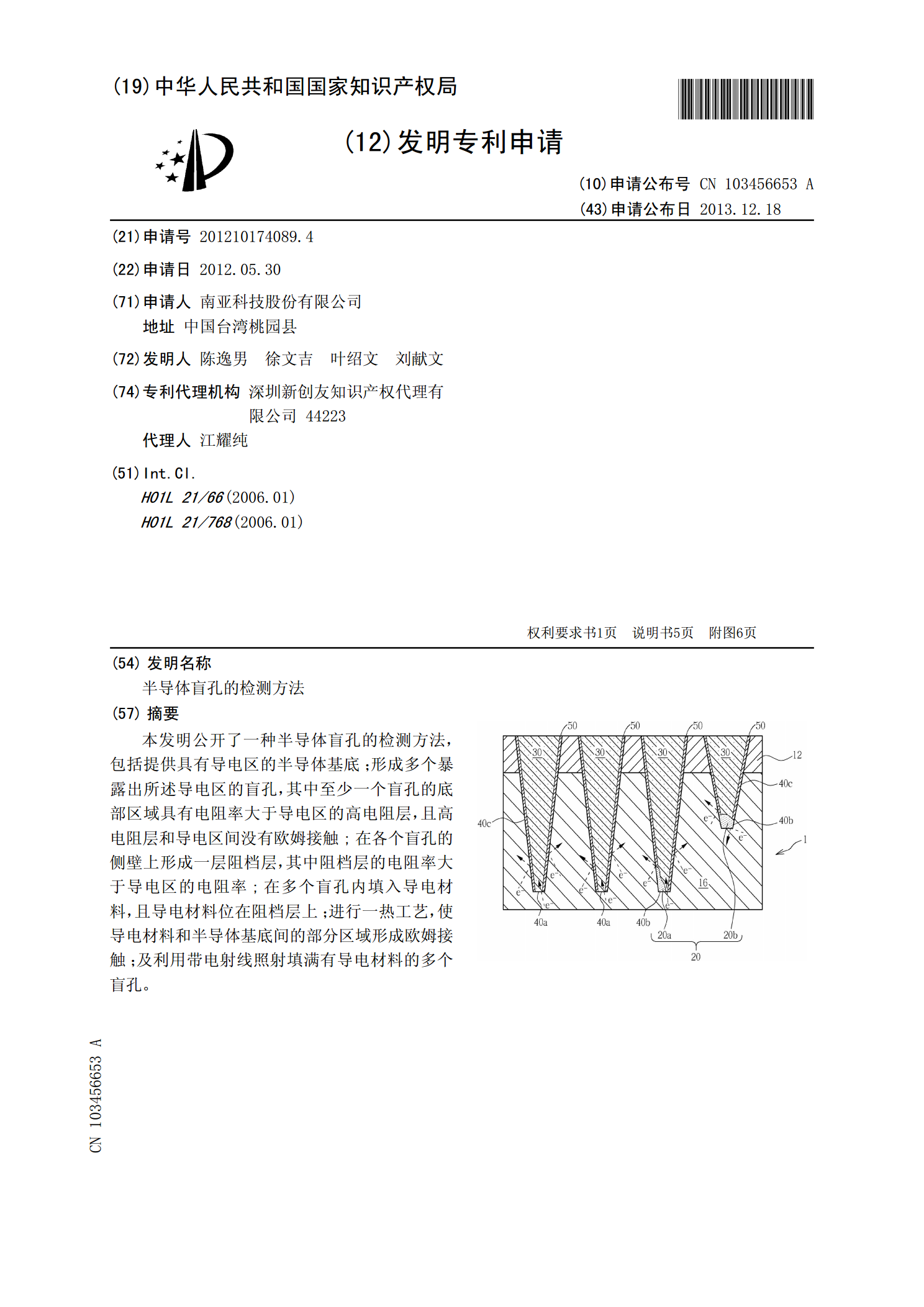

本发明公开了一种半导体盲孔的检测方法,包括提供具有导电区的半导体基底;形成多个暴露出所述导电区的盲孔,其中至少一个盲孔的底部区域具有电阻率大于导电区的高电阻层,且高电阻层和导电区间没有欧姆接触;在各个盲孔的侧壁上形成一层阻档层,其中阻档层的电阻率大于导电区的电阻率;在多个盲孔内填入导电材料,且导电材料位在阻档层上;进行一热工艺,使导电材料和半导体基底间的部分区域形成欧姆接触;及利用带电射线照射填满有导电材料的多个盲孔。