一种基于CNN的LDPC码盲信道译码方法及译码器.pdf

a是****澜吖

亲,该文档总共18页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种基于CNN的LDPC码盲信道译码方法及译码器.pdf

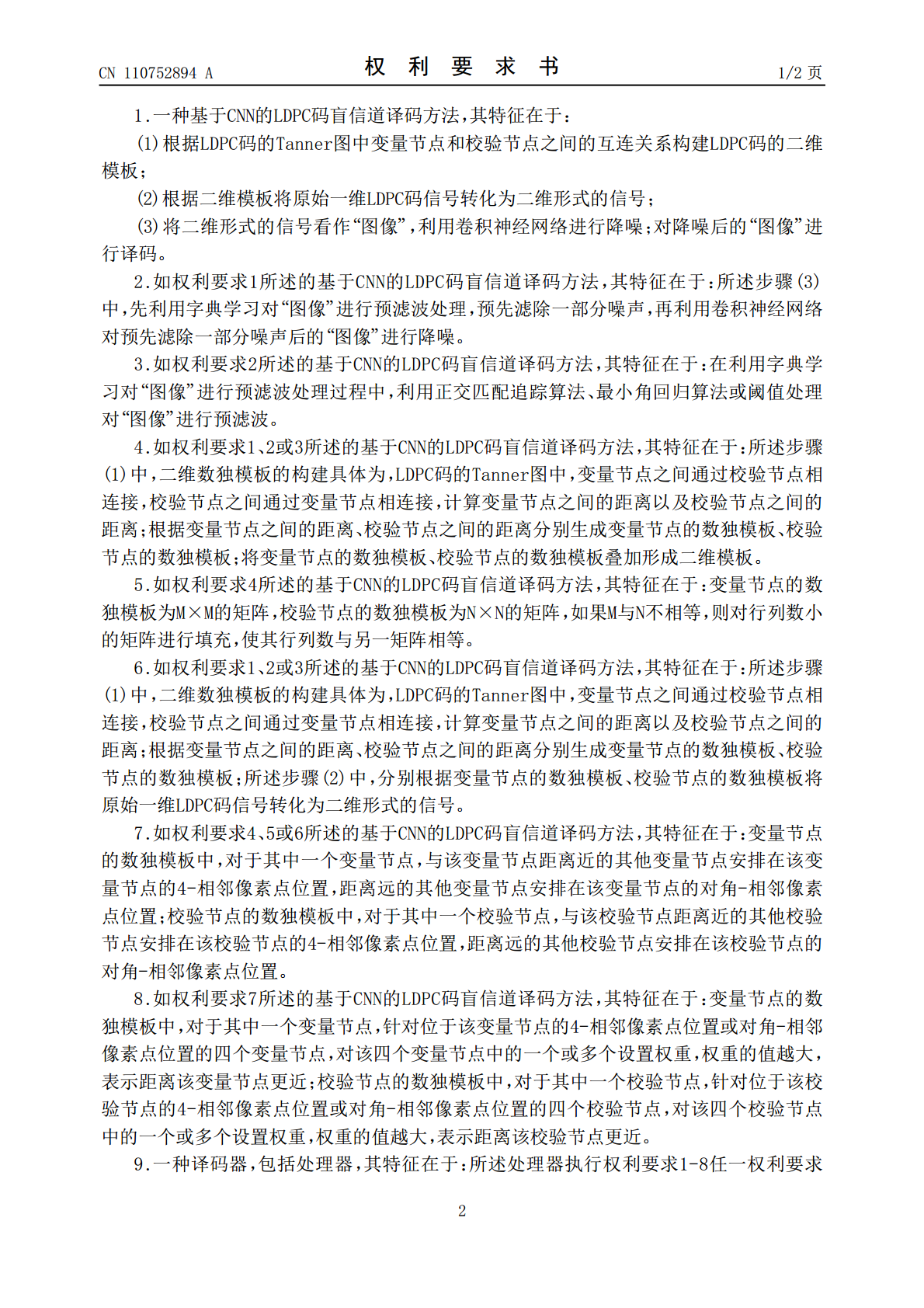

本发明提供一种无需信道检测的基于CNN的LDPC盲译码方法及译码器。利用LDPC码的Tanner图所展示出来的内部节点之间的互连关系确定模板,根据该模板将LDPC码一维信号转换为二维图像,再通过CNN对图像进行降噪处理,并在二维图像的基础上,对LDPC码进行译码,整个网络架构可以在无需维度变换的基础上进行降噪且译码。在相同条件下,盲译码算法相比于传统BP译码算法具有显著提升。

极化码的高效盲检测译码方法及译码器.pdf

本发明公开了一种极化码的高效盲检测译码方法及译码器,该盲检测译码方法利用SSC译码算法中的冻结位的对数似然比值,引入一个新的度量D,用以区分极化码与非极化码信号,以及不同制式的极化码信号。本发明实现了极化码的简化盲检测,能够避免接收机对于所有极化码制式候选进行复杂的译码算法,尽可能减少功耗,复杂度与延迟。在模拟真实传输环境的仿真中,简化盲检测算法在缺失码长N的基础上,译码的帧误码率可以在E

基于FPGA的LDPC码译码器的实现的开题报告.docx

基于FPGA的LDPC码译码器的实现的开题报告一、选题背景低密度奇偶校验码(Low-DensityParity-CheckCode,LDPC码)是一种经典的前向纠错编码,现已广泛应用于数字通信领域,包括有线和无线通信以及储存等多个领域。由于LDPC码具有相对较高的解码性能,因此在无线通信、深空通信和数字电视等领域得到了广泛的应用。而基于可编程逻辑芯片的LDPC码译码器实现已经成为近年来的研究热点之一。随着FPGA的高度集成和快速发展,现有的FPGA芯片已经具备了实现复杂通信算法所需的资源。因此该项目旨在研

基于FPGA的LDPC码译码器的实现的中期报告.docx

基于FPGA的LDPC码译码器的实现的中期报告一、项目简介本项目是基于FPGA实现LDPC码译码器,采用硬件加速的方式加快LDPC码的解码速度。LDPC码是一种码长很长且译码性能较好的纠错码,它在无线通信、数字广播、卫星通信等领域有广泛应用。通过FPGA实现LDPC码的译码器能够大大提高纠错性能,并且具有低功耗和高速率的优点。二、进展情况1.熟悉LDPC码译码原理和算法,并对算法进行优化改进,提高译码性能。2.完成对FPGA硬件平台的研究,包括了解FPGA的搭建方式、硬件资源分配和约束文件的编写等。3.架

基于FPGA的多元LDPC码编译码器的设计.docx

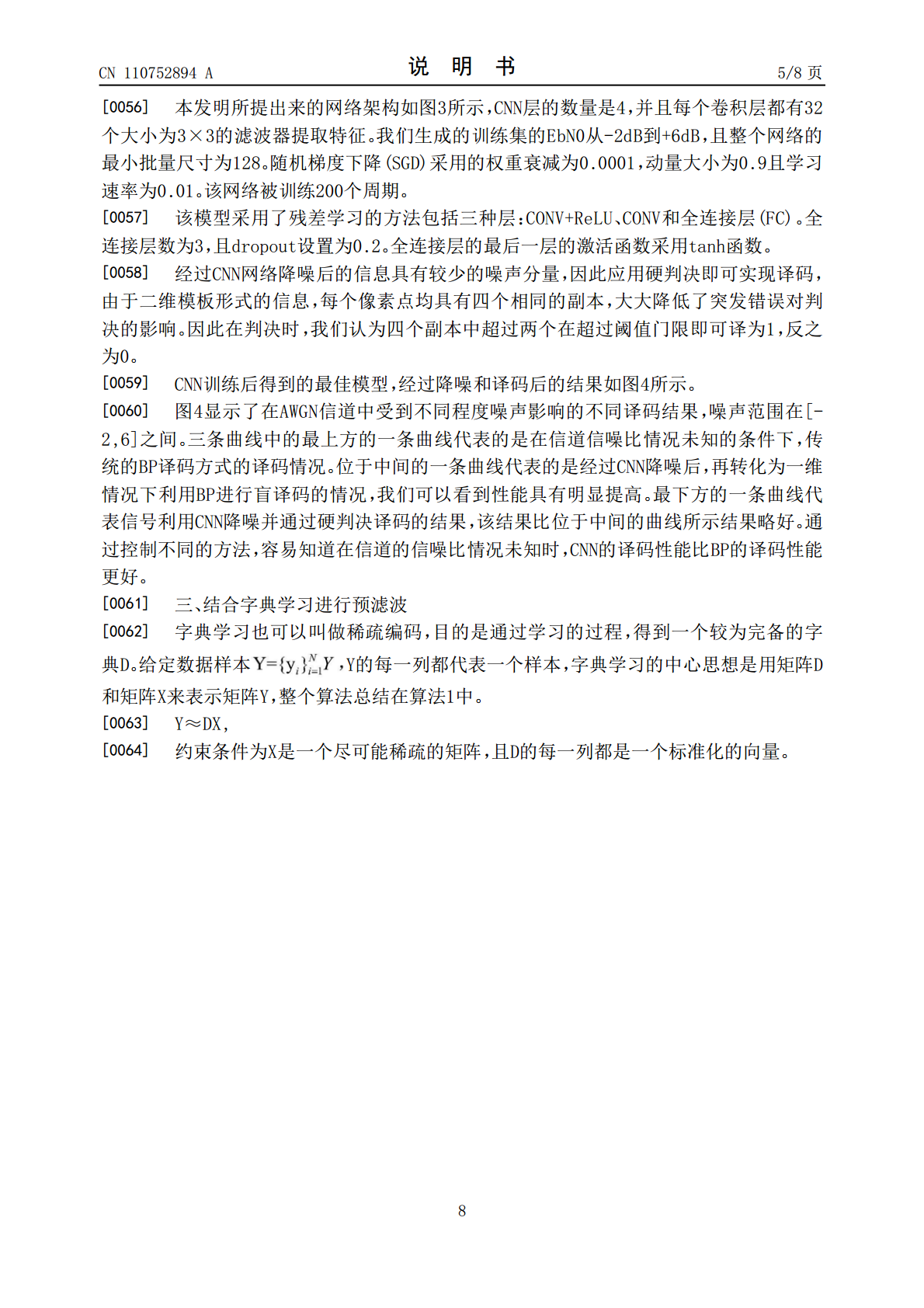

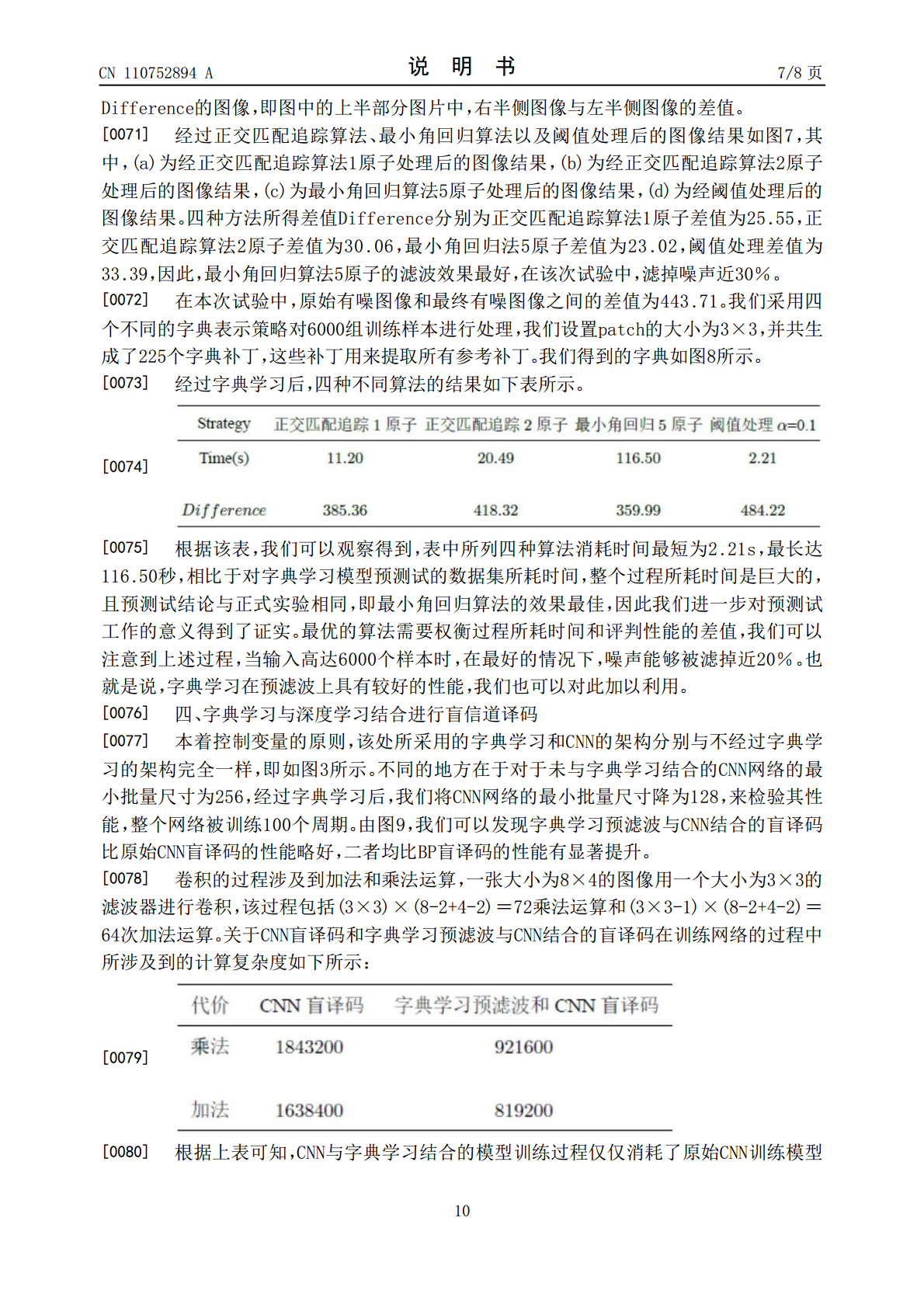

基于FPGA的多元LDPC码编译码器的设计基于FPGA的多元LDPC码编译码器设计摘要:随着通信技术的发展,低密度奇偶校验码(LDPC码)作为一种高效的前向纠错码,被广泛应用于无线通信和存储设备中。本文基于FPGA实现了多元LDPC码编译码器的设计。首先介绍了LDPC码的基本原理和结构,然后详细描述了多元LDPC码编译码器的设计思路和实现流程。在设计过程中,采用了迭代求解和循环移位技术来提高编译码器的性能。最后,通过实验验证了多元LDPC码编译码器在FPGA上的正确性和可靠性。关键词:FPGA,LDPC码