数字像素读出电路、像素阵列及图像传感器.pdf

努力****绮亦

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

数字像素读出电路、像素阵列及图像传感器.pdf

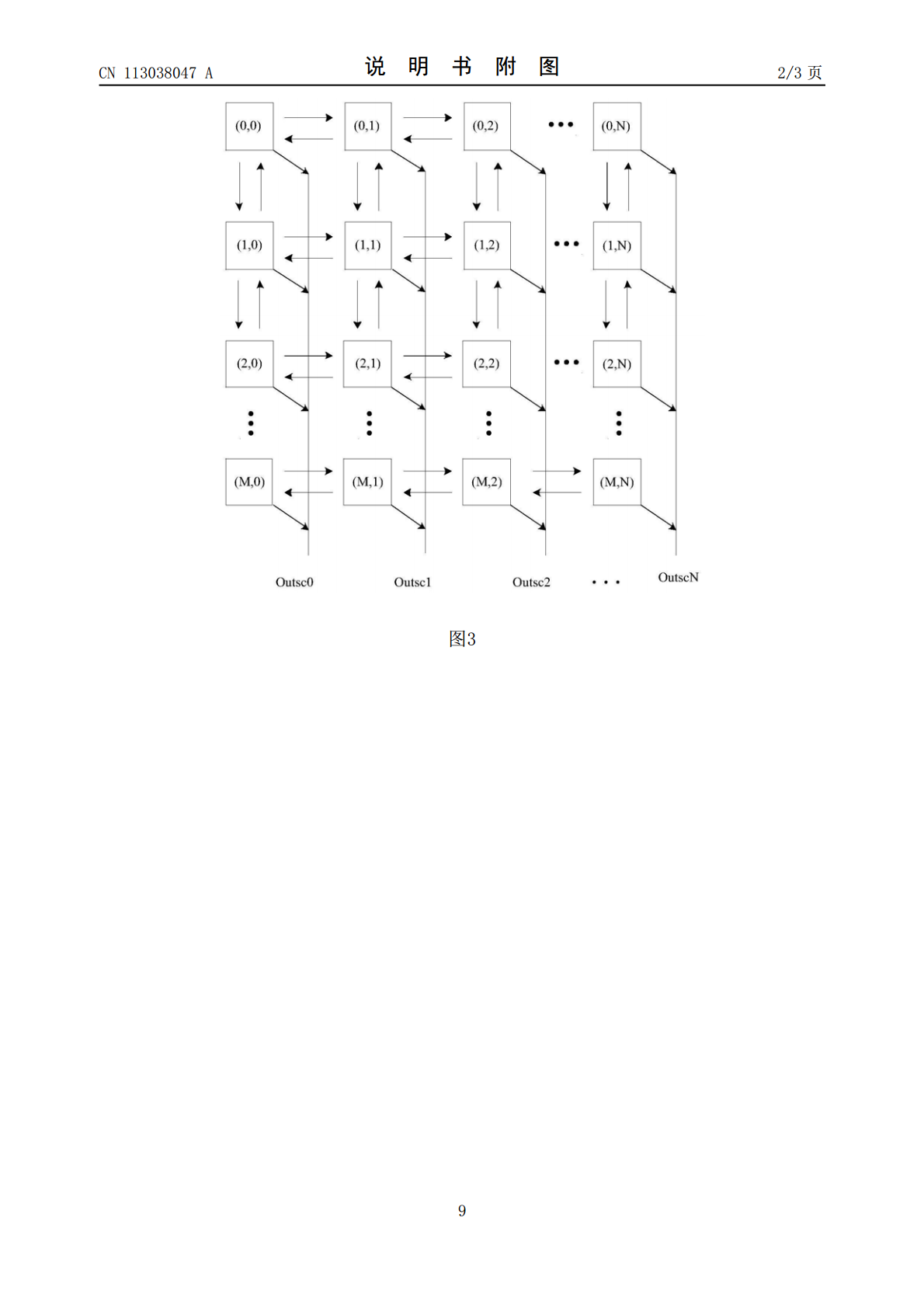

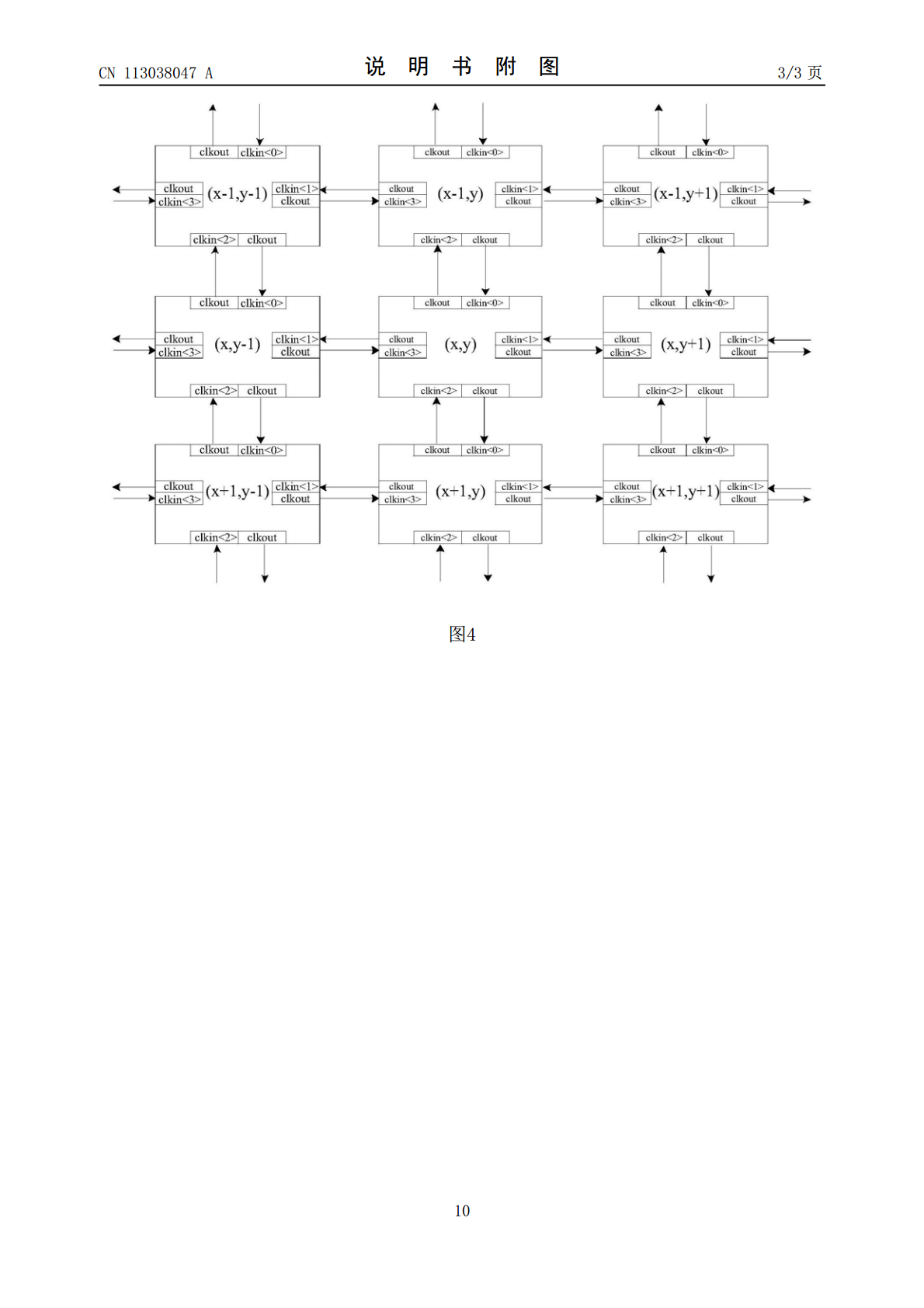

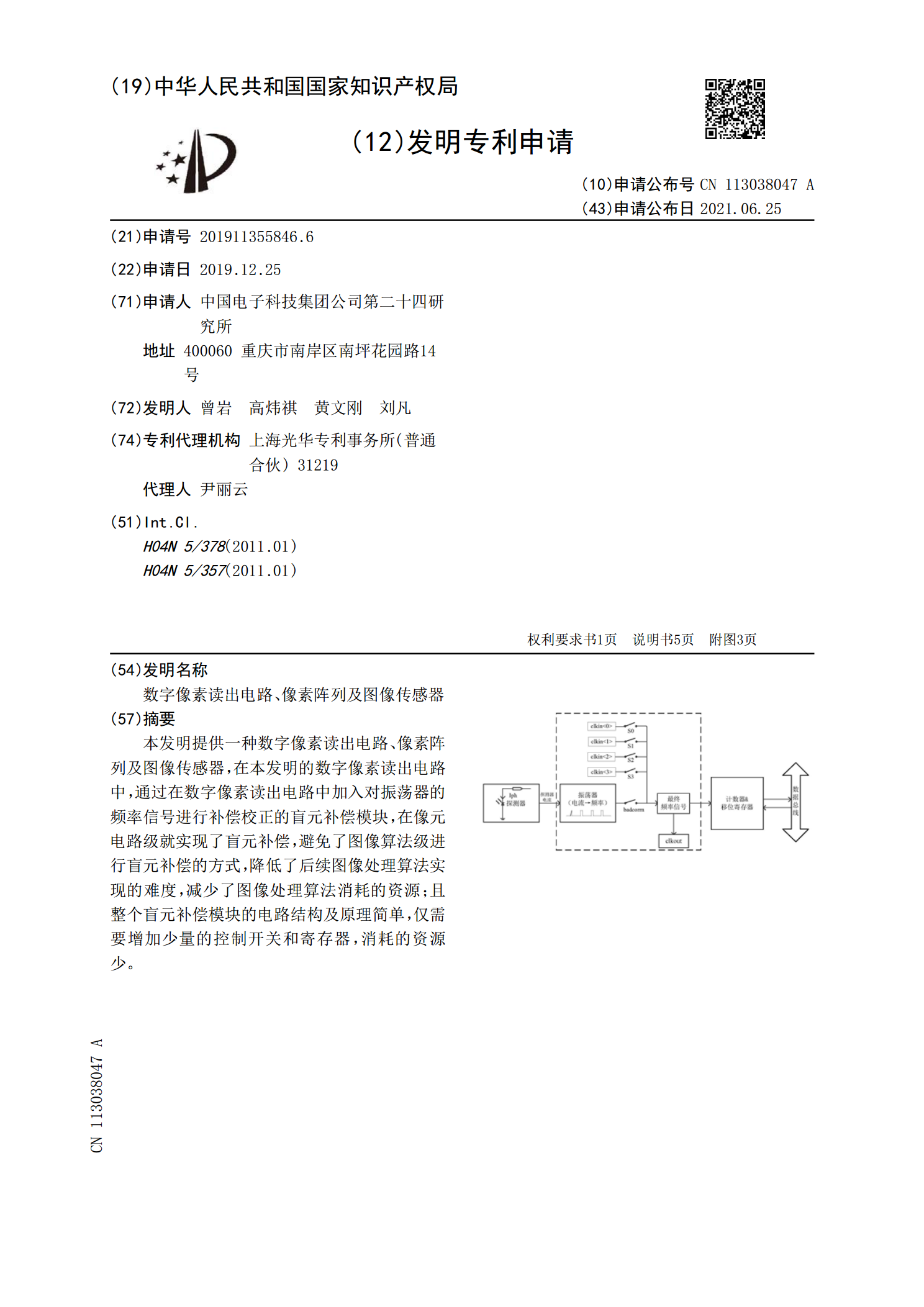

本发明提供一种数字像素读出电路、像素阵列及图像传感器,在本发明的数字像素读出电路中,通过在数字像素读出电路中加入对振荡器的频率信号进行补偿校正的盲元补偿模块,在像元电路级就实现了盲元补偿,避免了图像算法级进行盲元补偿的方式,降低了后续图像处理算法实现的难度,减少了图像处理算法消耗的资源;且整个盲元补偿模块的电路结构及原理简单,仅需要增加少量的控制开关和寄存器,消耗的资源少。

一种CMOS图像传感器的像素阵列读出结构.pdf

本发明公开了一种CMOS图像传感器像素阵列的读出结构,包括CMOS图像传感器像素阵列和设置在所述CMOS图像传感器像素阵列上的积分器电路阵列;还包括电荷释放电路阵列,所述电荷释放电路阵列设置在远离所述积分器电路阵列的一侧,且所述电荷释放电路阵列中的电荷释放电路分别与所述CMOS图像传感器像素阵列中的列信号线电连接。本发明的目的在于提供一种CMOS图像传感器的像素阵列读出结构,通过在CMOS图像传感器像素阵列远离积分器电路阵列的一侧加入电荷释放电路阵列,使得将坏列中像素累积的电荷清除掉,从而使其不影响相邻的

像素级数字化紫外焦平面读出电路的研究.docx

像素级数字化紫外焦平面读出电路的研究摘要:在相机和光谱仪中,紫外焦平面读出电路是不可或缺的组成部分。该文探讨了像素级数字化紫外焦平面读出电路的研究进展,介绍了不同类型的数字化电路,以及它们的优缺点。此外,该文还讨论了未来发展方向,包括数字化技术的提高和更高效的能源利用。1.作用在研究和应用中,紫外焦平面读出电路是非常重要的。其作用是将来自紫外摄像器或光谱仪的信号转换为数字信号,以便进行进一步处理和分析。也就是说,它将可见光和紫外光的信息检测和转换输出给数字处理单元。2.数字化电路类型在当前的数字化技术中,

像素阵列面板与包括像素阵列面板的数字X射线检测器.pdf

公开了一种用于数字X射线检测器的像素阵列面板和数字X射线检测器。该像素阵列面板包括多个像素区域,其中,该像素阵列面板包括:与每个像素区域相对应的第一电极;设置在第一电极上并以矩阵形式布置的多个PIN(P型/I型/N型半导体)层;以及设置在每个PIN层上的第二电极。

像素处理电路及其读取方法、图像传感器.pdf

本发明提供了一种像素处理电路及其读取方法、图像传感器,所述像素处理电路包括:像素阵列、ADC模块、开关选择模块;所述像素阵列中每一列的所述像素单元分别通过输出总线电连设置于所述像素阵列两端的所述开关选择模块的一端;所述开关选择模块的另一端与所述ADC模块中的一个所述模数转换器电连,且每一个所述开关选择模块仅电连所述ADC模块中的两个相对应的所述模数转换器;所述像素阵列包括拜耳阵列。本发明通过控制开关选择模块的状态实现经过Gr通道、Gb通道的像素信号都经过输出总线同一端侧的ADC转换,保证了Gr通道、Gb通