一种半导体结构的制备方法、半导体结构和电容结构.pdf

骊蓉****23

亲,该文档总共17页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种半导体结构的制备方法、半导体结构和电容结构.pdf

本申请实施例提供了一种半导体结构的制备方法、半导体结构和电容结构,该制备方法包括:提供基底,基底表面具有多个盲孔或沟槽;于多个盲孔或沟槽内形成填充层,填充层的顶面与基底的顶面平齐;于填充层的顶面和基底的顶面上形成覆盖层;其中,覆盖层包括至少一个叠层结构,一个叠层结构包括一层第一覆盖层和一层第二覆盖层,且第一覆盖层的掺杂材料源和第二覆盖层的掺杂材料源不同。这样,采用包含第一覆盖层和第二覆盖层的叠层结构实现覆盖层,不仅能够避免沉积过程中的应力累积问题,而且改善了覆盖层的均匀度和表面粗糙度,还能够平衡结构阻值,

电容结构及其制备方法、半导体结构.pdf

本申请涉及一种电容结构及其制备方法、半导体结构。电容结构包括:第一极板;介质叠层,包括依次层叠设置的第一介质层、第二介质层及第三介质层,所述第一介质层位于所述第一极板的表面;其中,所述第一介质层的折射率与所述第三介质层的折射率均低于所述第二介质层的折射率;第二极板,位于所述第三介质层远离所述第一极板的表面。本申请的电容结构的介质叠层的具备较高的介电常数值,电容密度得到提升,第一介质层的折射率与第三介质层的折射率均低于第二介质层的折射率,使得直接与电容上下极板接触的介质层的应力较低,解决了提升电容密度造成介

一种电容结构、半导体器件以及电容结构制备方法.pdf

本申请公开了一种电容结构、半导体器件以及电容结构制备方法,通过在柱状结构的下电极外侧壁设置支撑结构,支撑结构包括支撑下电极上部区域的顶部支撑结构,该顶部支撑结构至少包括第一支撑层以及与第一支撑层材料不同的第二支撑层,第一支撑层的下表面被设置为与第二支撑层的上表面接触,并且第一支撑层与第二支撑层的接触界面低于下电极的顶部,第一支撑层的上表面高于下电极的顶部;再形成有覆盖下电极与支撑结构的电容介电层以及覆盖电容介电层的上电极,可以在满足下电极在垂直方向上延伸的高度的同时,降低漏电率,以及避免在对下电极的顶部支

半导体结构的制备方法和半导体结构.pdf

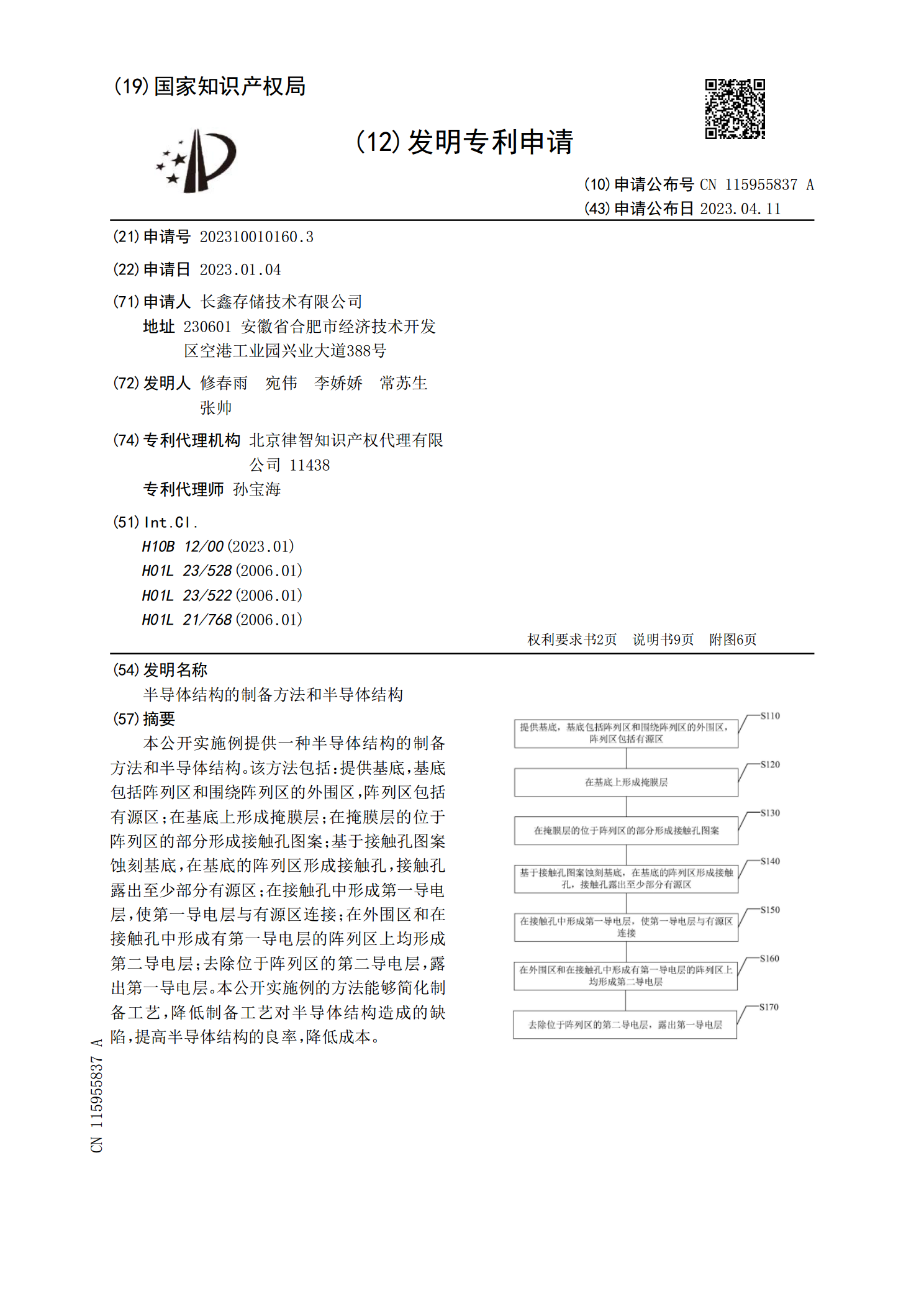

本公开实施例提供一种半导体结构的制备方法和半导体结构。该方法包括:提供基底,基底包括阵列区和围绕阵列区的外围区,阵列区包括有源区;在基底上形成掩膜层;在掩膜层的位于阵列区的部分形成接触孔图案;基于接触孔图案蚀刻基底,在基底的阵列区形成接触孔,接触孔露出至少部分有源区;在接触孔中形成第一导电层,使第一导电层与有源区连接;在外围区和在接触孔中形成有第一导电层的阵列区上均形成第二导电层;去除位于阵列区的第二导电层,露出第一导电层。本公开实施例的方法能够简化制备工艺,降低制备工艺对半导体结构造成的缺陷,提高半导体

半导体结构和半导体结构的制备方法.pdf

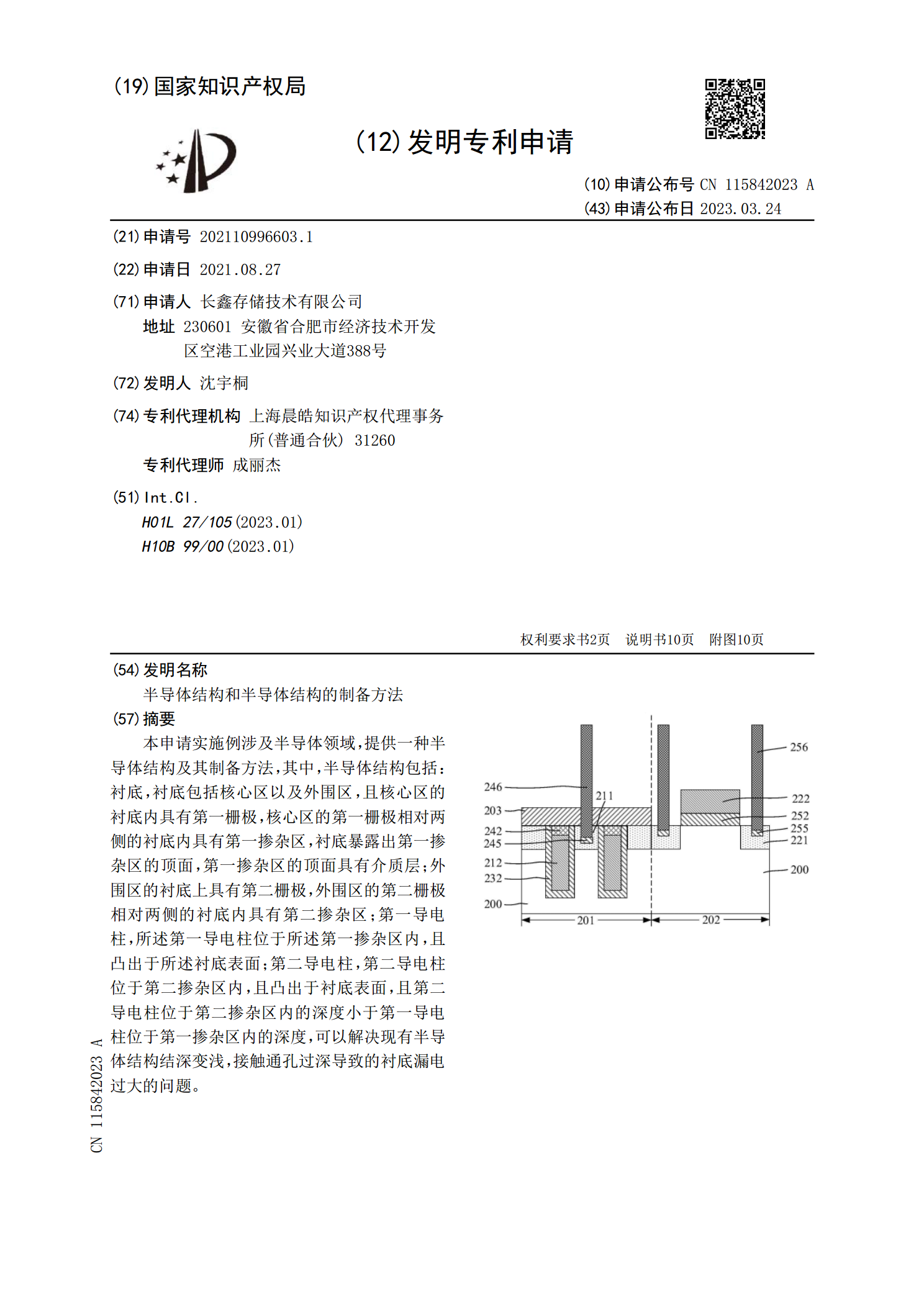

本申请实施例涉及半导体领域,提供一种半导体结构及其制备方法,其中,半导体结构包括:衬底,衬底包括核心区以及外围区,且核心区的衬底内具有第一栅极,核心区的第一栅极相对两侧的衬底内具有第一掺杂区,衬底暴露出第一掺杂区的顶面,第一掺杂区的顶面具有介质层;外围区的衬底上具有第二栅极,外围区的第二栅极相对两侧的衬底内具有第二掺杂区;第一导电柱,所述第一导电柱位于所述第一掺杂区内,且凸出于所述衬底表面;第二导电柱,第二导电柱位于第二掺杂区内,且凸出于衬底表面,且第二导电柱位于第二掺杂区内的深度小于第一导电柱位于第一掺