一种制作电容触摸屏的方法.pdf

睿达****的的

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种制作电容触摸屏的方法.pdf

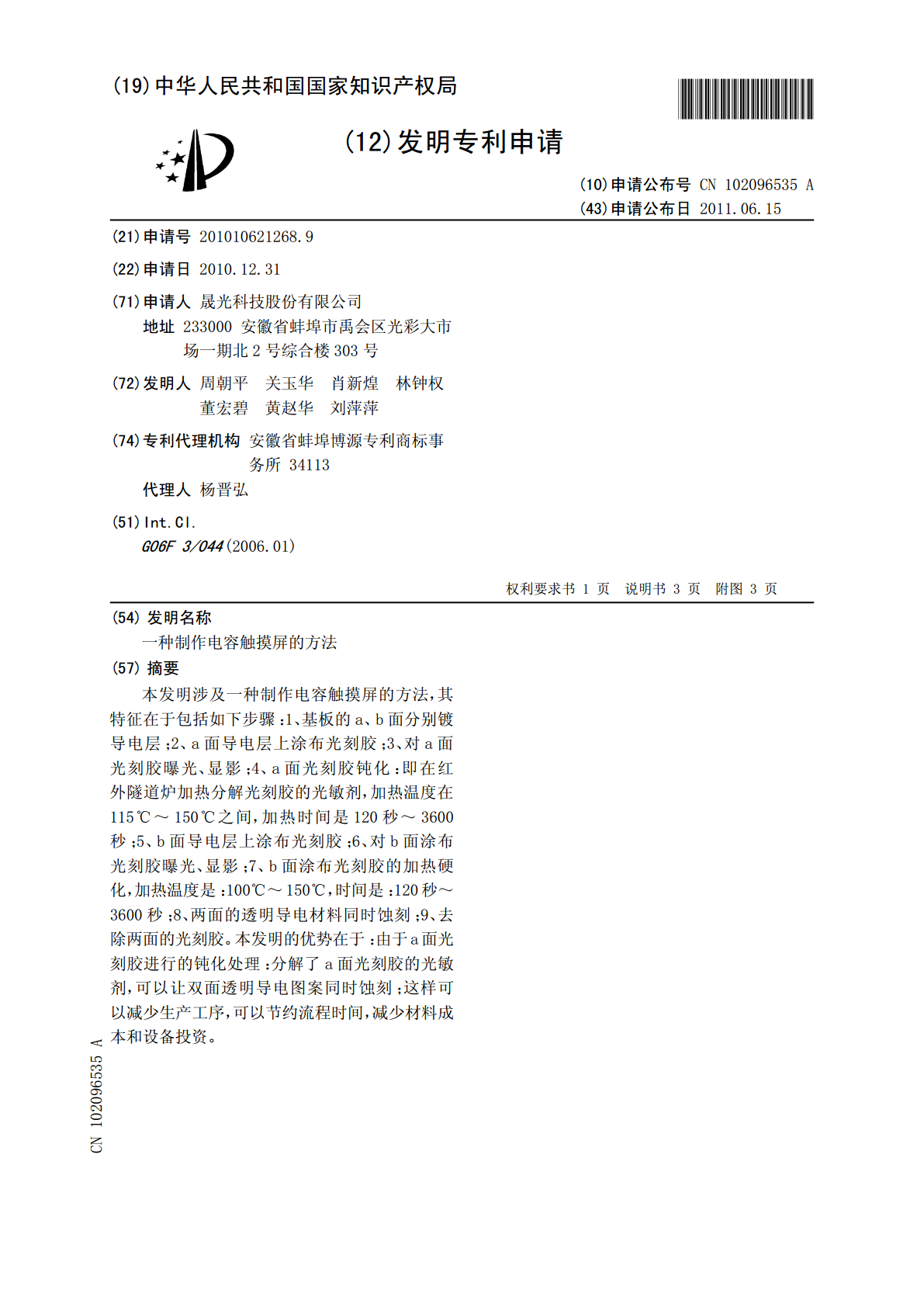

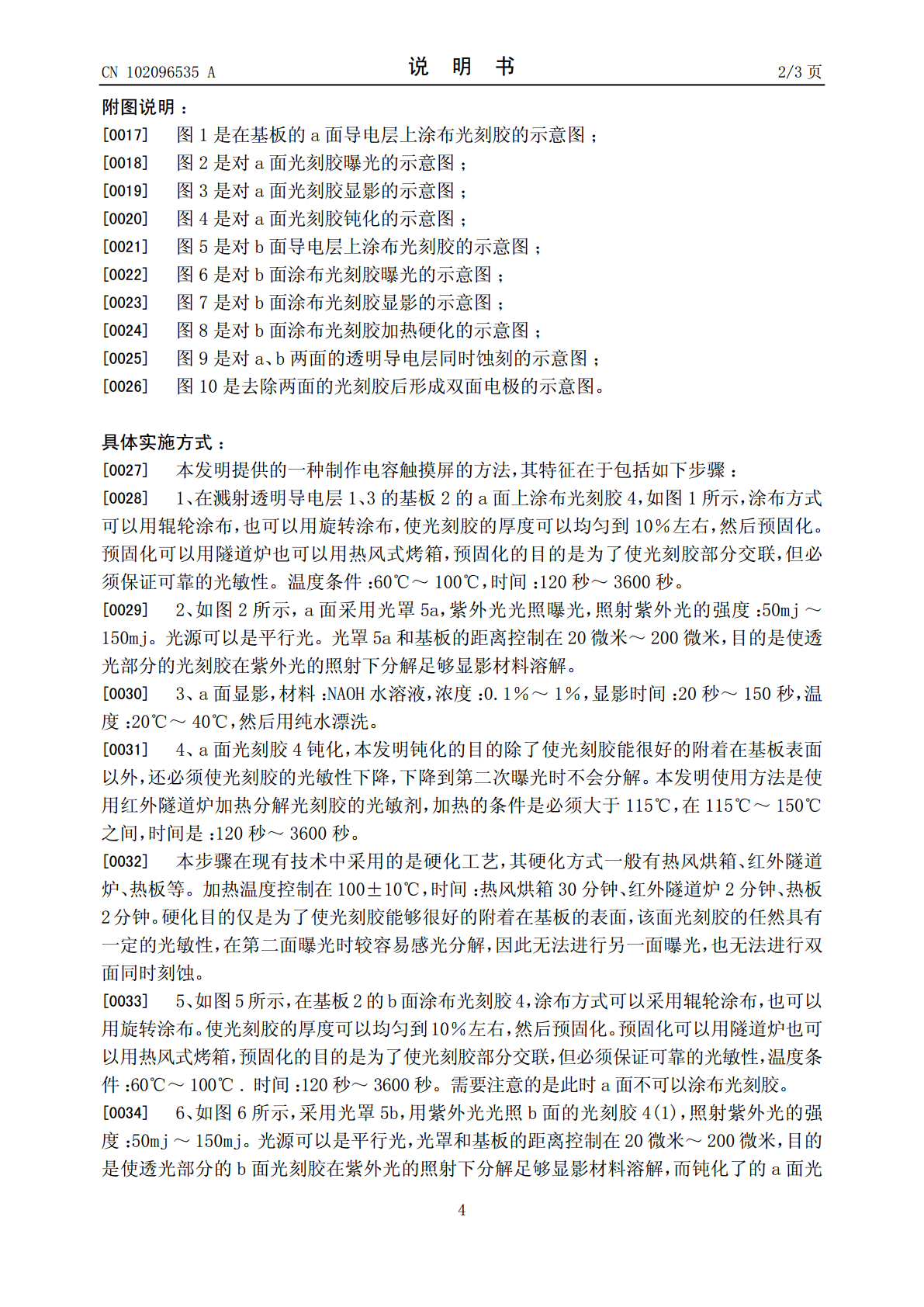

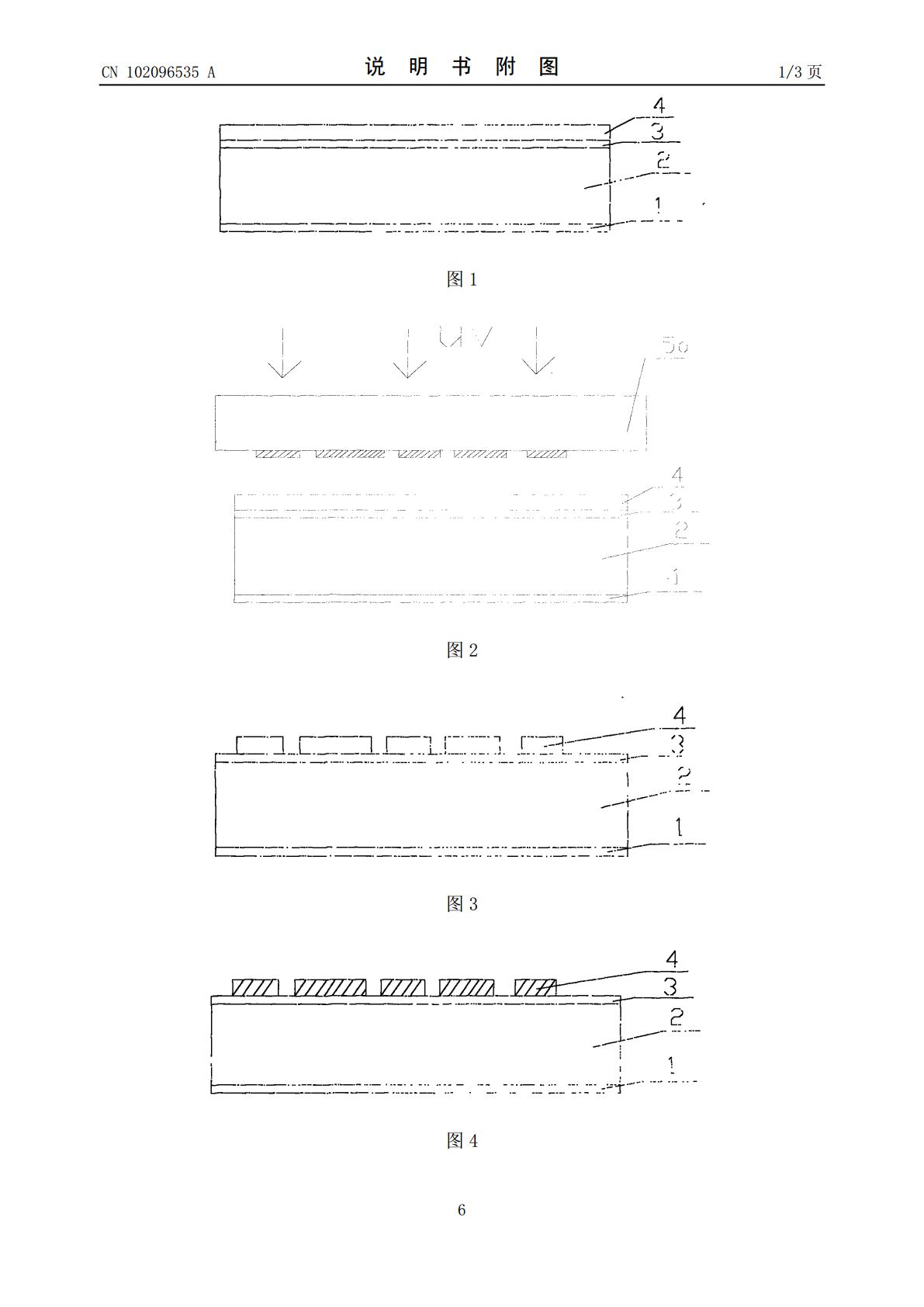

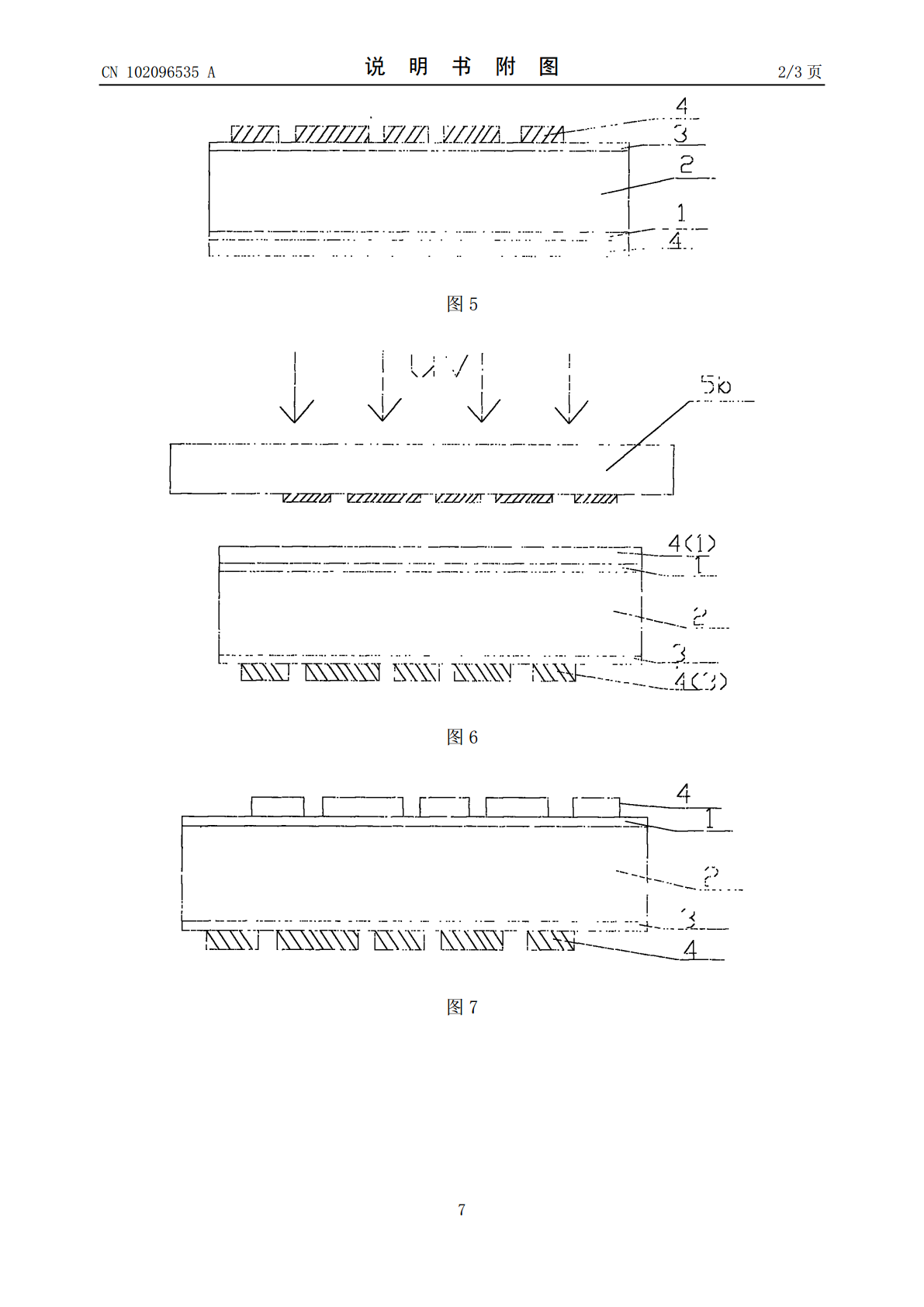

本发明涉及一种制作电容触摸屏的方法,其特征在于包括如下步骤:1、基板的a、b面分别镀导电层;2、a面导电层上涂布光刻胶;3、对a面光刻胶曝光、显影;4、a面光刻胶钝化:即在红外隧道炉加热分解光刻胶的光敏剂,加热温度在115℃~150℃之间,加热时间是120秒~3600秒;5、b面导电层上涂布光刻胶;6、对b面涂布光刻胶曝光、显影;7、b面涂布光刻胶的加热硬化,加热温度是:100℃~150℃,时间是:120秒~3600秒;8、两面的透明导电材料同时蚀刻;9、去除两面的光刻胶。本发明的优势在于:由于a面光刻胶

一种电容式触摸屏及其制作方法.pdf

本发明公开了一种电容式触摸屏及其制作方法,包括将底层具有黑化层的导电金属层设置于基板上;依据预设图案对导电金属层和黑化层进行蚀刻处理,得到各条金属网格走线,并保留预设边框区域内的黑化层;在经过蚀刻处理后的导电金属层上与预设边框区域对应的区域设置黑色油墨层。本申请在制作电容式触摸屏时,无需在基板上设置第一层黑框油墨,通过在对导电金属层和黑化层进行蚀刻时保留预设边框区域内的黑化层,采用预设边框区域内的黑化层代替第一层黑框油墨,不仅简化了制作流程,而且还节约了成本,降低了金属网格走线的爬坡风险,有利于提高产品的

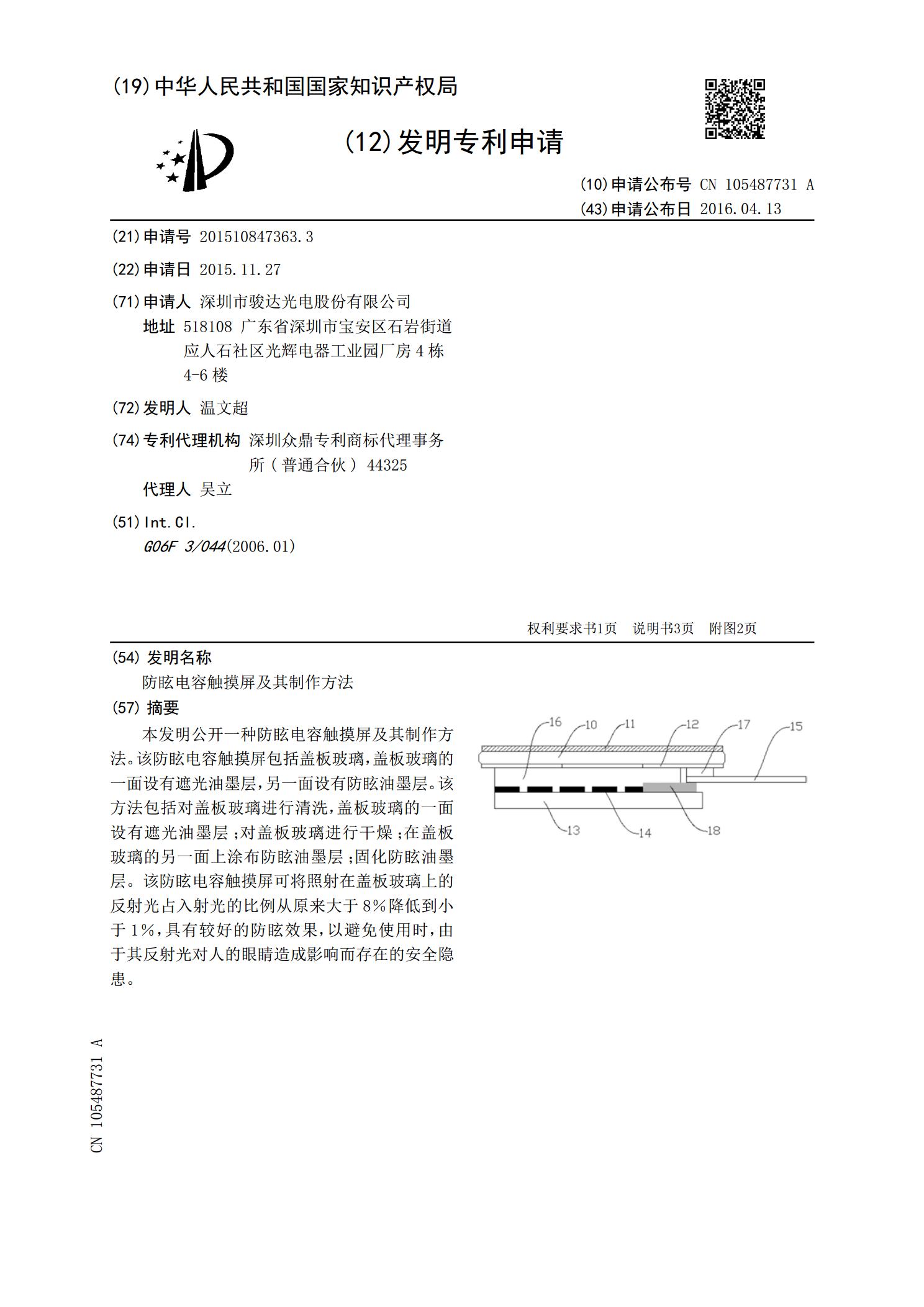

防眩电容触摸屏及其制作方法.pdf

本发明公开一种防眩电容触摸屏及其制作方法。该防眩电容触摸屏包括盖板玻璃,盖板玻璃的一面设有遮光油墨层,另一面设有防眩油墨层。该方法包括对盖板玻璃进行清洗,盖板玻璃的一面设有遮光油墨层;对盖板玻璃进行干燥;在盖板玻璃的另一面上涂布防眩油墨层;固化防眩油墨层。该防眩电容触摸屏可将照射在盖板玻璃上的反射光占入射光的比例从原来大于8%降低到小于1%,具有较好的防眩效果,以避免使用时,由于其反射光对人的眼睛造成影响而存在的安全隐患。

GFF结构的电容触摸屏及其制作方法.pdf

本发明公开一种GFF结构的电容触摸屏及其制作方法。该GFF结构的电容触摸屏包括第一ITO薄膜层、第二ITO薄膜层和柔性线路板;第一ITO薄膜层上设有X方向ITO线路,X方向ITO线路包括一体成型的X方向ITO电极线和X方向ITO引出线;第二ITO薄膜层上设有Y方向ITO线路,Y方向ITO线路包括一体成型的Y方向ITO电极线和Y方向ITO引出线;X方向ITO引出线和Y方向ITO引出线与柔性线路板相连。该GFF结构的电容触摸屏无需制作银浆线以将ITO电极线与柔性线路板相连,不存在ITO线与银浆线套版问题,结构

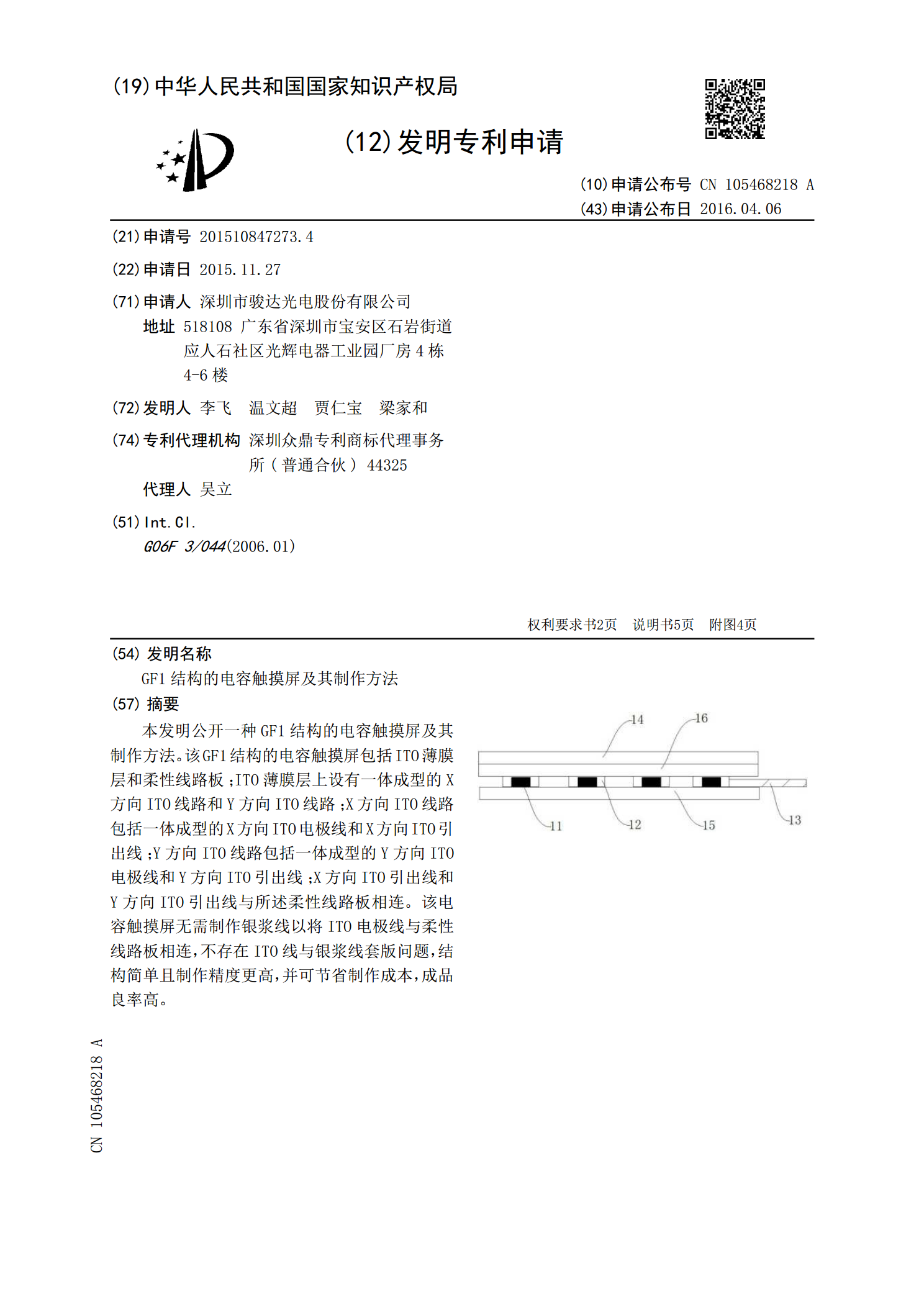

GF1结构的电容触摸屏及其制作方法.pdf

本发明公开一种GF1结构的电容触摸屏及其制作方法。该GF1结构的电容触摸屏包括ITO薄膜层和柔性线路板;ITO薄膜层上设有一体成型的X方向ITO线路和Y方向ITO线路;X方向ITO线路包括一体成型的X方向ITO电极线和X方向ITO引出线;Y方向ITO线路包括一体成型的Y方向ITO电极线和Y方向ITO引出线;X方向ITO引出线和Y方向ITO引出线与所述柔性线路板相连。该电容触摸屏无需制作银浆线以将ITO电极线与柔性线路板相连,不存在ITO线与银浆线套版问题,结构简单且制作精度更高,并可节省制作成本,成品良率