一种改善多晶硅栅极刻蚀中有源区漏电的方法.pdf

山柳****魔王

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种改善多晶硅栅极刻蚀中有源区漏电的方法.pdf

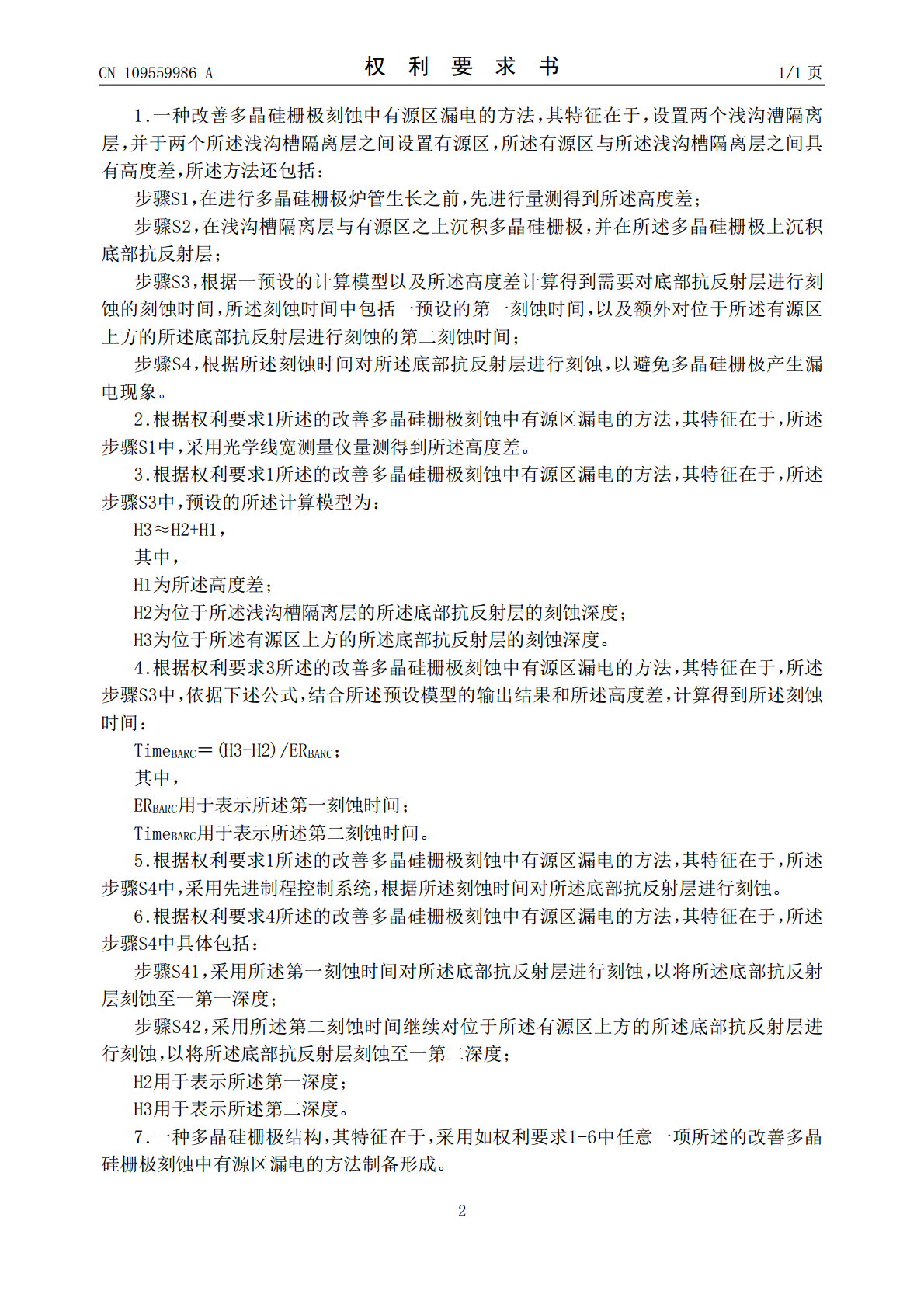

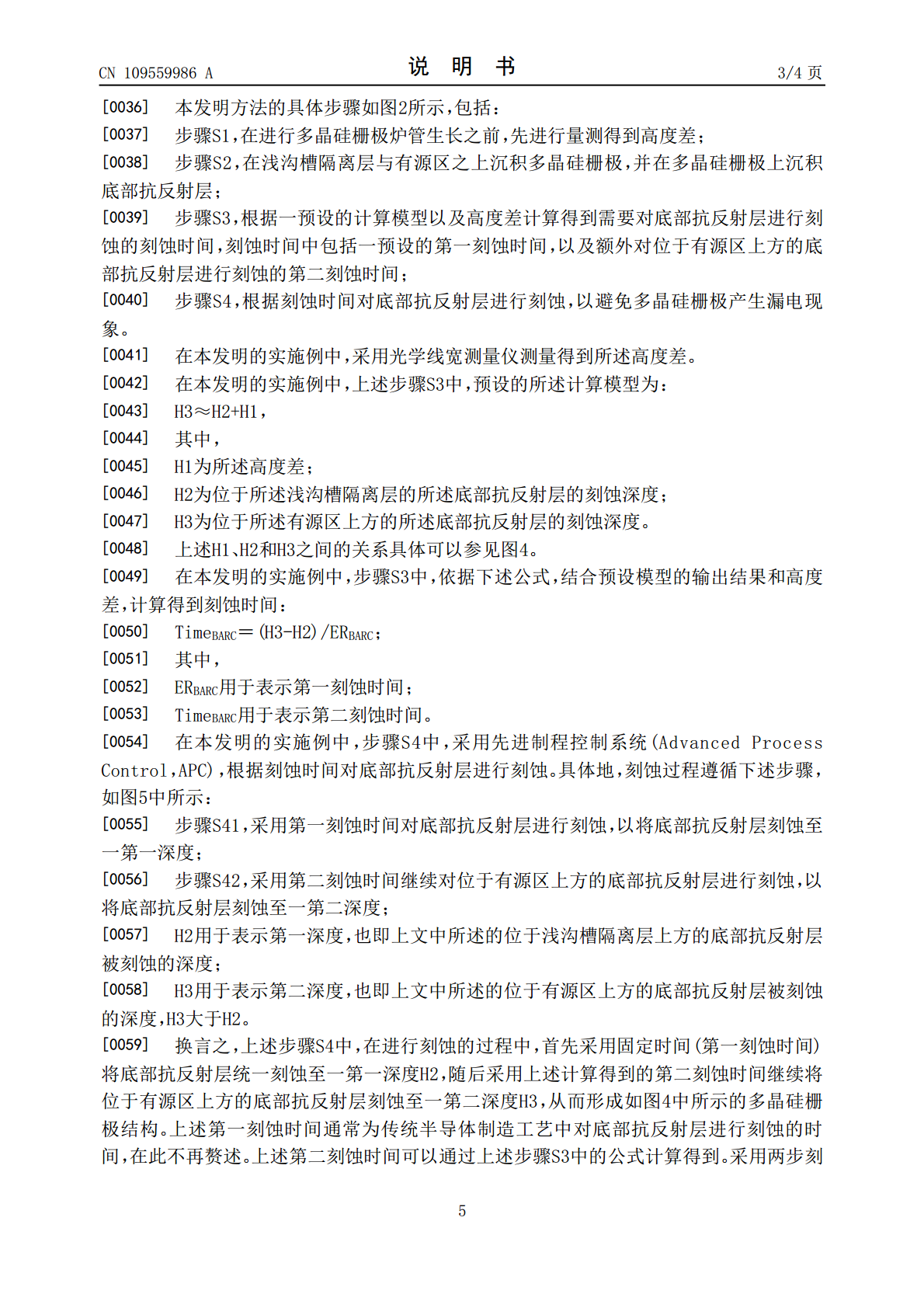

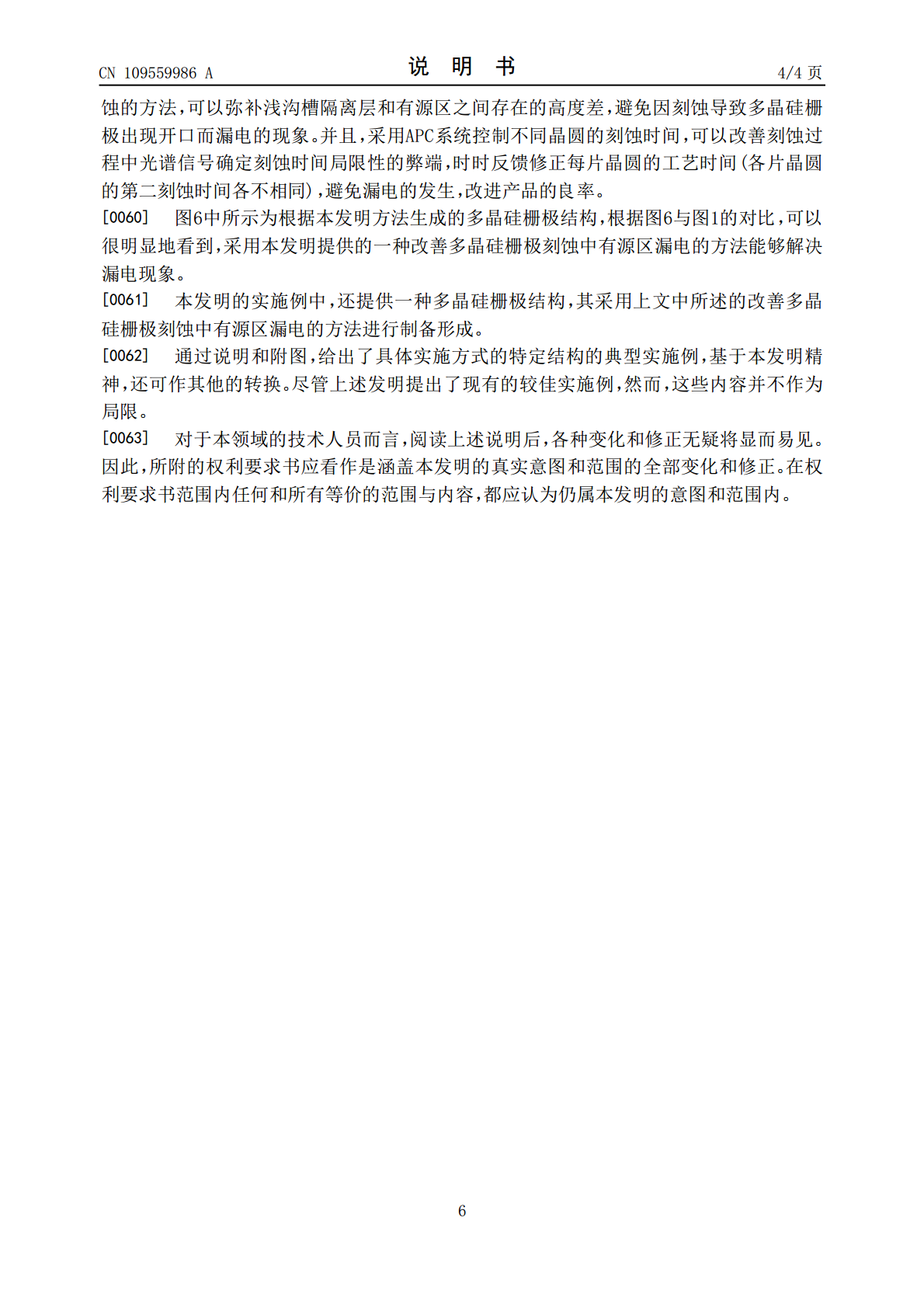

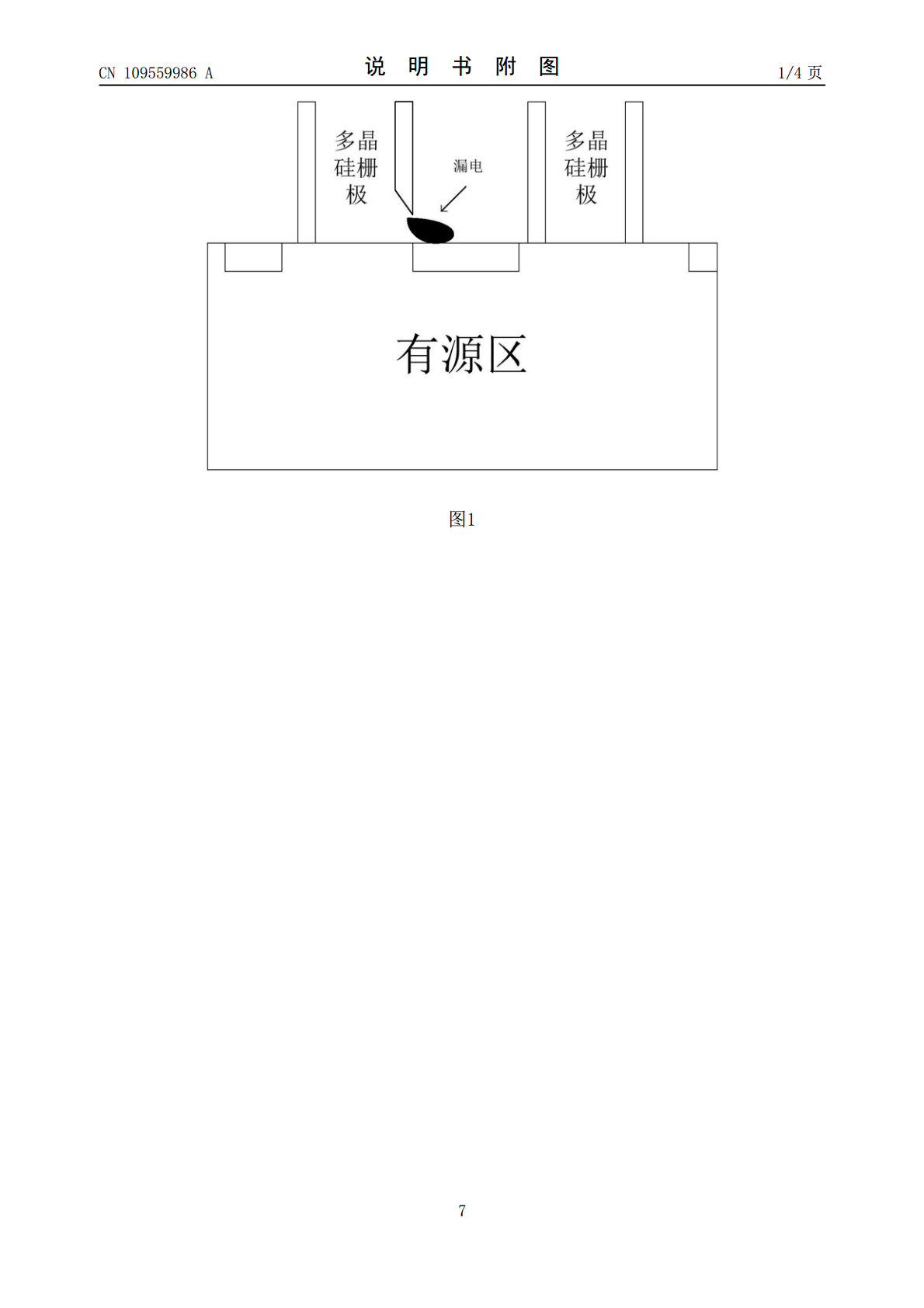

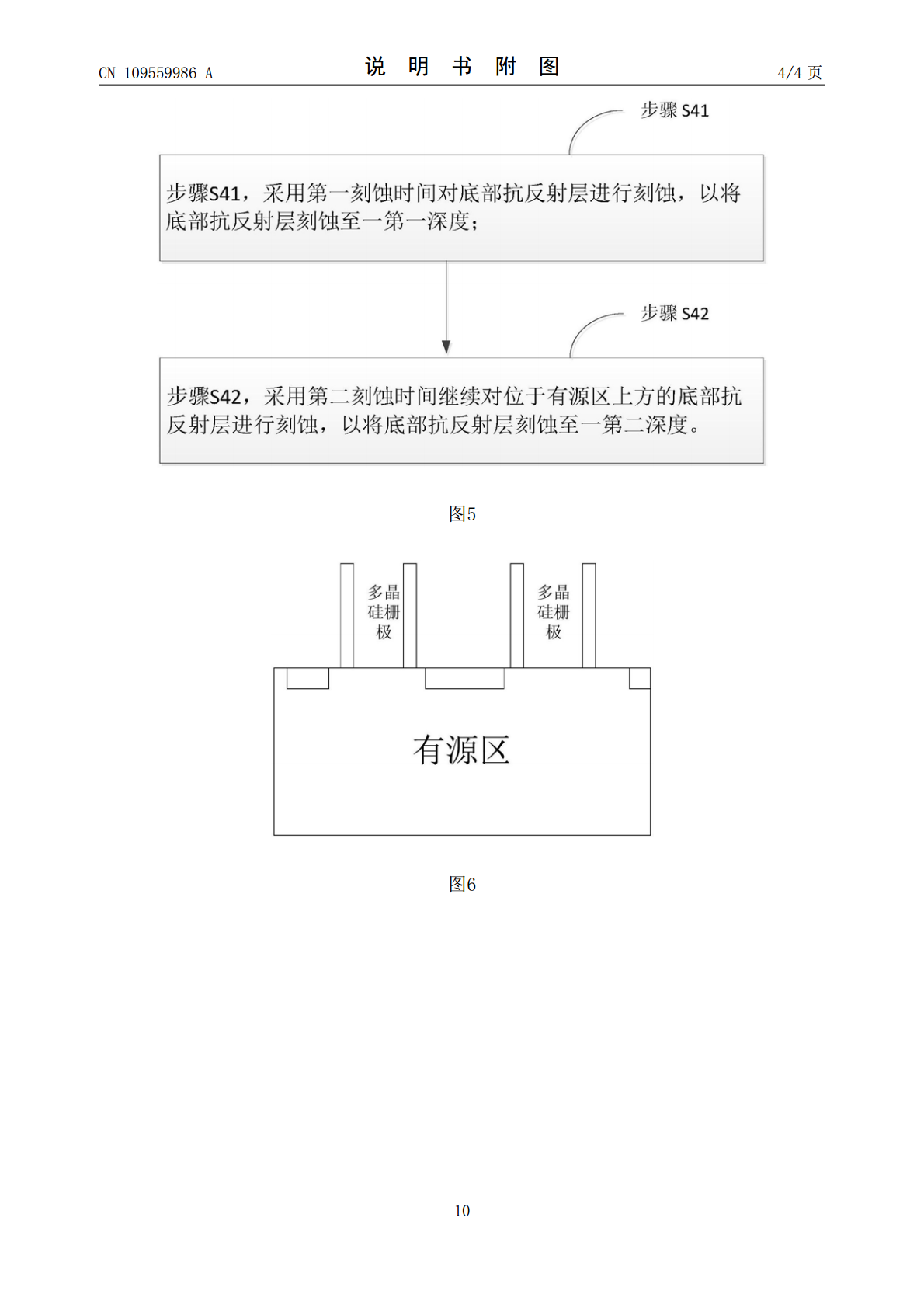

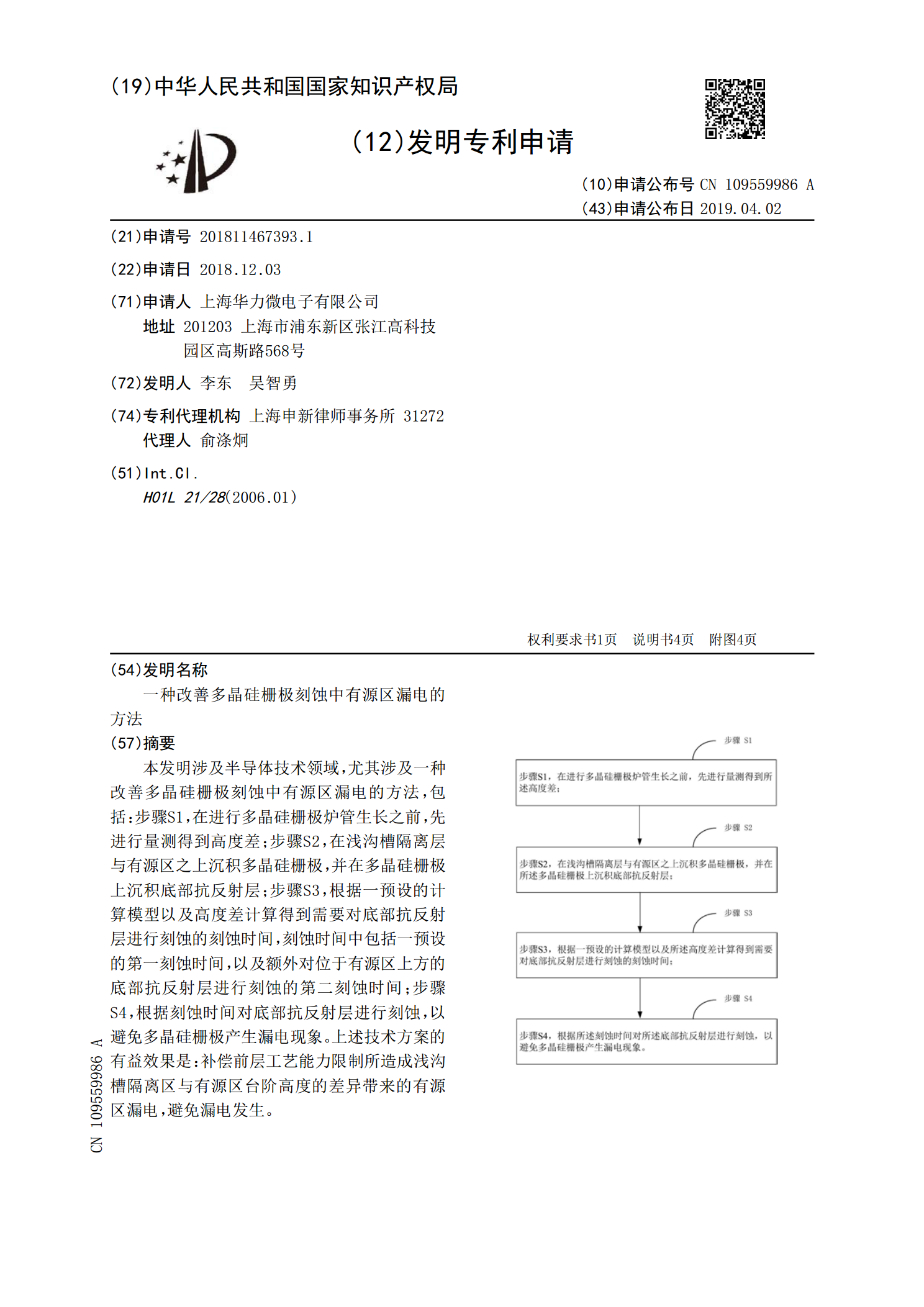

本发明涉及半导体技术领域,尤其涉及一种改善多晶硅栅极刻蚀中有源区漏电的方法,包括:步骤S1,在进行多晶硅栅极炉管生长之前,先进行量测得到高度差;步骤S2,在浅沟槽隔离层与有源区之上沉积多晶硅栅极,并在多晶硅栅极上沉积底部抗反射层;步骤S3,根据一预设的计算模型以及高度差计算得到需要对底部抗反射层进行刻蚀的刻蚀时间,刻蚀时间中包括一预设的第一刻蚀时间,以及额外对位于有源区上方的底部抗反射层进行刻蚀的第二刻蚀时间;步骤S4,根据刻蚀时间对底部抗反射层进行刻蚀,以避免多晶硅栅极产生漏电现象。上述技术方案的有益效

一种检测多晶硅栅极刻蚀能力的方法.pdf

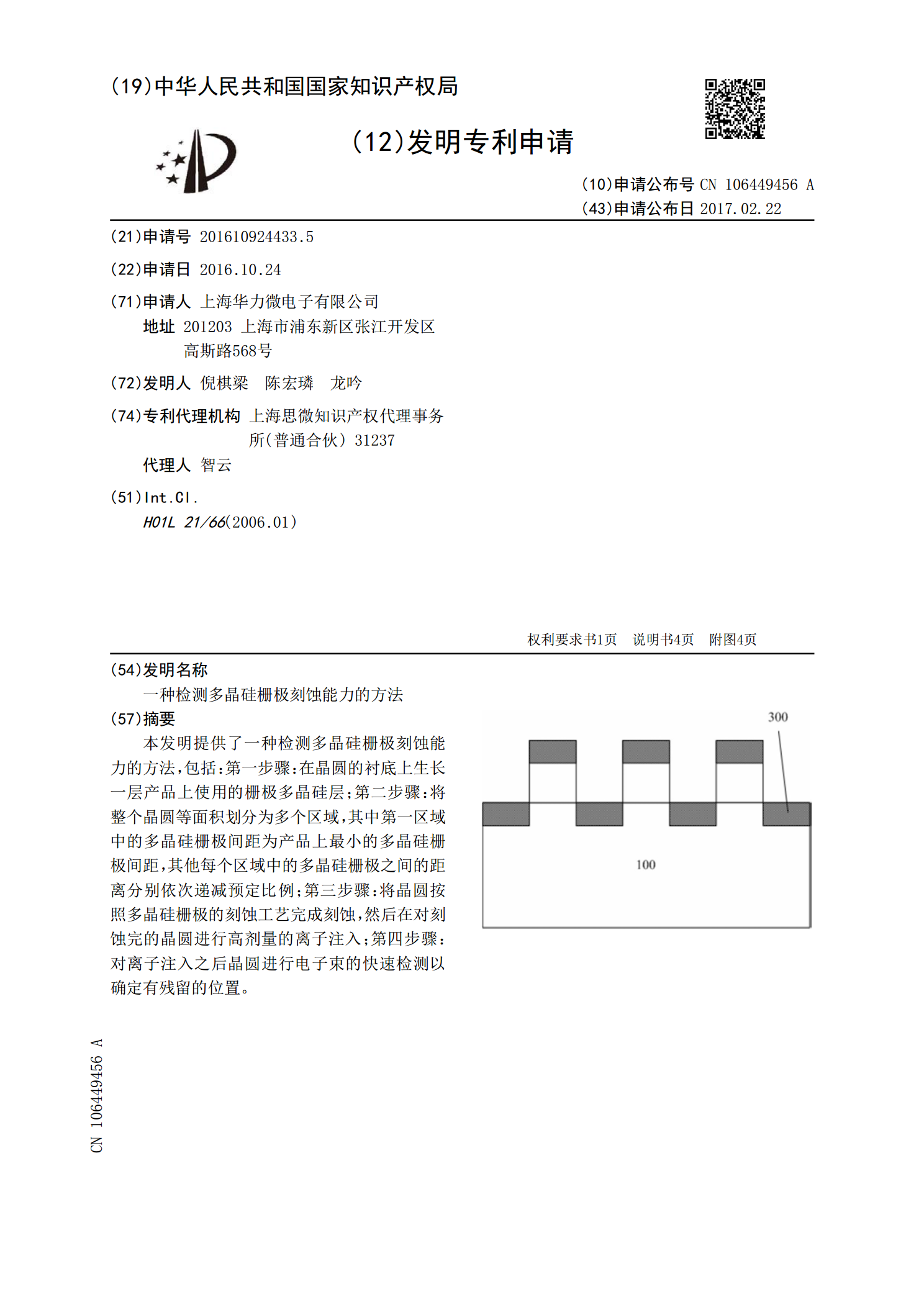

本发明提供了一种检测多晶硅栅极刻蚀能力的方法,包括:第一步骤:在晶圆的衬底上生长一层产品上使用的栅极多晶硅层;第二步骤:将整个晶圆等面积划分为多个区域,其中第一区域中的多晶硅栅极间距为产品上最小的多晶硅栅极间距,其他每个区域中的多晶硅栅极之间的距离分别依次递减预定比例;第三步骤:将晶圆按照多晶硅栅极的刻蚀工艺完成刻蚀,然后在对刻蚀完的晶圆进行高剂量的离子注入;第四步骤:对离子注入之后晶圆进行电子束的快速检测以确定有残留的位置。

一种多晶硅栅极的制造方法及多晶硅栅极.pdf

本发明提供了一种多晶硅栅极的制造方法及多晶硅栅极,其中,多晶硅栅极的制造方法包括:在衬底上依次生成栅氧化层、多晶硅层和氮化硅层;对所述氮化硅层和所述多晶硅层进行光刻和刻蚀,且所述多晶硅层上被刻蚀的位置保留预设厚度的余量;对外露的所述多晶硅层进行氧化,得到氧化层;去除所述氮化硅层,并在露出的所述多晶硅层上生成硅化物,形成多晶硅栅极。本发明提供的方案通过在刻蚀多晶硅时保留一定的余量,然后通过氧化将其转化为二氧化硅(氧化层),能够保证多晶硅层下方任何位置处的栅氧化层都不会被损伤到,简化了制作工艺;同时保留了完整

一种多晶硅刻蚀方法.pdf

本发明提供一种多晶硅刻蚀方法,包括以下步骤:S1:在多晶硅层表面形成SiN层,并刻蚀所述SiN层使其图形化,得到SiN硬掩膜层;S2:在所述SiN硬掩膜层周围未被刻蚀彻底的SiN残留颗粒与所述多晶硅层之间形成氧化层;S3:采用湿法腐蚀去除所述氧化层,使所述SiN残留颗粒因悬空而脱离所述多晶硅层;S4:以所述SiN硬掩膜层作为掩模对所述多晶硅层进行刻蚀。本发明避免了因氮化硅残留颗粒的遮挡阻碍后续多晶硅刻蚀,极大地降低了多晶硅残留缺陷的产生。本发明的多晶硅刻蚀方法无需增加光刻次数,对后续工艺几乎没有影响,并且

多晶硅刻蚀方法.pdf

本发明公开了一种多晶硅刻蚀方法,该方法包括:提供具有第一区域和第二区域的晶片,所述第一区域形成有第一多晶硅层,所述第二区域形成有第二多晶硅层,其中,第一多晶硅层包括非掺杂层以及位于非掺杂层上的掺杂层;在第一多晶硅层和第二多晶硅层上形成图案化光阻层;执行第一刻蚀步骤,以去除未被图案化光阻层覆盖的部分第一多晶硅层和部分第二多晶硅层;执行第二刻蚀步骤,以去除未被图案化光阻层覆盖的剩余的第一多晶硅层和剩余的第二多晶硅层;在所述第一刻蚀步骤中,未被图案化光阻层覆盖的掺杂层被完全去除,从而确保形成具有垂直轮廓的栅极,