管式炉及半导体掺杂膜层制备方法.pdf

哲妍****彩妍

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

管式炉及半导体掺杂膜层制备方法.pdf

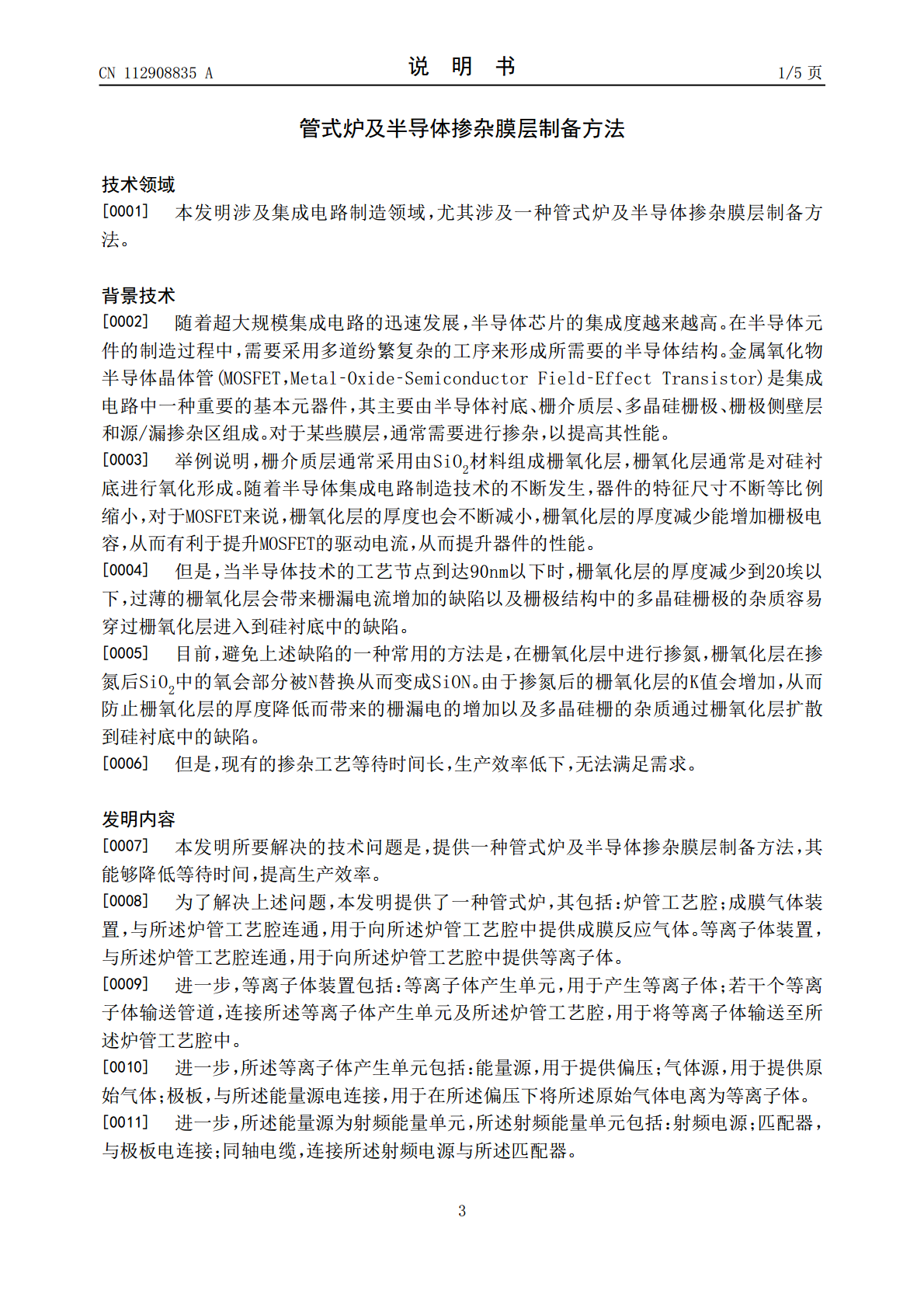

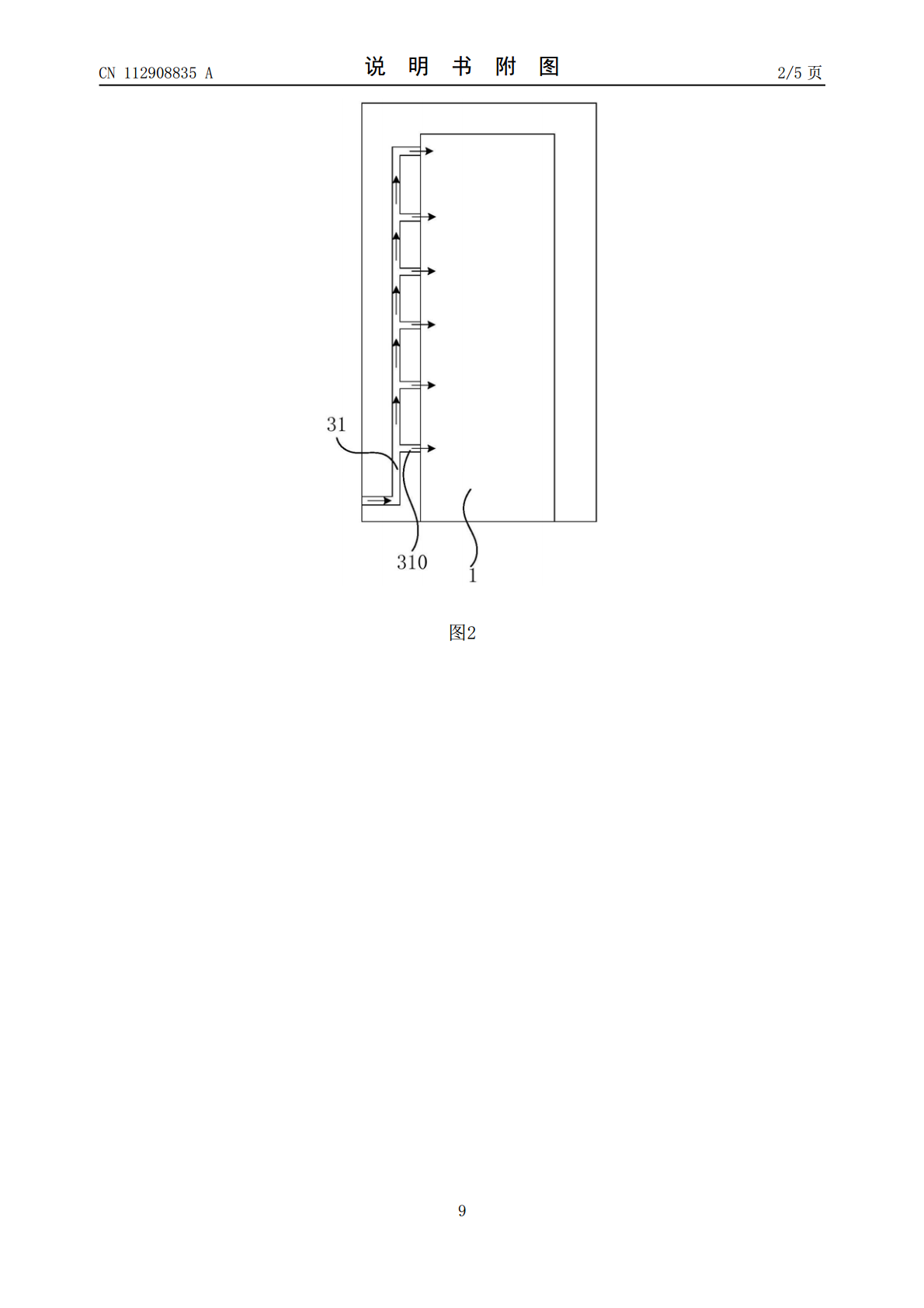

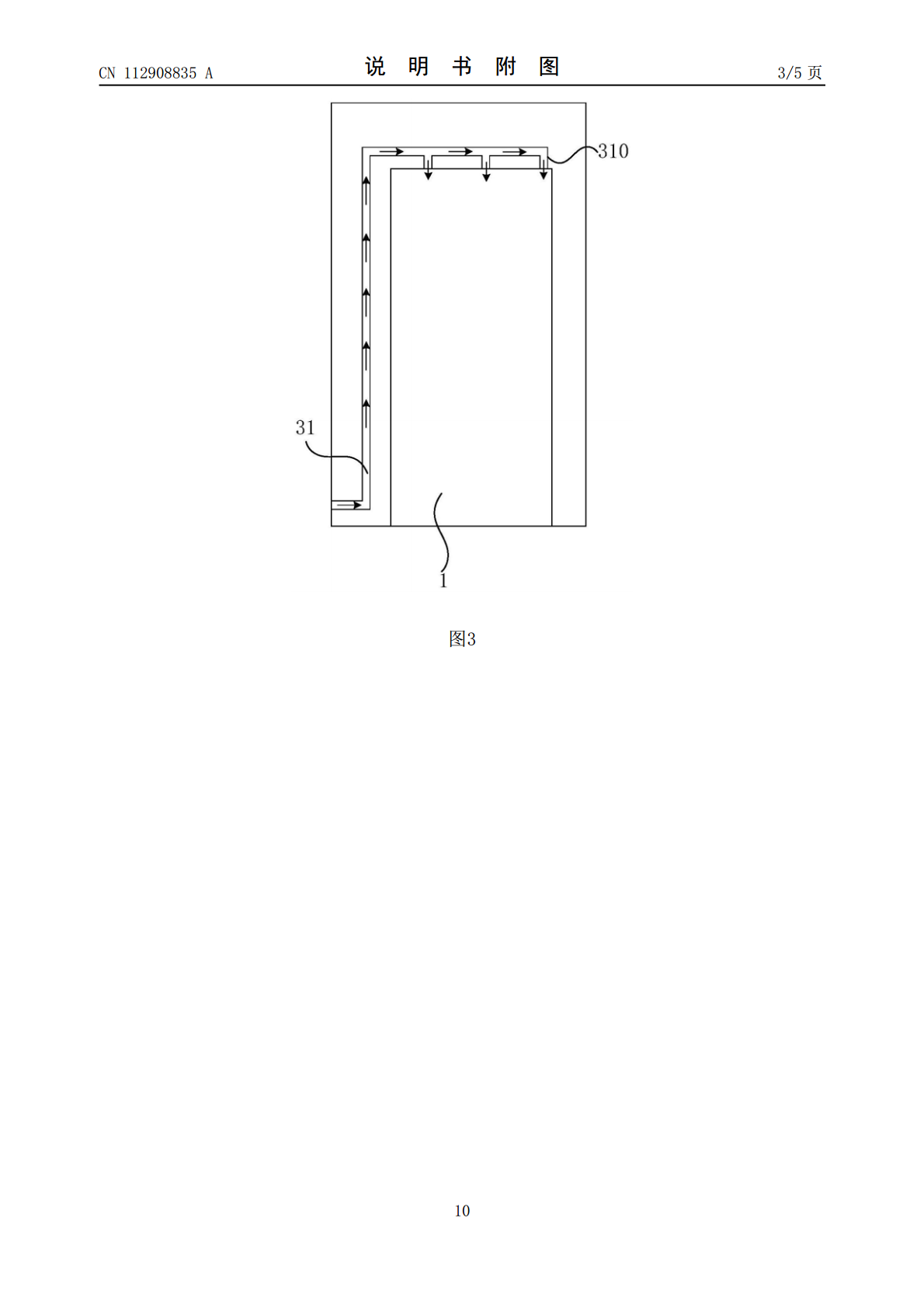

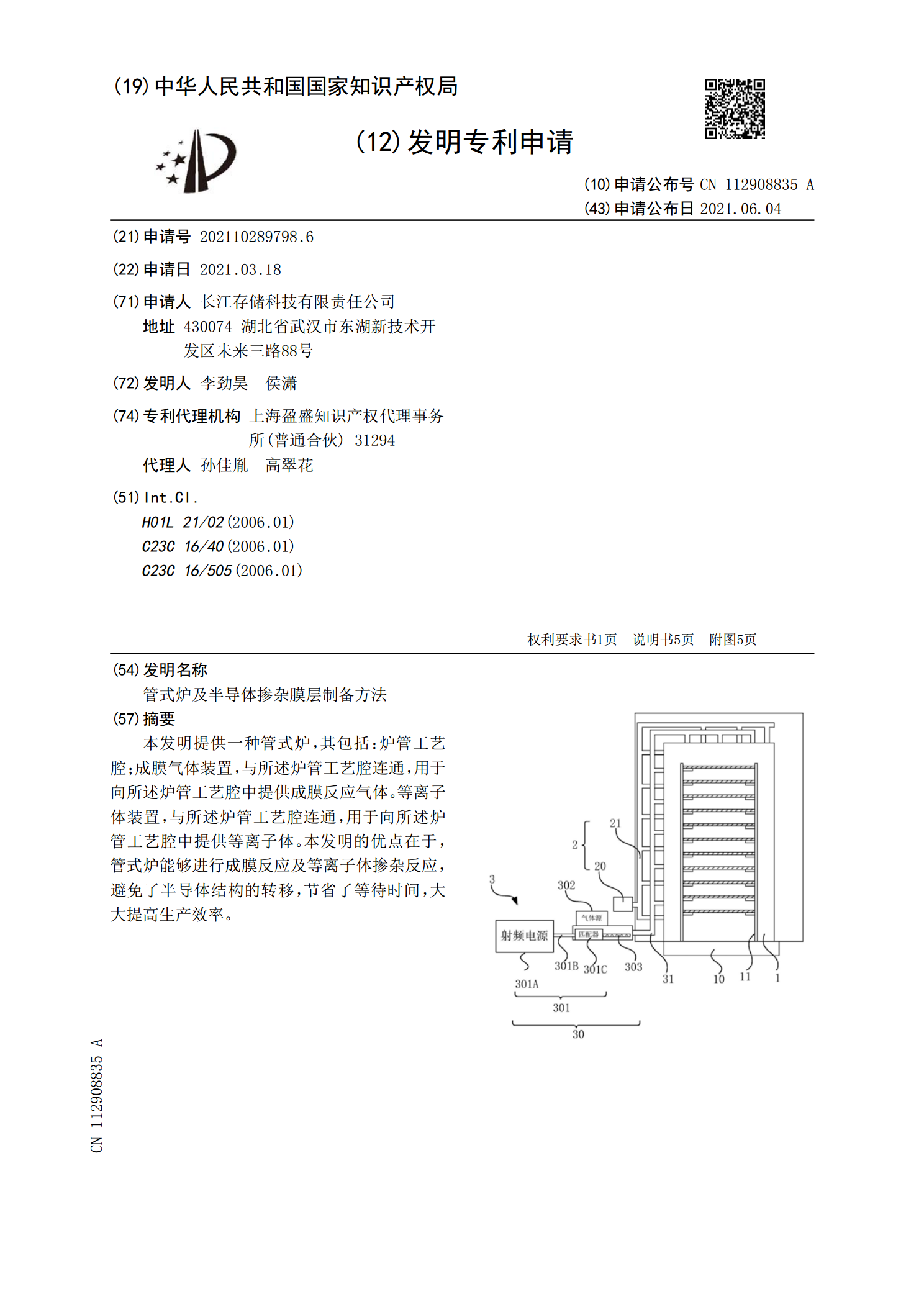

本发明提供一种管式炉,其包括:炉管工艺腔;成膜气体装置,与所述炉管工艺腔连通,用于向所述炉管工艺腔中提供成膜反应气体。等离子体装置,与所述炉管工艺腔连通,用于向所述炉管工艺腔中提供等离子体。本发明的优点在于,管式炉能够进行成膜反应及等离子体掺杂反应,避免了半导体结构的转移,节省了等待时间,大大提高生产效率。

同步外压管式膜制备方法.pdf

本发明属于分离膜制造领域,制得的外压管式膜可以用在环保、水处理和膜分离等领域。本发明同步外压管式膜制备方法将条状支撑网布以一定缠绕角连续缠绕到一根中心轴上,缠绕时条状支撑网布的两边互相重叠并将之这一重叠部分胶粘接或焊接,利用双向斜置的至少一个支撑管驱动轮,驱动支撑管平移并转动,同步在支撑管上涂敷铸膜液,经过凝胶或淬冷制成有支撑层和分离层的外压管式膜。本发明外压管式膜分离层与无纺布纤维的结合比与编织管纺织纤维的结合更牢固,因而不易脱落;外压管式膜机械强度比编织管加强膜更好,因此不易侧倒和互相缠绕;制膜效率高

内压管式膜的制备方法.pdf

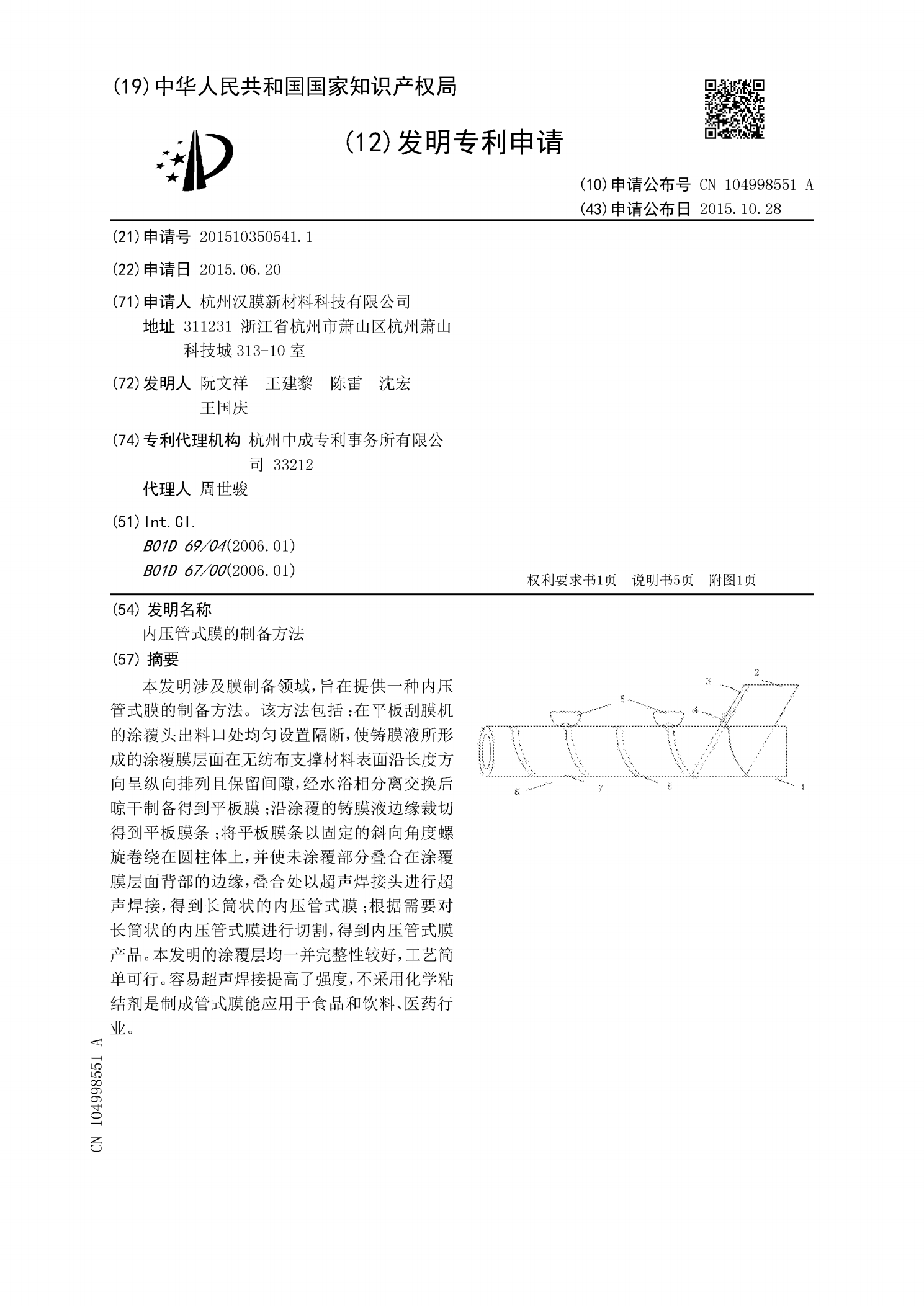

本发明涉及膜制备领域,旨在提供一种内压管式膜的制备方法。该方法包括:在平板刮膜机的涂覆头出料口处均匀设置隔断,使铸膜液所形成的涂覆膜层面在无纺布支撑材料表面沿长度方向呈纵向排列且保留间隙,经水浴相分离交换后晾干制备得到平板膜;沿涂覆的铸膜液边缘裁切得到平板膜条;将平板膜条以固定的斜向角度螺旋卷绕在圆柱体上,并使未涂覆部分叠合在涂覆膜层面背部的边缘,叠合处以超声焊接头进行超声焊接,得到长筒状的内压管式膜;根据需要对长筒状的内压管式膜进行切割,得到内压管式膜产品。本发明的涂覆层均一并完整性较好,工艺简单可行。

制备半导体层的方法.pdf

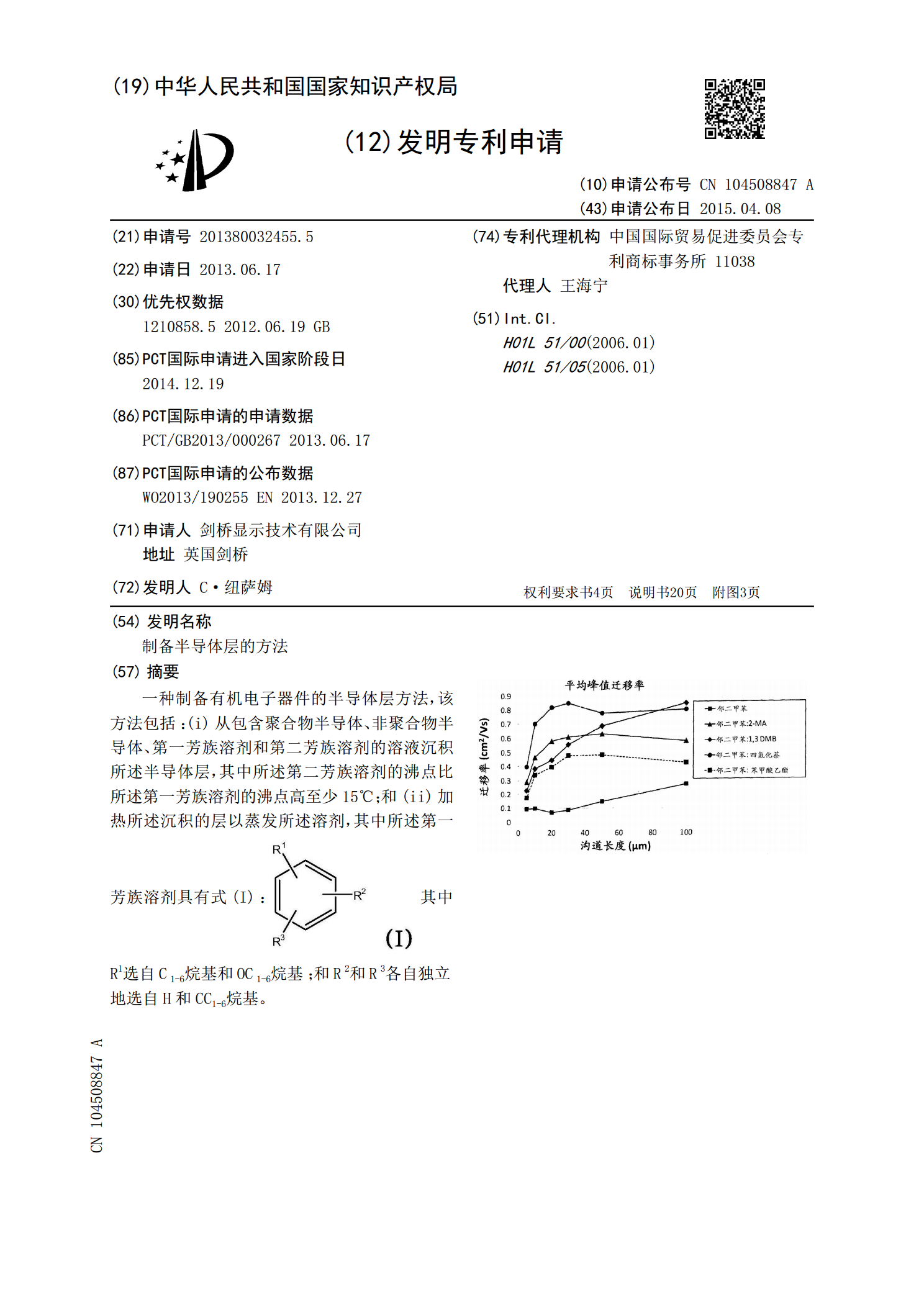

一种制备有机电子器件的半导体层方法,该方法包括:(i)从包含聚合物半导体、非聚合物半导体、第一芳族溶剂和第二芳族溶剂的溶液沉积所述半导体层,其中所述第二芳族溶剂的沸点比所述第一芳族溶剂的沸点高至少15℃;和(ii)加热所述沉积的层以蒸发所述溶剂,其中所述第一芳族溶剂具有式(I):

膜层的图形化方法及半导体器件的制备方法.pdf

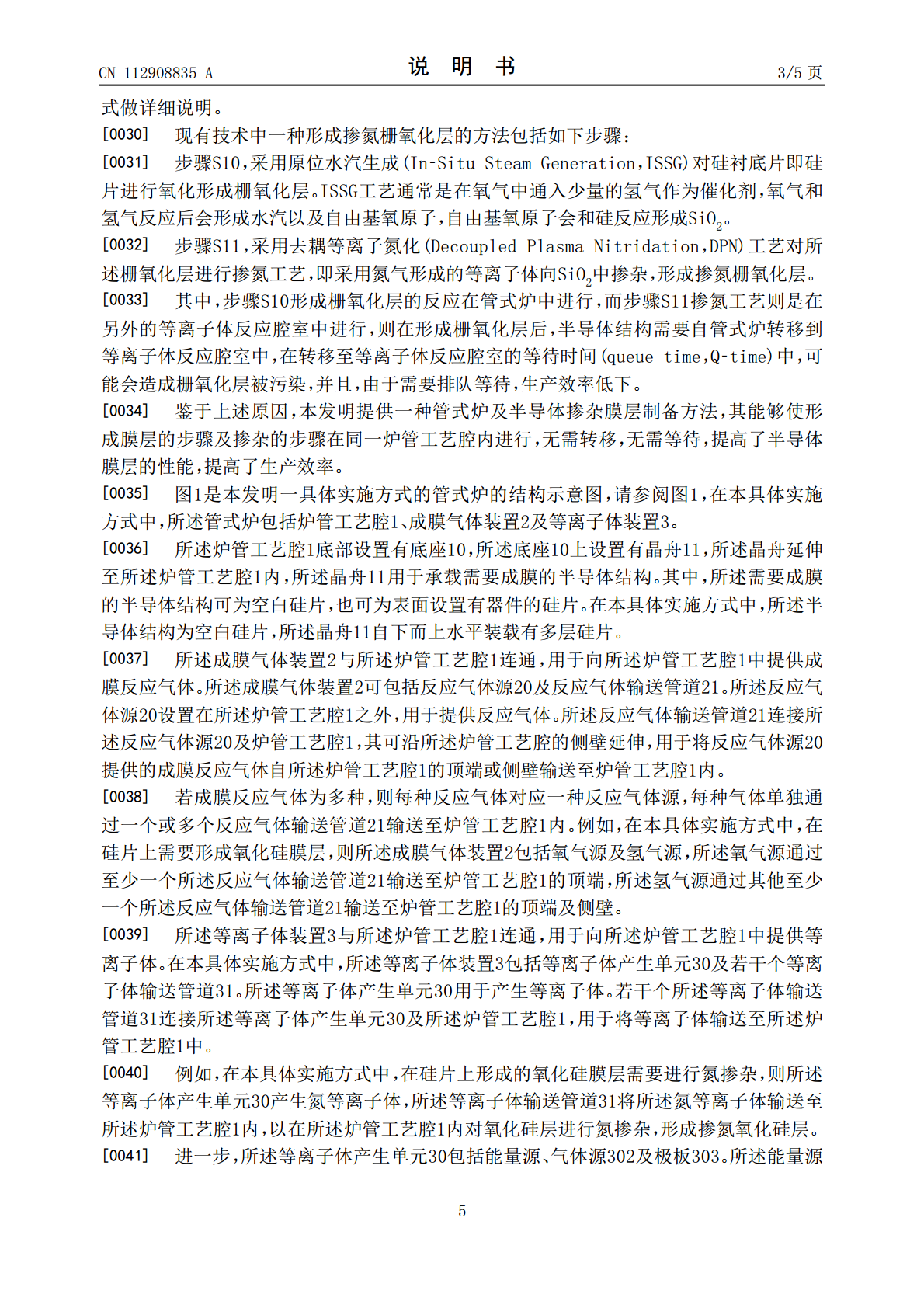

本发明提供了一种膜层的图形化方法及半导体器件的制备方法。在膜层的图形化方法中,通过光刻胶层的掩模对薄膜材料层中需要保留的部分进行等离子体表面处理,以使该部分的顶表面被钝化而形成钝化层,从而可利用形成的钝化层保护其下方的薄膜材料不会被去除,实现膜层的图形化效果。本发明提供的图形化方法,可有效改善光刻胶残留的问题,减少图形化工艺所带来的缺陷,并且工艺简单,实现了对图形化工艺的进一步优化。