一种铜合金键合丝及其制造方法.pdf

是你****盟主

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种铜合金键合丝及其制造方法.pdf

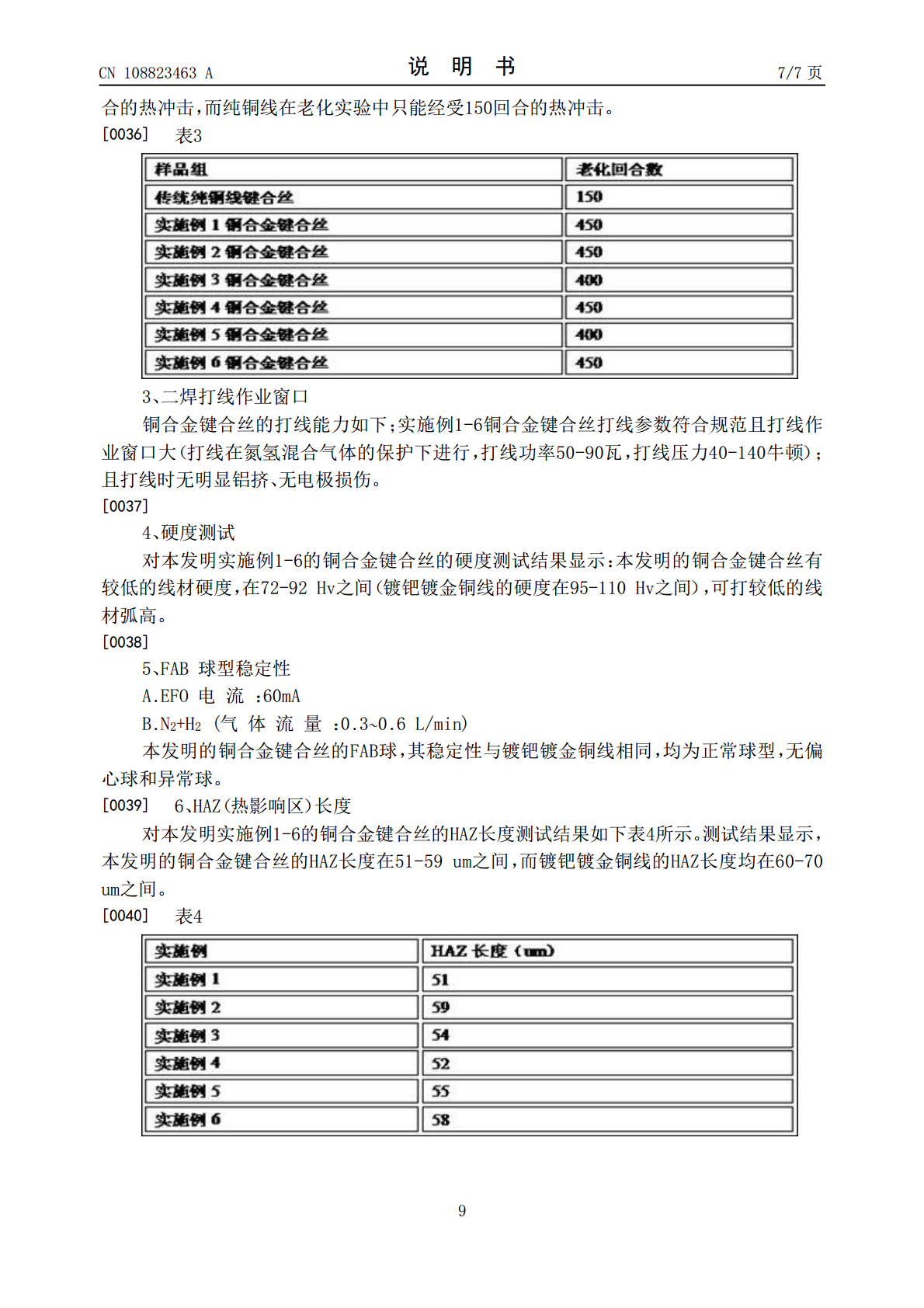

一种铜合金键合丝,其特征在于按重量计含有Ag0.3‑5%,微量添加元素1‑450ppm,余量为铜;所述微量添加元素是Ca、In、Be和Ge中的一种或其中两种以上的组合。本发明还提供上述铜合金键合丝的一种制造方法。本发明的铜合金键合丝具有以下有益效果:(1)具有优异的作业性和可靠性;(2)抗老化性能好;(3)有较适合的线材硬度,极大地降低了打线的弧高;(4)IC打线时,对一焊电极没有造成破裂和损伤;(5)能提供良好的接合性;(6)成本较低。

银合金键合丝及其制造方法.pdf

一种银合金键合丝,按重量计含有Au11‑30%,Pd0.1‑10%,微量添加元素2‑1000ppm,余量为Ag;所述微量添加元素是Ca、Cu、Be、In、Si、Pt和Ge中的一种或其中两种以上的组合。本发明还提供上述银合金键合丝的一种制造方法。本发明的银合金键合丝具有以下有益效果:(1)抗硫化性能优异;(2)抗老化性能优异,改善封装产品在热冲击试验中的可靠性,在同等老化条件下(‑40℃~100℃),本发明的银合金键合丝能够经受250‑300回合的热冲击;(3)打线作业窗口大具有良好的作业性;(4)F

一种金银合金键合丝及其制造方法.pdf

一种金银合金键合丝,按重量计含有Au38.5‑41.5%,Pd1‑3.5%,Pt0.5‑1%,微量添加元素30‑100ppm,余量为银;所述微量添加元素是In、Co、Ga、Mg、Ca、Ce和Ni中的一种或其中两种以上的组合。本发明还提供上述金银合金键合丝的一种制造方法。本发明的金银合金键合丝具有优异的高可靠性能,抗拉强度高,焊点接合性好,且能降低成本(本发明的金银合金键合丝与含金量60%左右的金合金键合丝相比,原材料成本降低了30%左右,而产品综合性能却相当)。

一种金合金键合丝及其制造方法.pdf

本发明提供一种金合金键合丝,其特征在于按重量计含有Pd0.5‑2%,Ag15‑30%,Cu0.5‑3%,Pt0.1‑2%,微量添加元素2‑200ppm,余量为金;所述微量添加元素是Ca、In、Co、Be、Ga、Mg、Ce和Ni中的一种或其中两种以上的组合。本发明提供还上述金合金键合丝的一种制造方法。本发明的金合金键合丝具有优异的高可靠性能和抗硫化性能,抗拉强度高,焊点接合性好,且能降低成本。

一种金合金键合丝及其制造方法.pdf

一种金合金键合丝,其特征在于按重量计含有:钯1-1.5%,银20-24%,钙、铍和铈中的一种和其中多种的组合2-200ppm,余量为金。本发明还提供上述金合金键合丝的一种制造方法。本发明的金合金键合丝可用于IC、LED封装中,综合打线性能优异,具体体现在:热影响区长度小(可达到53-60um),极大地降低了打线的弧高;烧球性能好,在FAB烧球后得到数目适中的对称柱状晶,变形球真圆度高;封装后产品热冲击性能好,可靠性高。