漏电补偿电路、芯片及电子设备.pdf

雨星****萌娃

亲,该文档总共16页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

漏电补偿电路、芯片及电子设备.pdf

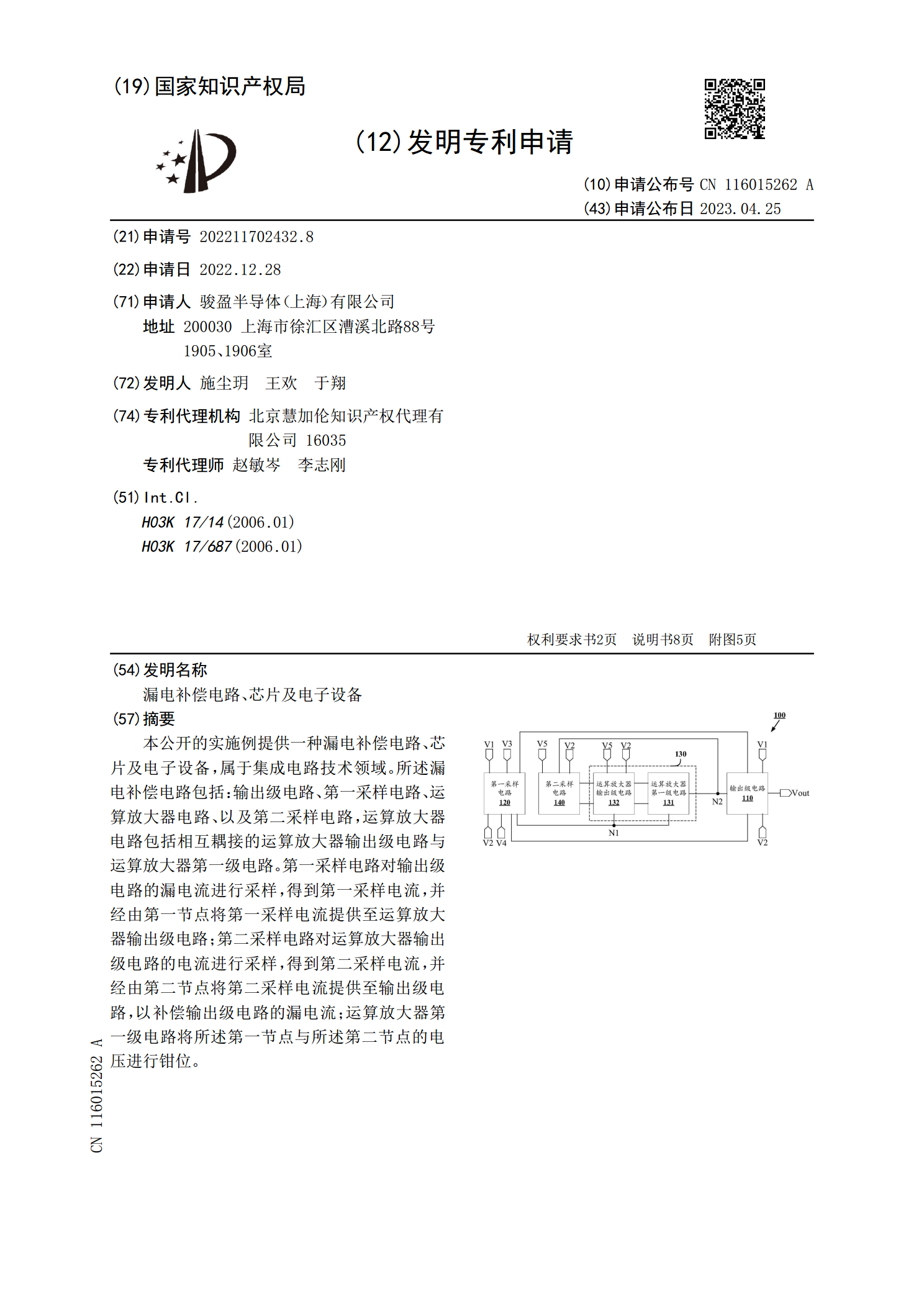

本公开的实施例提供一种漏电补偿电路、芯片及电子设备,属于集成电路技术领域。所述漏电补偿电路包括:输出级电路、第一采样电路、运算放大器电路、以及第二采样电路,运算放大器电路包括相互耦接的运算放大器输出级电路与运算放大器第一级电路。第一采样电路对输出级电路的漏电流进行采样,得到第一采样电流,并经由第一节点将第一采样电流提供至运算放大器输出级电路;第二采样电路对运算放大器输出级电路的电流进行采样,得到第二采样电流,并经由第二节点将第二采样电流提供至输出级电路,以补偿输出级电路的漏电流;运算放大器第一级电路将所述

一种通用输入输出接口防漏电电路、芯片和电子设备.pdf

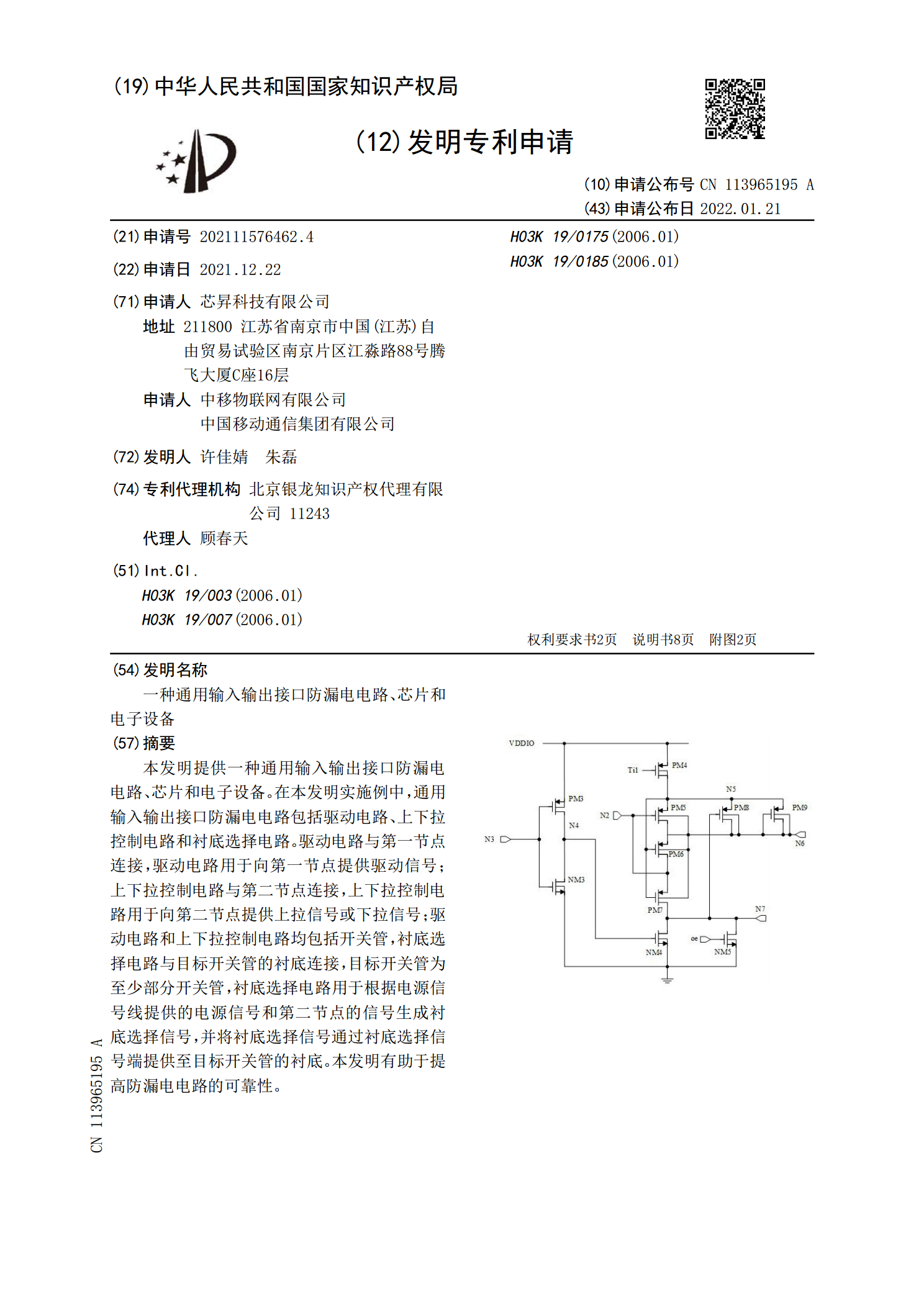

本发明提供一种通用输入输出接口防漏电电路、芯片和电子设备。在本发明实施例中,通用输入输出接口防漏电电路包括驱动电路、上下拉控制电路和衬底选择电路。驱动电路与第一节点连接,驱动电路用于向第一节点提供驱动信号;上下拉控制电路与第二节点连接,上下拉控制电路用于向第二节点提供上拉信号或下拉信号;驱动电路和上下拉控制电路均包括开关管,衬底选择电路与目标开关管的衬底连接,目标开关管为至少部分开关管,衬底选择电路用于根据电源信号线提供的电源信号和第二节点的信号生成衬底选择信号,并将衬底选择信号通过衬底选择信号端提供至目

一种芯片之间通信的防漏电电路.pdf

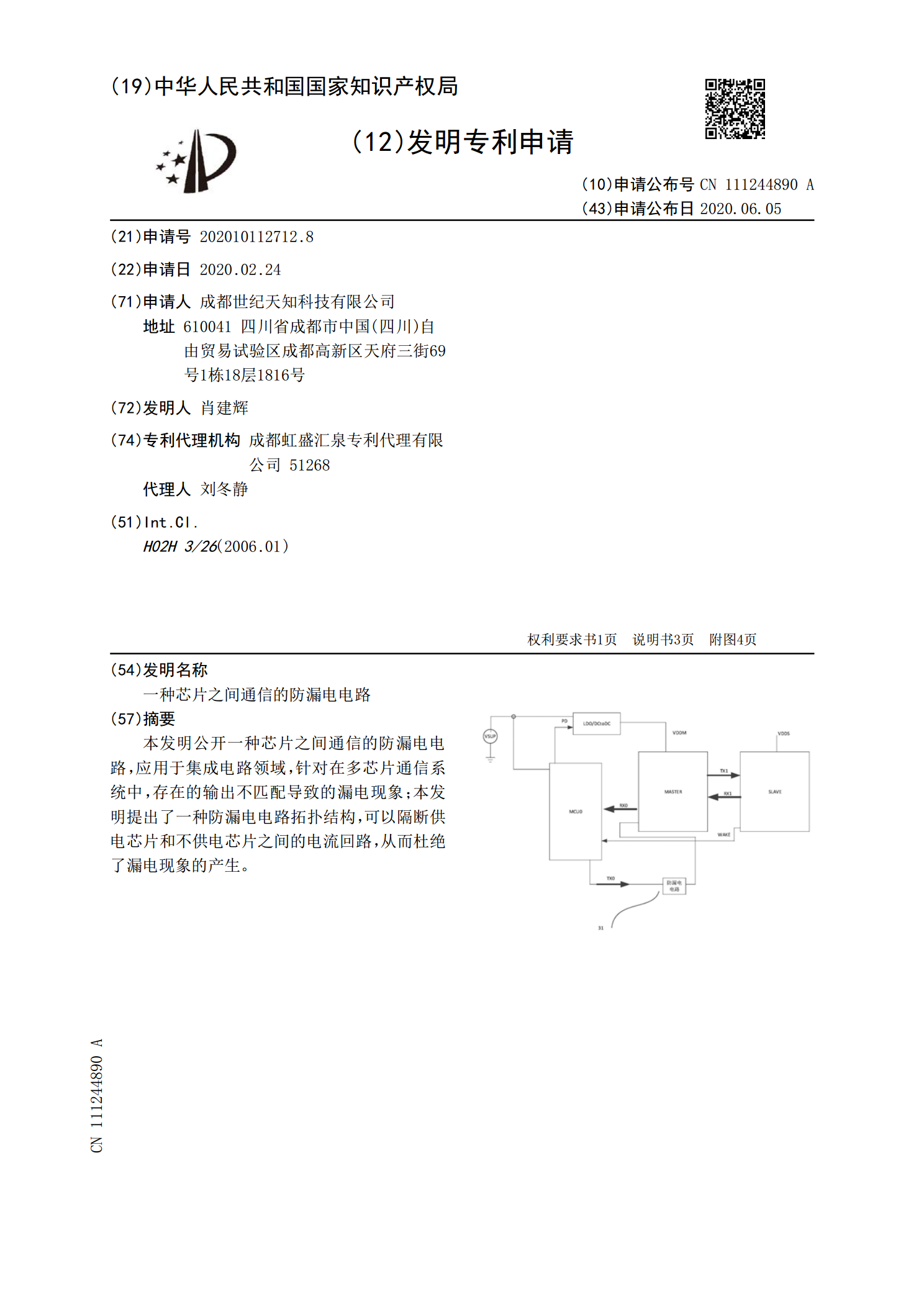

本发明公开一种芯片之间通信的防漏电电路,应用于集成电路领域,针对在多芯片通信系统中,存在的输出不匹配导致的漏电现象;本发明提出了一种防漏电电路拓扑结构,可以隔断供电芯片和不供电芯片之间的电流回路,从而杜绝了漏电现象的产生。

故障检测电路、芯片及电子设备.pdf

本申请实施例涉及通信技术领域,公开了一种故障检测电路、芯片及电子设备。电路包括:电源芯片、检测单元、电平输出单元和微控制单元;电源芯片用于作为输出目标电压的电源并为检测单元提供输入输出的压差;检测单元用于在电源芯片输入端和输出端存在的电压差的情况下,将电平输出单元的输出端接地;电平输出单元用于在输出端接地的情况下为微控制单元提供第一电平信号,在输出端未接地的情况下为微控制单元提供第二电平信号;微控制单元,用于在获取到第一电平信号的情况下,判定电源芯片正常,在获取到第二电平信号的情况下,判定电源芯片输入输出

信号输入电路、电子芯片及电子设备.pdf

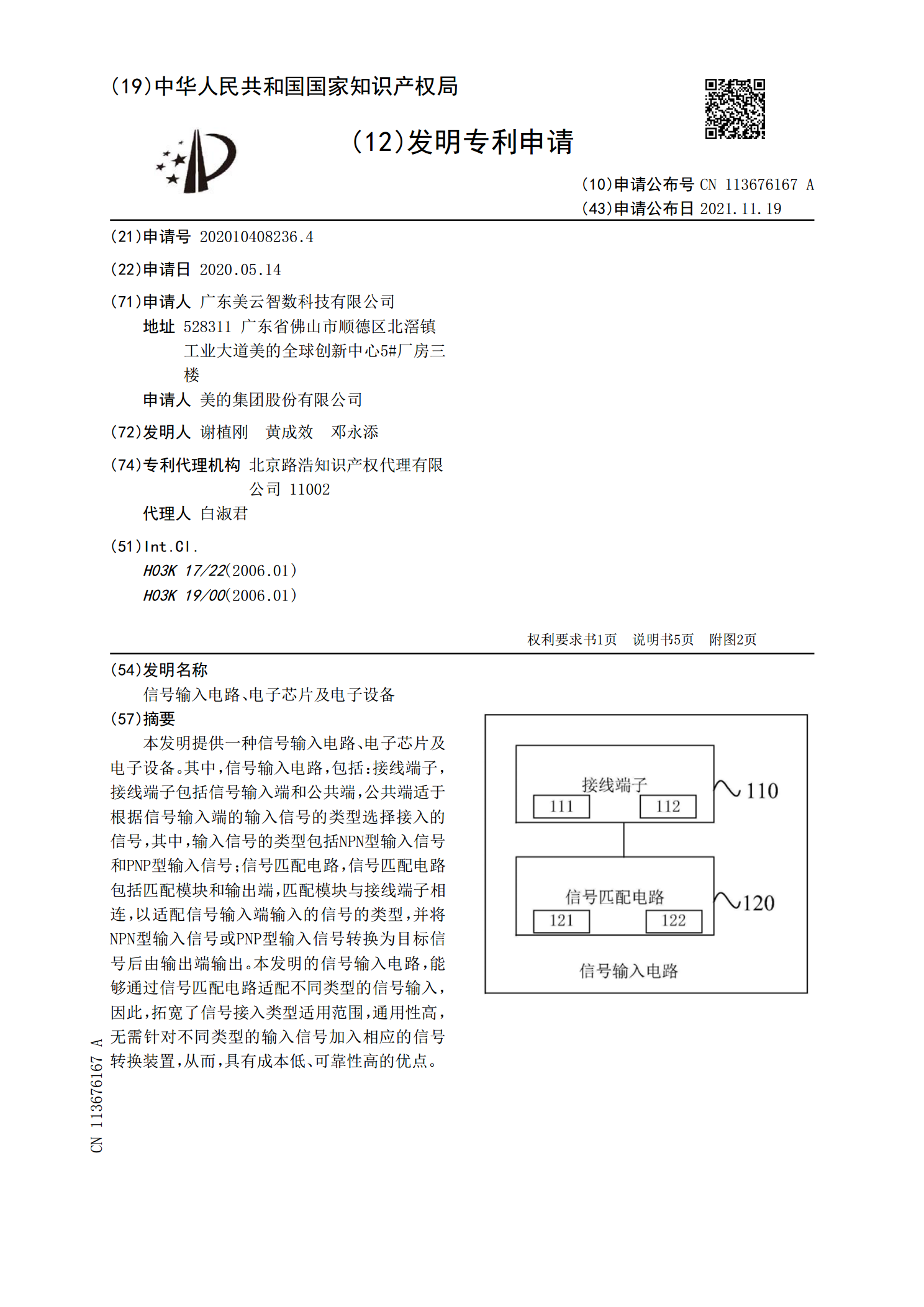

本发明提供一种信号输入电路、电子芯片及电子设备。其中,信号输入电路,包括:接线端子,接线端子包括信号输入端和公共端,公共端适于根据信号输入端的输入信号的类型选择接入的信号,其中,输入信号的类型包括NPN型输入信号和PNP型输入信号;信号匹配电路,信号匹配电路包括匹配模块和输出端,匹配模块与接线端子相连,以适配信号输入端输入的信号的类型,并将NPN型输入信号或PNP型输入信号转换为目标信号后由输出端输出。本发明的信号输入电路,能够通过信号匹配电路适配不同类型的信号输入,因此,拓宽了信号接入类型适用范围,通用