将相变存储器并入CMOS工艺的非易失性SRAM单元.pdf

一只****懿呀

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

将相变存储器并入CMOS工艺的非易失性SRAM单元.pdf

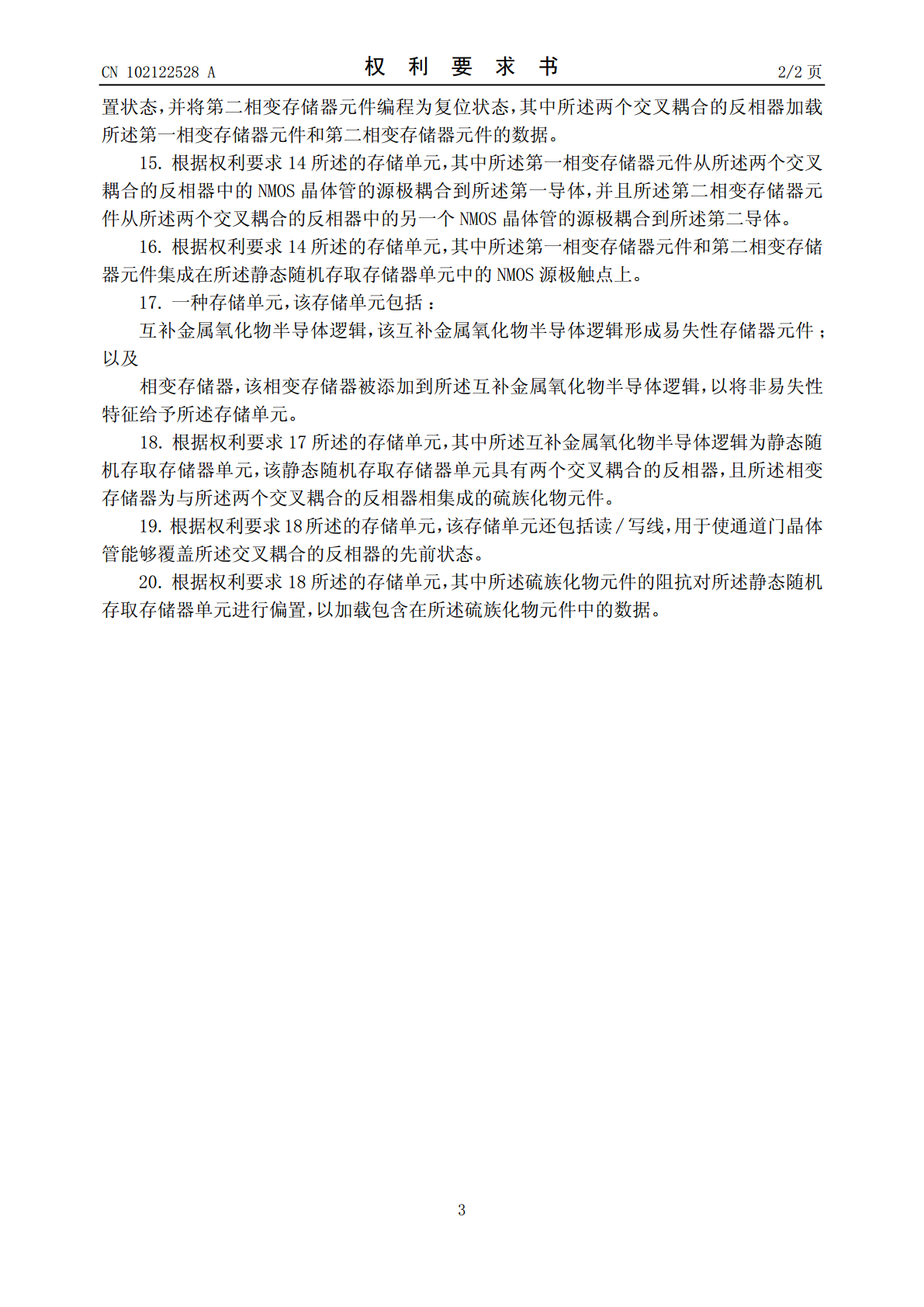

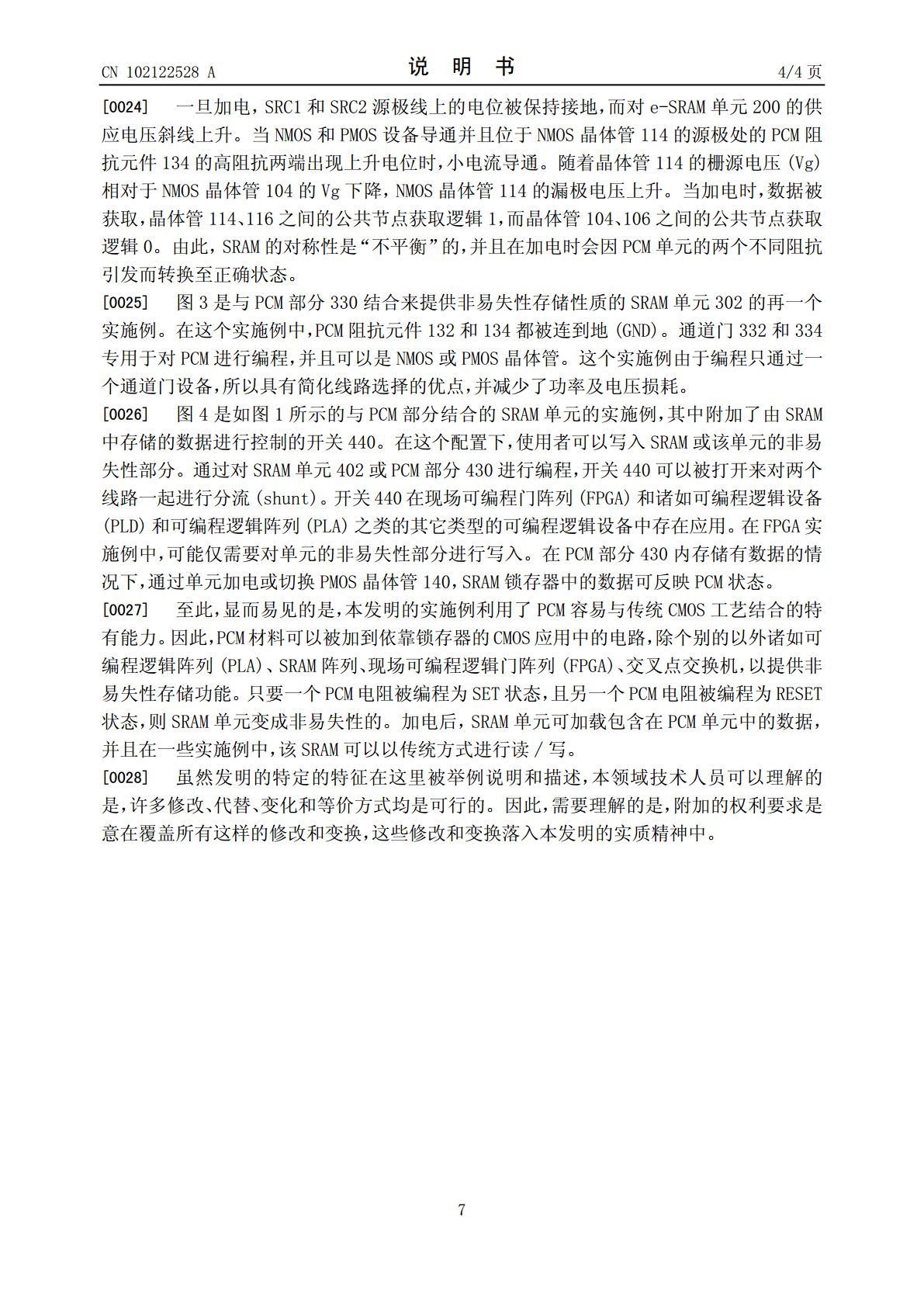

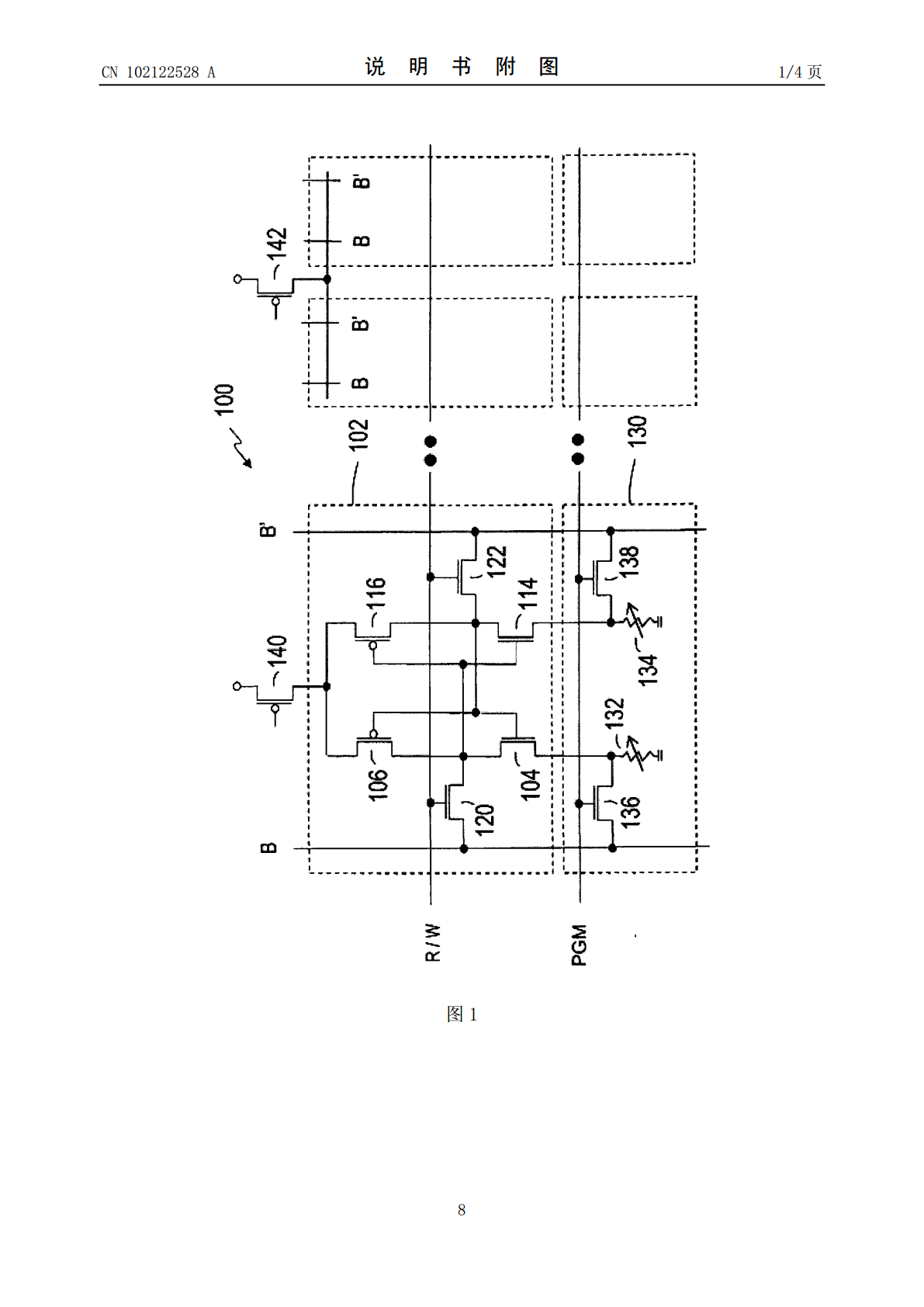

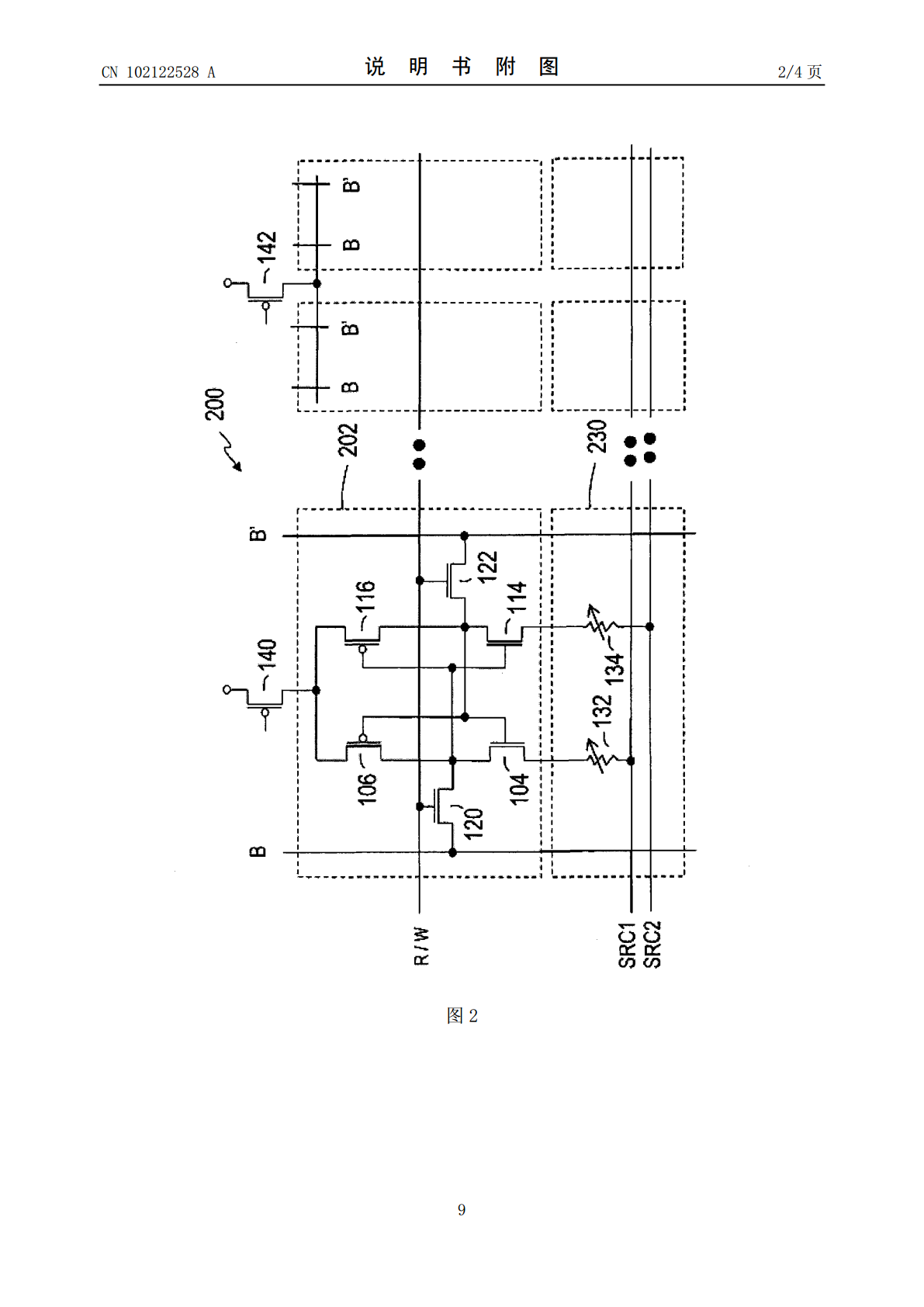

一种SRAM单元,该SRAM单元具有由CMOS技术形成的两个交叉耦合反相器以及第一和第二硫族化物元件,该第一和第二硫族化物元件与SRAM单元相集成,以将非易失性性质添加到存储单元。PCM阻抗被编程为SET状态和RESET状态,并且当加电时,SRAM单元加载包含在PCM单元中的数据。

65nm工艺下基于RRAM的非易失性SRAM单元设计.docx

65nm工艺下基于RRAM的非易失性SRAM单元设计标题:基于RRAM的非易失性SRAM单元设计研究摘要:随着集成电路制造工艺的不断发展,对于存储器单元的需求也越来越高。传统的SRAM存储器单元由于其易失性的特点,需要不断地刷新来保持数据的稳定。而基于RRAM(ResistiveRandom-AccessMemory)的非易失性SRAM单元设计可以有效地解决这个问题。本文以65纳米工艺为基础,研究基于RRAM的非易失性SRAM单元的设计问题。关键词:RRAM、非易失性、SRAM、65纳米工艺一、引言随着移

65nm工艺下基于RRAM的非易失性SRAM单元设计的开题报告.docx

65nm工艺下基于RRAM的非易失性SRAM单元设计的开题报告一、选题背景及意义随着集成电路制造技术的不断发展,芯片上存储器的集成度越来越高,非易失性存储器逐渐成为集成电路中重要的组成部分。目前主流的非易失性存储器有闪存和EEPROM等,但这些存储器的密度和速度较低,而且易受到擦写次数限制,因此对于一些更高密度、更快速的应用而言并不够理想。相较之下,基于阻变存储器的非易失性随机存储器(RRAM-NVSRAM)在密度、速度和可靠性等方面具有潜力。本文选题旨在研究基于65nm工艺下的RRAM-NVSRAM单元

基于多值RRAM的高能效非易失性SRAM设计.docx

基于多值RRAM的高能效非易失性SRAM设计标题:基于多值RRAM的高能效非易失性SRAM设计摘要:随着集成电路技术的不断发展,存储器在计算机系统中的重要性不断增加。传统的静态随机存取存储器(SRAM)是一种高速、易失性存储器。然而,SRAM需要连续的电源供应,并且功耗较高。为了解决这个问题,非易失性SRAM逐渐成为研究的热点。本文提出了一种基于多值RRAM的高能效非易失性SRAM设计方案。通过利用多值RRAM的多个阈值电压水平,我们实现了较低的功耗和更高的能效。关键词:多值RRAM,非易失性SRAM,高

非易失性静态随机访问存储器.pdf

本发明涉及非易失性静态随机访问存储器,揭示一种非易失性静态随机访问存储器(NV‑SRAM)单元的实施例。该NV‑SRAM单元包括静态随机访问存储器(SRAM)电路(例如,传统的高性能、高可靠性SRAM电路)。然而,为了在仍保留与SRAM电路操作相关联的优点的同时避免易失性,该NV‑SRAM单元还包括一对NVM电路。这些NVM电路在断电之前撷取储存于该SRAM电路的数据节点上的数据值,并在通电时将这些数据值重写回该SRAM电路的数据节点上。本发明还揭示一种操作存储器阵列中的选定NV‑SRAM单元的方法的实施