一种硅基砷化镓复合衬底的制备方法.pdf

醉香****mm

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种硅基砷化镓复合衬底的制备方法.pdf

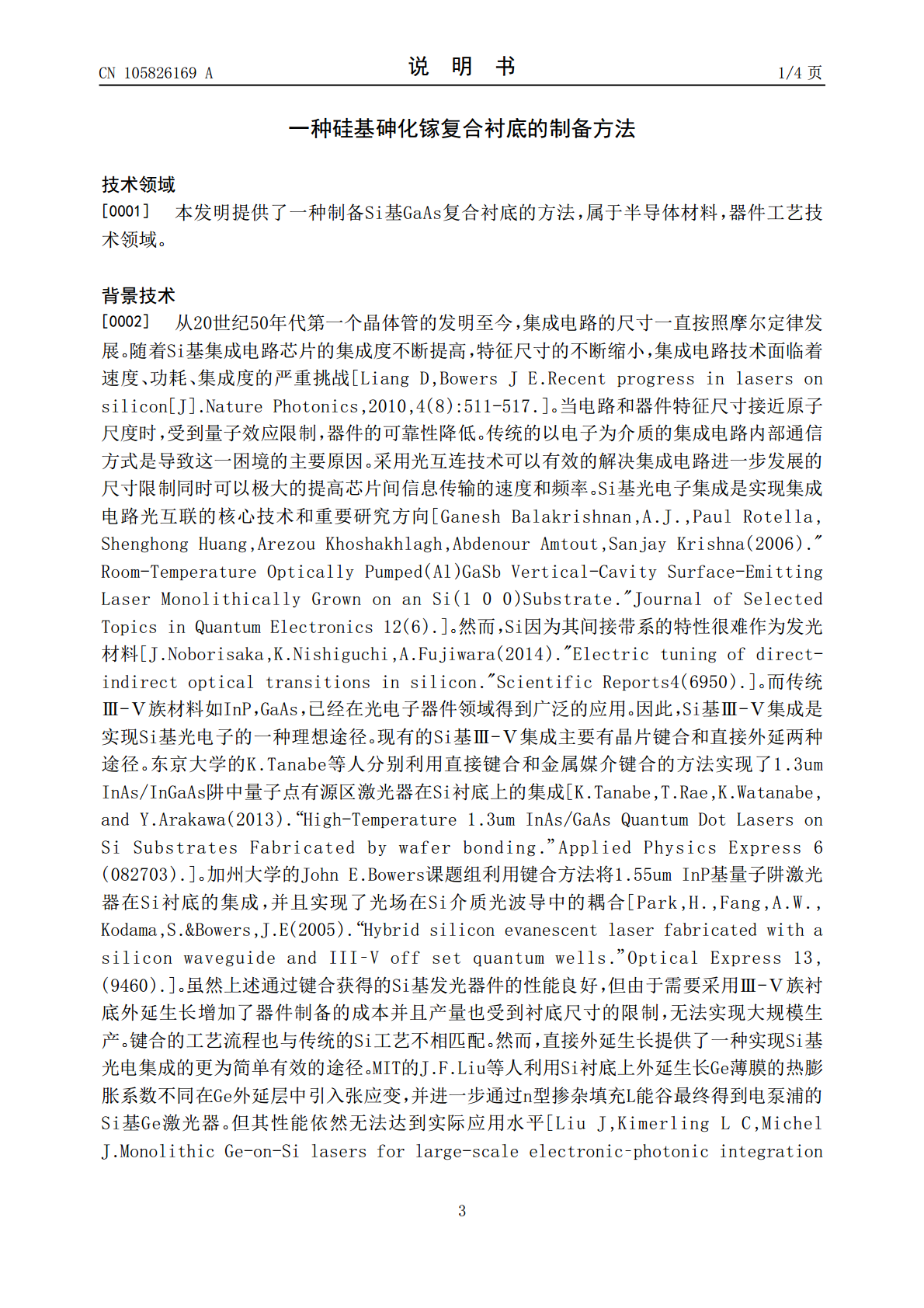

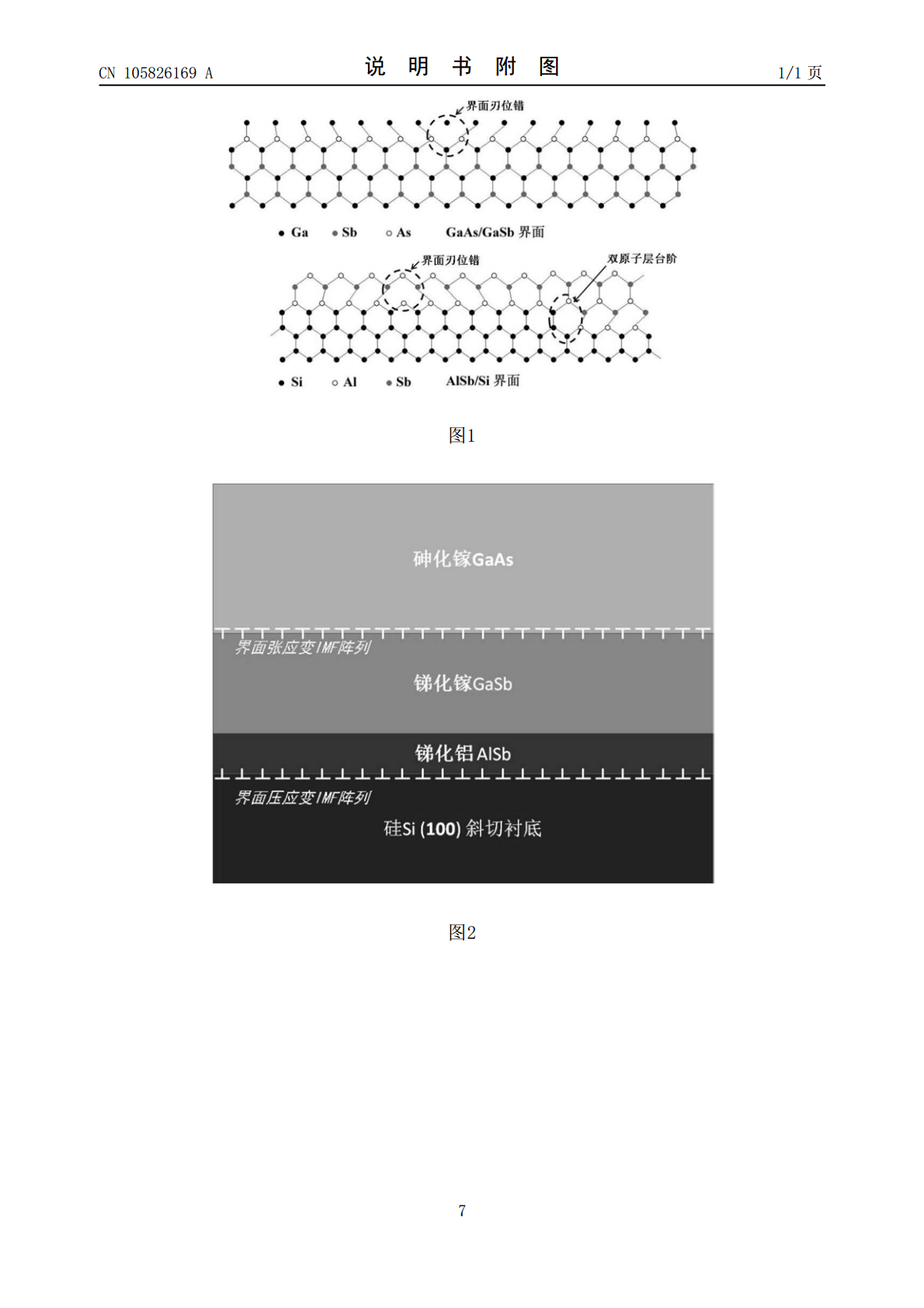

本发明涉及一种硅基砷化镓复合衬底的制备方法,其特征在于所述的复合衬底以锑化物为中间层、上、下表面分别形成压应变AlSb/Si和张应变GaAs/GaSb的界面失配位错阵列IMF,使应变在两个界面处得到释放,解决了GaAs与Si之间晶格失配。所述Si衬底为向[110]晶向斜切5°。制备方法特征在于首先在Si衬底上生长AlSb/SiIMF阵列,然后生长GaSb缓冲层,然后在GaSb缓冲层上生长GaAs/GaSbIFM阵列,从而完成从Si衬底向GaAs材料层的过渡,获得Si基GaAs复合衬底。本发明解决了Si

硅基砷化镓外延结构、激光器及制备方法.pdf

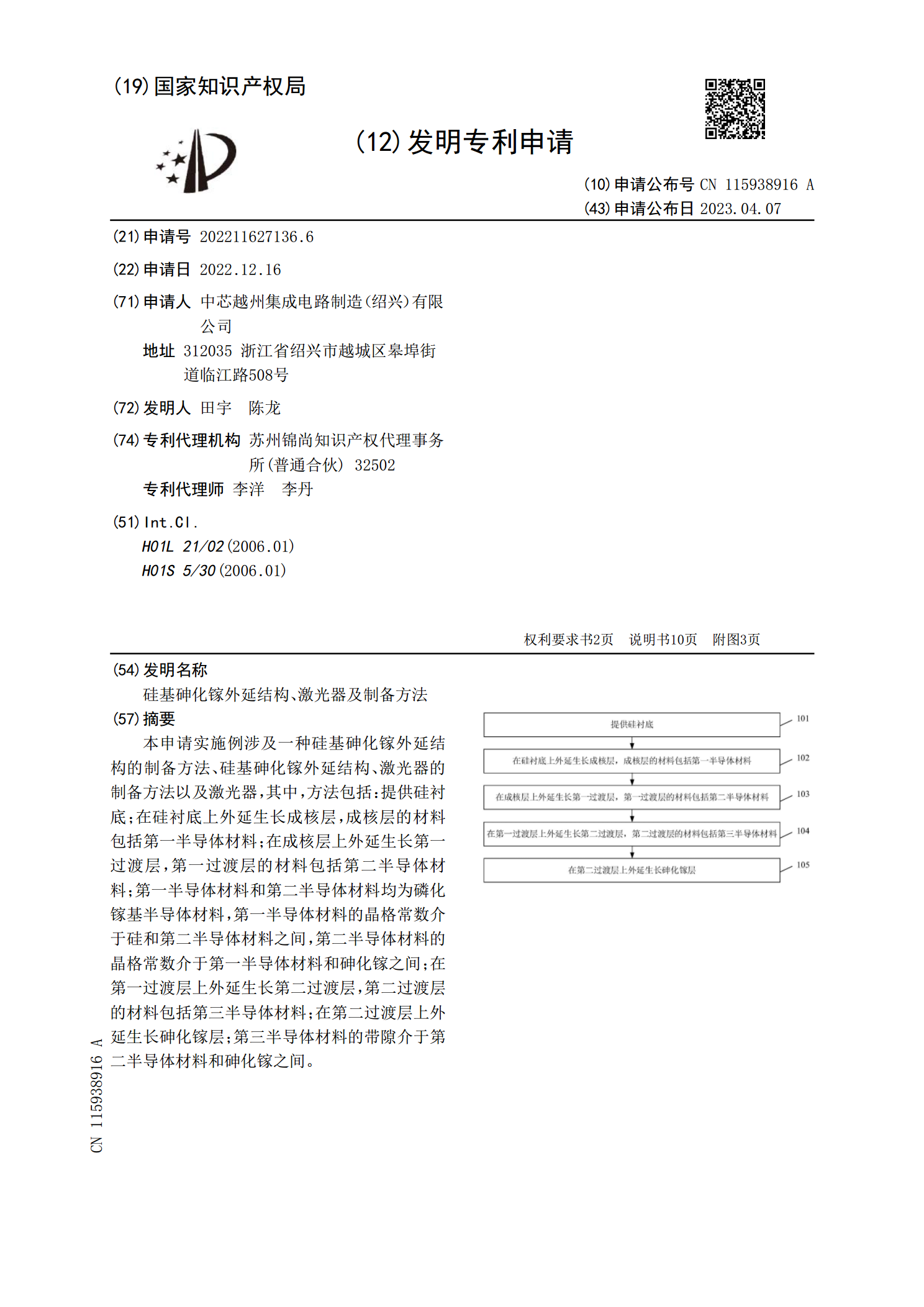

本申请实施例涉及一种硅基砷化镓外延结构的制备方法、硅基砷化镓外延结构、激光器的制备方法以及激光器,其中,方法包括:提供硅衬底;在硅衬底上外延生长成核层,成核层的材料包括第一半导体材料;在成核层上外延生长第一过渡层,第一过渡层的材料包括第二半导体材料;第一半导体材料和第二半导体材料均为磷化镓基半导体材料,第一半导体材料的晶格常数介于硅和第二半导体材料之间,第二半导体材料的晶格常数介于第一半导体材料和砷化镓之间;在第一过渡层上外延生长第二过渡层,第二过渡层的材料包括第三半导体材料;在第二过渡层上外延生长砷化镓

一种硅基Ⅲ-V族砷化镓半导体材料制备方法和系统.pdf

本发明提供一种硅基III-V族砷化镓半导体材料制备方法和系统,包括:在清洁的单晶硅衬底表面制备二氧化硅膜;在所述二氧化硅膜上,采用纳米压印技术得到二氧化硅纳米图形层,所述二氧化硅纳米图形层包括裸露单晶硅衬底表面的生长窗口区,以及二氧化硅图形区,生长窗口区和二氧化硅图形区交错分布;在所述生长窗口区上,沉积接近或等于所述二氧化硅图形区的台面高度的砷化镓缓冲层;在所述砷化镓缓冲层和所述二氧化硅图形区上外延生长III-V族半导体材料。本发明采用纳米压印的技术制作二氧化硅纳米图形层,作为半导体材料生长的图形衬底,打

一种砷化镓废料回收制备砷化镓多晶的方法.pdf

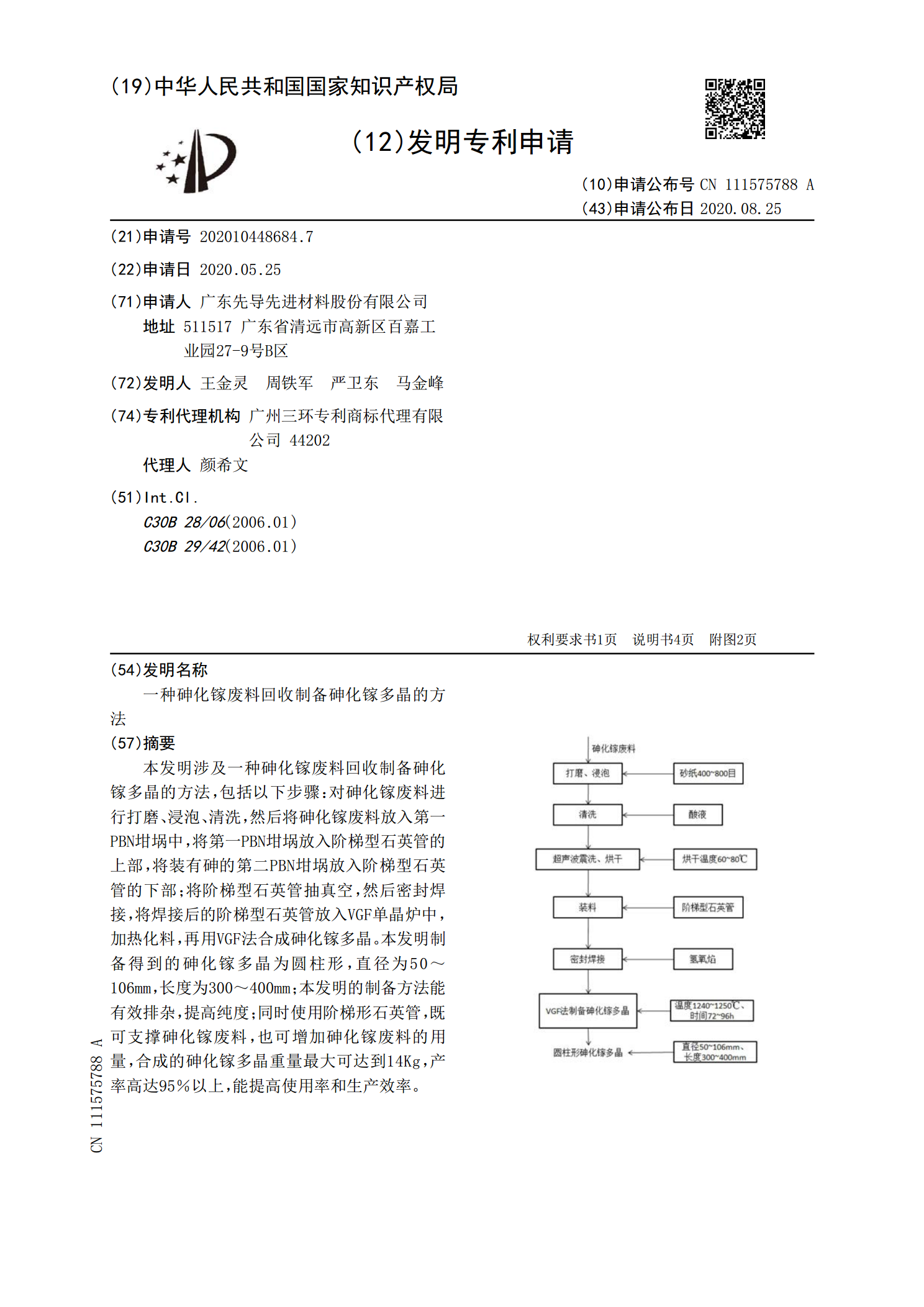

本发明涉及一种砷化镓废料回收制备砷化镓多晶的方法,包括以下步骤:对砷化镓废料进行打磨、浸泡、清洗,然后将砷化镓废料放入第一PBN坩埚中,将第一PBN坩埚放入阶梯型石英管的上部,将装有砷的第二PBN坩埚放入阶梯型石英管的下部;将阶梯型石英管抽真空,然后密封焊接,将焊接后的阶梯型石英管放入VGF单晶炉中,加热化料,再用VGF法合成砷化镓多晶。本发明制备得到的砷化镓多晶为圆柱形,直径为50~106mm,长度为300~400mm;本发明的制备方法能有效排杂,提高纯度;同时使用阶梯形石英管,既可支撑砷化镓废料,也可

一种砷化镓超薄衬底及应用.pdf

本发明公开了一种砷化镓超薄衬底及应用,所述砷化镓超薄衬底的形状为正六边形,所述砷化镓超薄衬底的内部包括至少两个边长依次减小的多孔正六边形,呈窝蜂状。其加工方法为材料提纯、多晶料制备、晶体生长、切片、磨边、研磨、腐蚀、粗抛和精抛、清洗、光刻腐蚀,该超薄砷化镓衬底应用于热核电池,可有效增强热核电池对放射源辐射能量的吸收效果,提高转换效率,电池输出的电压和电流可达到0‑4V、0.8‑2A。