一种叠层电路结构及其制备方法.pdf

Ja****20

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种叠层电路结构及其制备方法.pdf

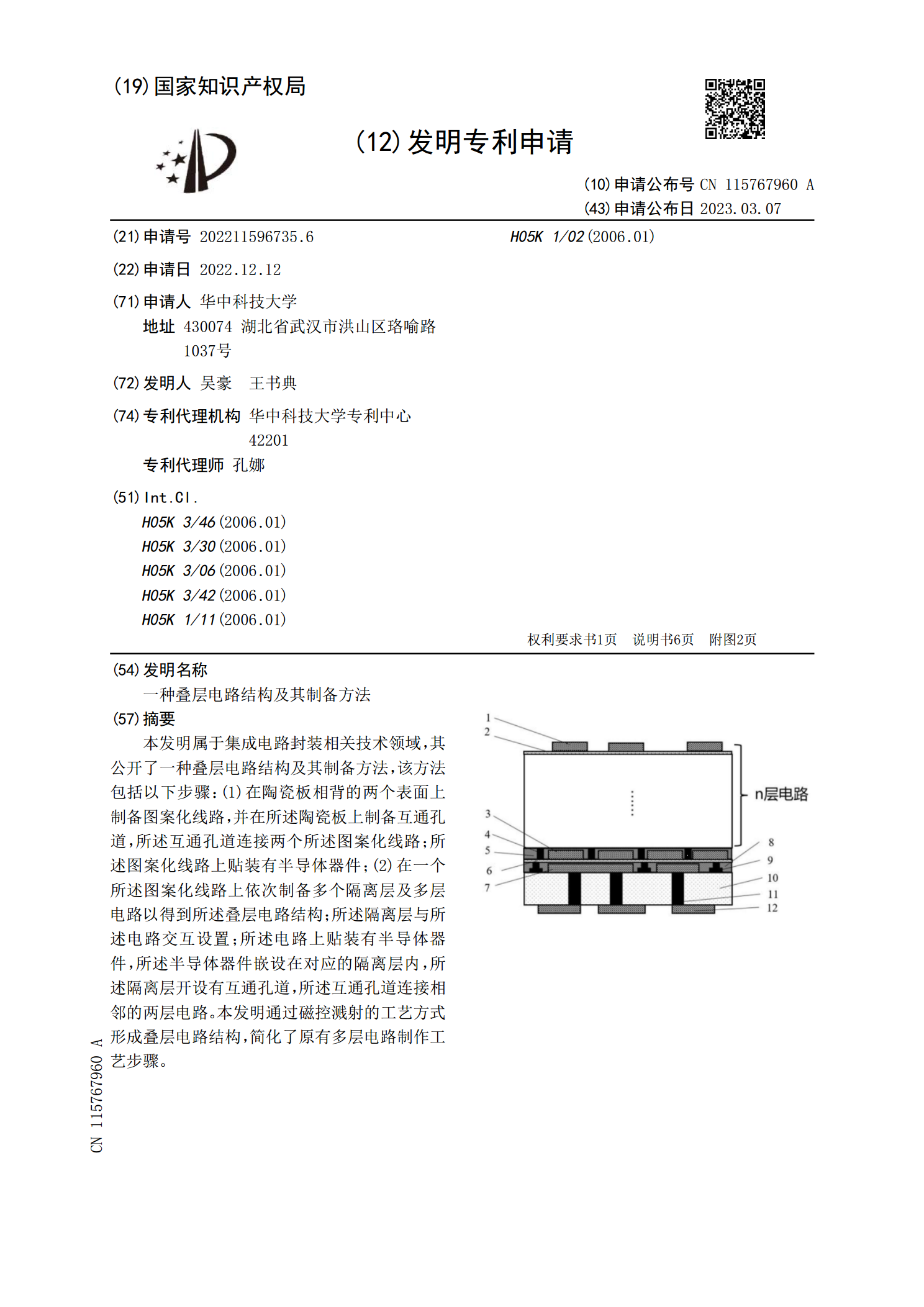

本发明属于集成电路封装相关技术领域,其公开了一种叠层电路结构及其制备方法,该方法包括以下步骤:(1)在陶瓷板相背的两个表面上制备图案化线路,并在所述陶瓷板上制备互通孔道,所述互通孔道连接两个所述图案化线路;所述图案化线路上贴装有半导体器件;(2)在一个所述图案化线路上依次制备多个隔离层及多层电路以得到所述叠层电路结构;所述隔离层与所述电路交互设置;所述电路上贴装有半导体器件,所述半导体器件嵌设在对应的隔离层内,所述隔离层开设有互通孔道,所述互通孔道连接相邻的两层电路。本发明通过磁控溅射的工艺方式形成叠层电

多元叠层结构硬质涂层及其制备方法.pdf

本发明公开了一种多元叠层结构硬质涂层及利用反应磁控多弧线圈真空镀膜设备制备多元叠层结构硬质涂层的方法,包括以下步骤:a)对基片净化和超声清洗;b)对基片表面进行气体放电轰击,以去除基片表面的杂质和油污,活化表面;c)在一定气压条件下,采用反应磁控多弧线圈真空镀膜设备在基片表面形成多元叠层结构硬质涂层;多元叠层结构硬质涂层为CrAlSiN、TiAlN、CrAlN、Cr中的两种或者多种膜层。本发明的整个制备工艺过程简单,可操作性强,镀膜工艺在真空室内完成,工艺节能绿色环保,更主要的是制备工艺沉积速率快,镀膜效

一种具有叠层复合结构材料的制备方法.pdf

一种具有叠层复合结构过滤材料的制备方法,其特征在于,采用化学气相渗透法结合高温氧化处理制备具有中空骨架的碳化硅泡沫支撑体,将碳化硅纤维预先编织成平纹和斜纹二维布,叠层铺放至碳化硅泡沫支撑体一侧表面,通过纤维缝合方式将碳化硅纤维二维布与碳化硅泡沫缝合固定,配制硝酸镍溶液,将缝合固定的材料浸渍硝酸镍溶液,烘干后放入气相沉积炉中,化学气相沉积碳化硅纳米线后即可得到一种具有叠层复合结构过滤材料。本发明具有的优点:1、叠层结构具有梯度孔隙,利于过滤清灰;2、多孔网状碳化硅晶须降低过滤阻力,提高过滤效率;3、采用整体

多结叠层电池及其制备方法.pdf

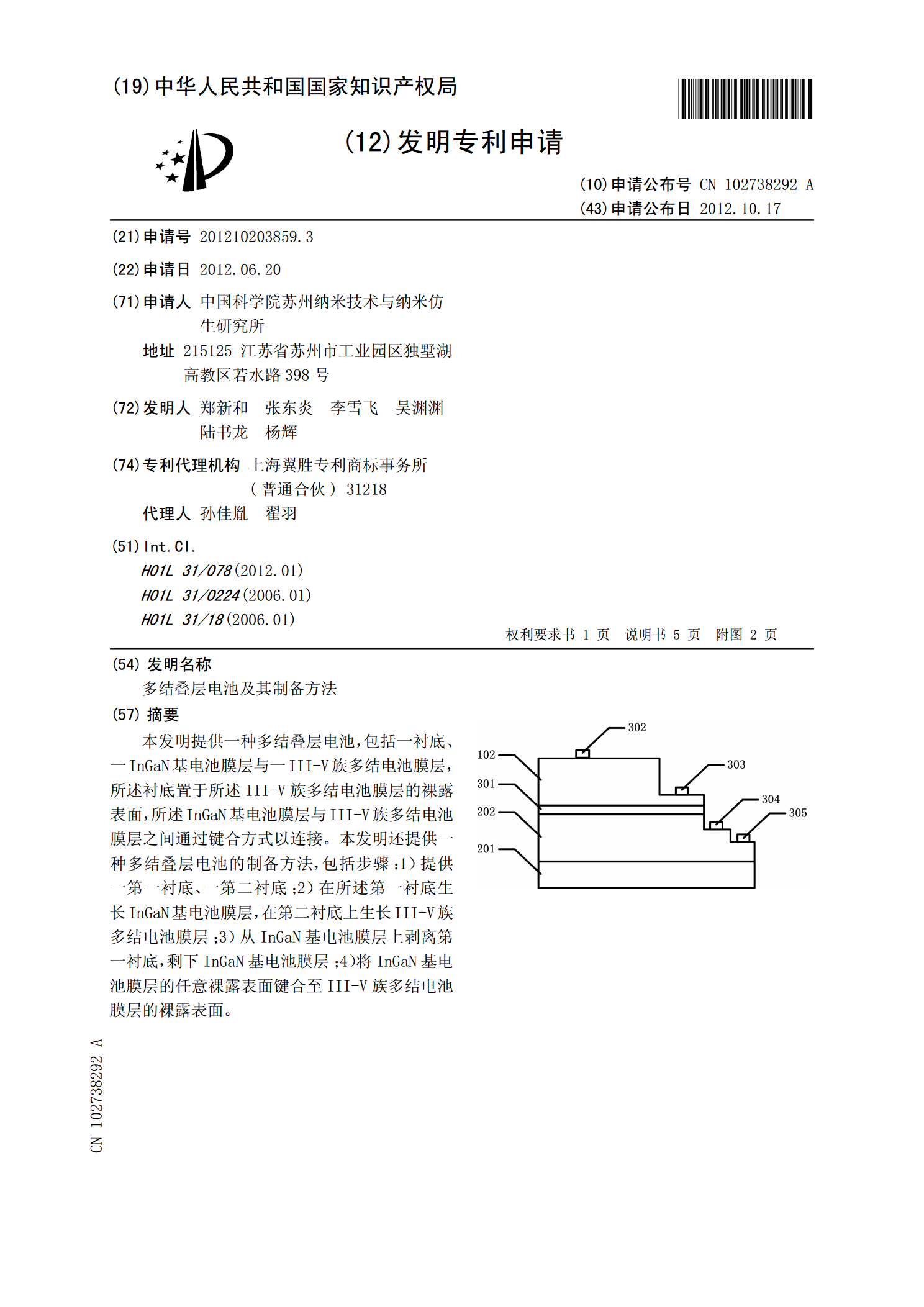

本发明提供一种多结叠层电池,包括一衬底、一InGaN基电池膜层与一III-V族多结电池膜层,所述衬底置于所述III-V族多结电池膜层的裸露表面,所述InGaN基电池膜层与III-V族多结电池膜层之间通过键合方式以连接。本发明还提供一种多结叠层电池的制备方法,包括步骤:1)提供一第一衬底、一第二衬底;2)在所述第一衬底生长InGaN基电池膜层,在第二衬底上生长III-V族多结电池膜层;3)从InGaN基电池膜层上剥离第一衬底,剩下InGaN基电池膜层;4)将InGaN基电池膜层的任意裸露表面键合至III-V

钝化叠层电池及其制备方法.pdf

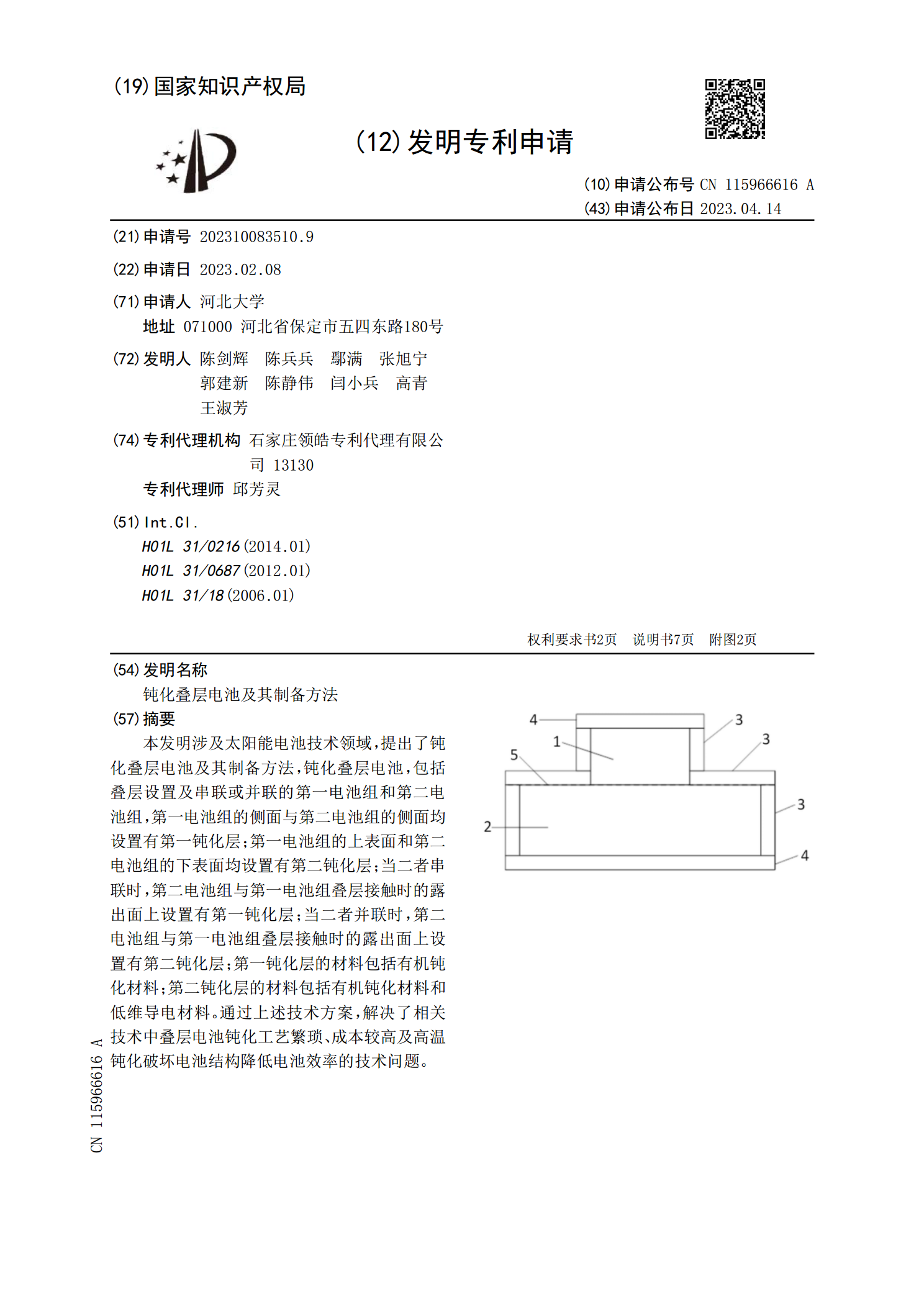

本发明涉及太阳能电池技术领域,提出了钝化叠层电池及其制备方法,钝化叠层电池,包括叠层设置及串联或并联的第一电池组和第二电池组,第一电池组的侧面与第二电池组的侧面均设置有第一钝化层;第一电池组的上表面和第二电池组的下表面均设置有第二钝化层;当二者串联时,第二电池组与第一电池组叠层接触时的露出面上设置有第一钝化层;当二者并联时,第二电池组与第一电池组叠层接触时的露出面上设置有第二钝化层;第一钝化层的材料包括有机钝化材料;第二钝化层的材料包括有机钝化材料和低维导电材料。通过上述技术方案,解决了相关技术中叠层电池