硅基集成量子芯片、制备及测试方法.pdf

fa****楠吖

亲,该文档总共13页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

硅基集成量子芯片、制备及测试方法.pdf

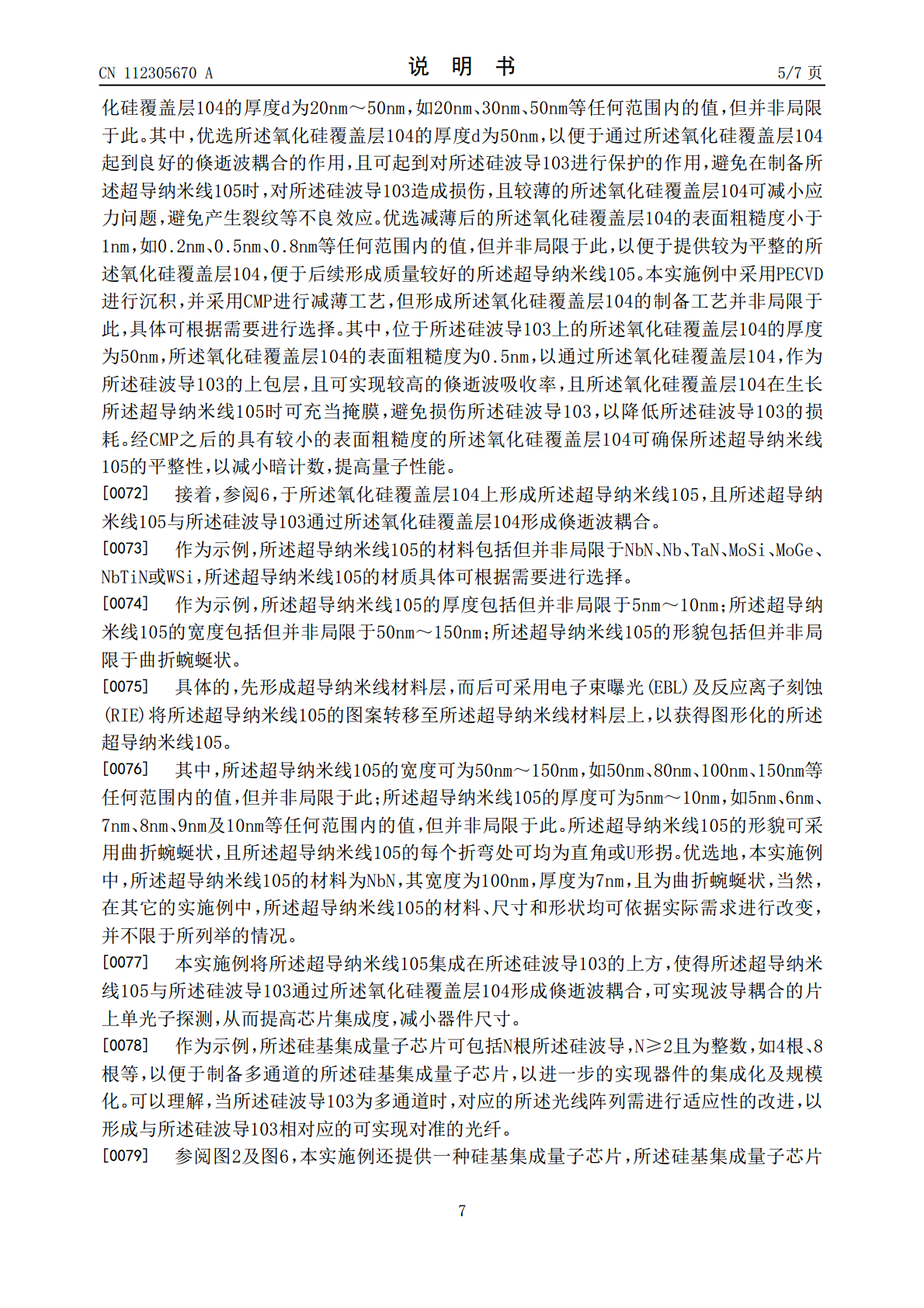

本发明提供一种硅基集成量子芯片、制备及测试方法,将超导纳米线集成在硅波导的上方,使得超导纳米线与硅波导通过氧化硅覆盖层形成倏逝波耦合,可实现波导耦合的片上单光子探测;通过位于超导纳米线与硅波导之间的氧化硅覆盖层,可实现较高的倏逝波吸收率,且氧化硅覆盖层在生长超导纳米线时可充当掩膜,避免损伤硅波导,以降低硅波导的损耗;经CMP之后的具有较小的表面粗糙度的氧化硅覆盖层可确保超导纳米线的平整性,以减小暗计数,提高量子性能;可制备多通道的硅基集成量子芯片。本发明可实现集成化、规模化,并可靠保持高保真度的单光子信号

硅基集成量子光学芯片研究的任务书.docx

硅基集成量子光学芯片研究的任务书任务书:硅基集成量子光学芯片研究一、研究背景和意义近年来,量子光学在信息科学、精密测量和量子计算等领域引起了越来越多的关注。硅基微纳光电子技术是快速发展的技术之一,具有制造复杂集成电路的优异性能。就微电子行业而言,芯片的制造已经进入了纳米尺度,但是在光子学领域,我们还没有达到这一水平。硅基集成量子光学芯片的研究,可以在光子学领域继续超越电子学,实现单光子自洽处理、量子纠缠和光量子计算等功能,实现单光子器件的现实应用。二、研究目标本研究主要目标是使用硅基微纳加工技术实现硅基集

硅基光分路集成芯片、集成化光纤陀螺、制备及连接方法.pdf

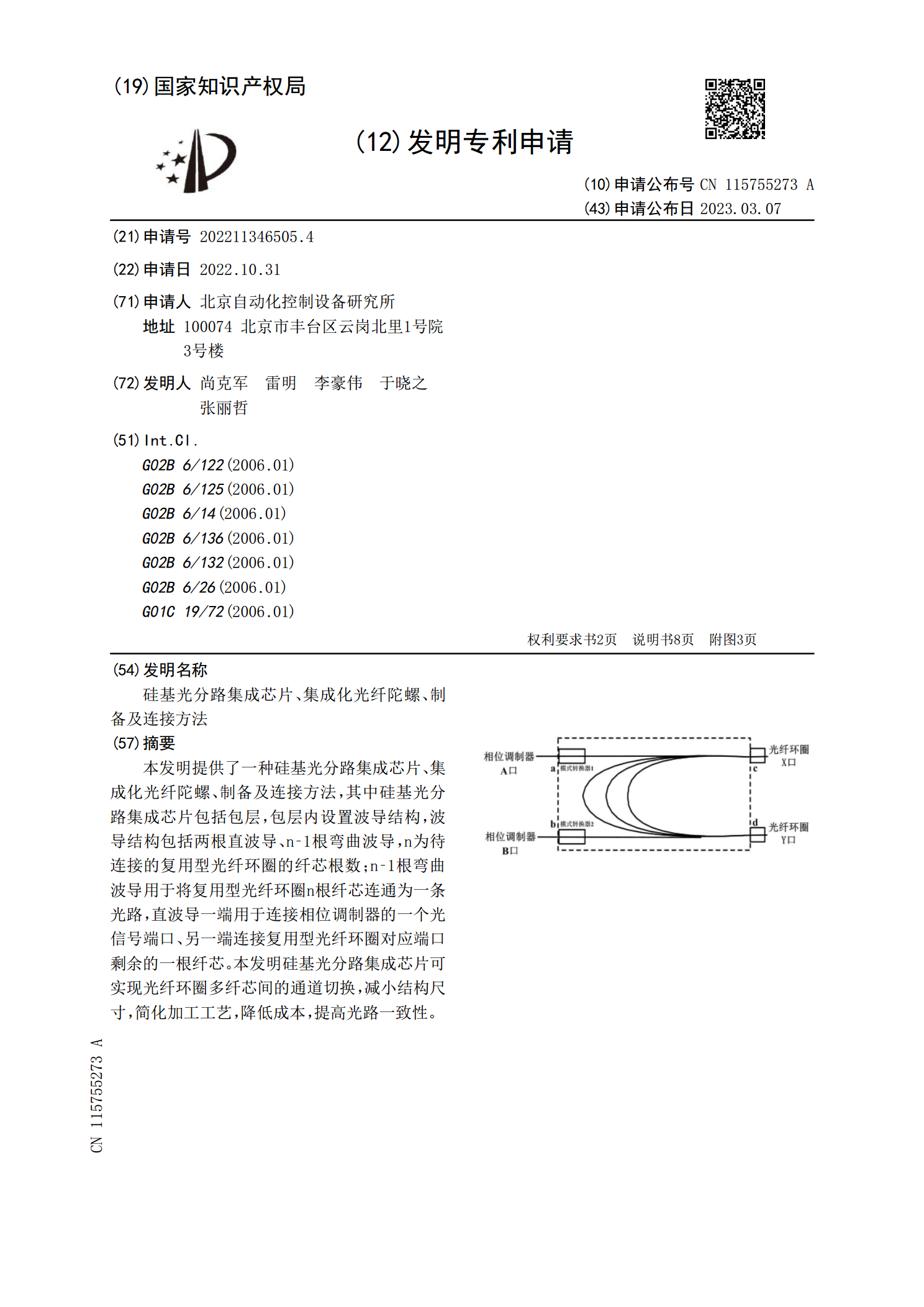

本发明提供了一种硅基光分路集成芯片、集成化光纤陀螺、制备及连接方法,其中硅基光分路集成芯片包括包层,包层内设置波导结构,波导结构包括两根直波导、n‑1根弯曲波导,n为待连接的复用型光纤环圈的纤芯根数;n‑1根弯曲波导用于将复用型光纤环圈n根纤芯连通为一条光路,直波导一端用于连接相位调制器的一个光信号端口、另一端连接复用型光纤环圈对应端口剩余的一根纤芯。本发明硅基光分路集成芯片可实现光纤环圈多纤芯间的通道切换,减小结构尺寸,简化加工工艺,降低成本,提高光路一致性。

硅基集成量子光学芯片实验研究的任务书.docx

硅基集成量子光学芯片实验研究的任务书任务书一、研究背景光子学作为一门新兴的交叉学科,正逐渐成为信息科学和通信技术领域中最为前沿的研究方向之一。量子光学作为光子学的一个分支,致力于研究光的量子性质,如光的粒子性、波粒二象性、量子纠缠等,以及光子与其它量子系统的相互作用和量子信息的处理与传输等问题。而集成光子学作为一种新兴的技术与微电子集成电路技术相似,标志着光子学实验趋于大规模、自动化和可靠化。硅基集成量子光学芯片就是一种新型的集成平台,可以实现更复杂的量子光学功能和更严格的控制,有望在量子计算、量子通信、

硅基光量子芯片上量子调控技术和量子信息应用.docx

硅基光量子芯片上量子调控技术和量子信息应用硅基光量子芯片上量子调控技术和量子信息应用摘要:随着量子信息科学的发展,量子调控技术在量子信息处理领域中扮演着关键角色。硅基光量子芯片作为一种重要的量子调控平台,具有出色的操控性能和稳定性,对于实现高度可控的量子信息处理具有潜在的应用价值。本文主要探讨了硅基光量子芯片上的量子调控技术及其相关的量子信息应用,包括硅基光子的单光子源、量子存储和量子计算等方面。1.简介量子调控是指通过精确地操控量子系统的态和相互作用,实现对量子信息的控制和处理。硅基光量子芯片凭借其优异