超结器件终端结构及其制备方法.pdf

小琛****82

亲,该文档总共15页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

超结器件终端结构及其制备方法.pdf

本发明提供一种超结器件终端结构及其制备方法,终端结构包括:半导体衬底;外延层,位于半导体衬底的表面,外延层包括若干个交替排列的n型柱及p型柱;厚氧化层,覆盖于外延层表面,在每相邻两个p型柱之间对应位置的厚氧化层上设置有贯穿槽;栅氧化层,位于外延层表面;多晶硅栅,位于贯穿槽内。本发明在基本保持源漏击穿电压与导通电阻不变的前提下,在超结器件终端区增加多晶硅栅结构,通过调整多晶硅栅在所述超结器件终端区的面积,可以在较低的源漏偏压下引入更多缓变的栅漏电容,使得超结器件的栅漏电容曲线突变区变缓,进而改善超结器件的电

超结功率器件及其制备方法.pdf

本发明提供一种超结功率器件及其制备方法,在制备超结功率器件时,可在形成第一导电类型外延层之后通过添加超结掩膜版、在形成第二导电类型阱区之前或之后直接通过阱区掩膜版,以及在形成接触结构之前或之后直接通过接触掩膜版,即可在第一导电类型外延层内注入第二导电类型杂质,以依次形成第二导电类型浮岛及第二导电类型柱,该制备工艺无需进行多次外延工艺,且无需进行深沟道刻蚀,因此制备工艺简单、成本低,且成品率及可靠性较高。本发明的超结功率器件同时具有第二导电类型浮岛及第二导电类型柱,在断路状态,可提高功率器件的击穿电压,降低

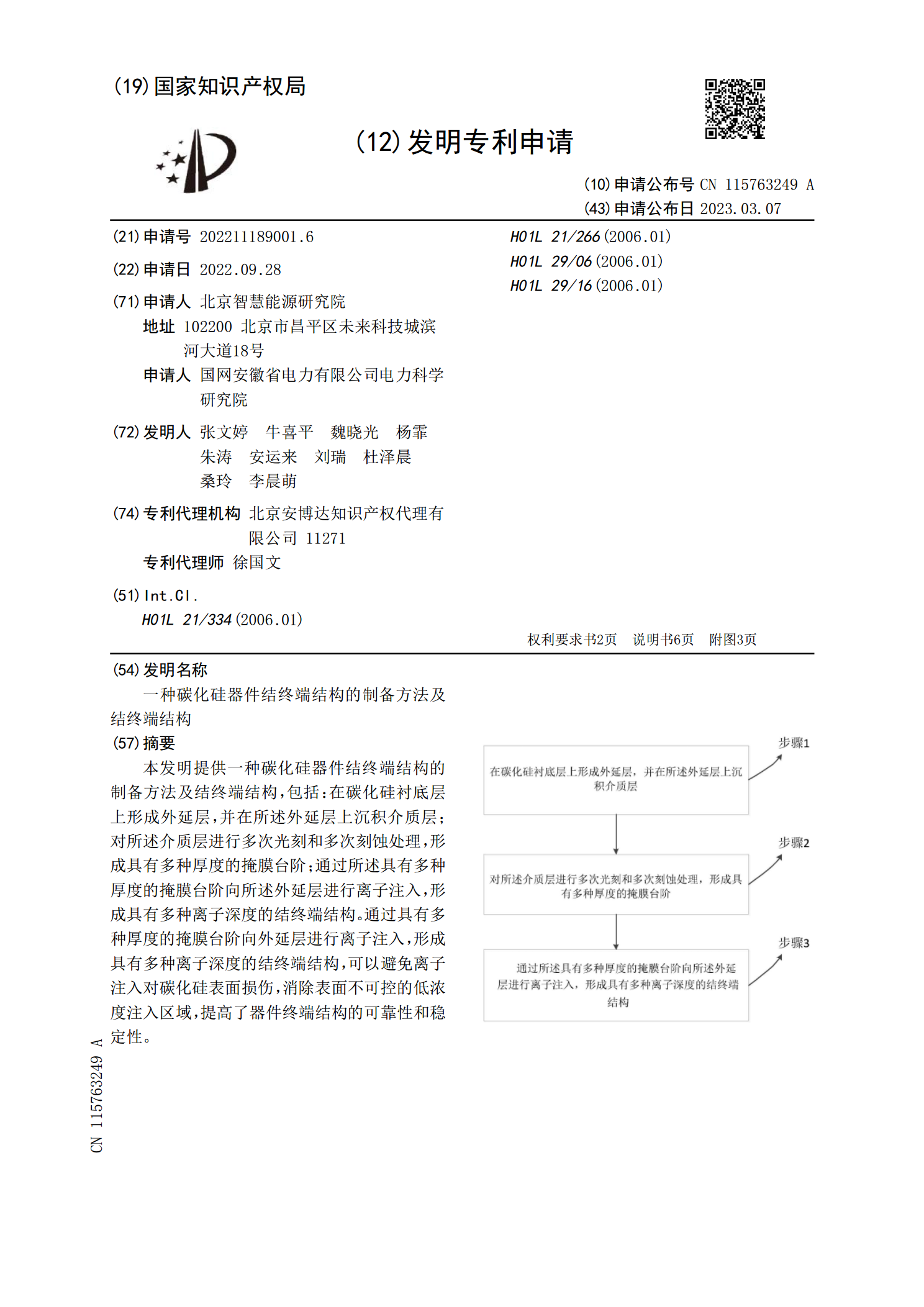

一种碳化硅器件结终端结构的制备方法及结终端结构.pdf

本发明提供一种碳化硅器件结终端结构的制备方法及结终端结构,包括:在碳化硅衬底层上形成外延层,并在所述外延层上沉积介质层;对所述介质层进行多次光刻和多次刻蚀处理,形成具有多种厚度的掩膜台阶;通过所述具有多种厚度的掩膜台阶向所述外延层进行离子注入,形成具有多种离子深度的结终端结构。通过具有多种厚度的掩膜台阶向外延层进行离子注入,形成具有多种离子深度的结终端结构,可以避免离子注入对碳化硅表面损伤,消除表面不可控的低浓度注入区域,提高了器件终端结构的可靠性和稳定性。

集成TMBS结构的超结MOS器件及其制造方法.pdf

本发明公开了一种集成TMBS结构的超结MOS器件及其制造方法,其中超结MOS器件包括超结MOS器件本体,超结MOS器件本体中部分元胞之间并联集成有TMBS结构。本发明实施例提供的集成TMBS结构的超结MOS器件制造方法,通过在超结MOS器件本体中部分元胞之间并联集成TMBS结构,来极大的改善超结MOS器件的反向恢复特性,解决由于较高的反向恢复峰值电流等导致的超结MOS器件容易损坏,进而降低使用安全性的问题,提高了超结MOS器件在使用过程中的安全性。其在不增加工艺步骤的基础上,在超结MOS器件本体中的两个或

超结器件及其制造方法.pdf

本发明公开了一种超结器件,包括形成于超结结构的N型柱顶部的沟槽栅,沟道区的掺杂包括在源极对应的接触孔的开口形成后、金属填充前进行带倾角的P型离子注入形成的P型离子注入杂质,P型离子注入的注入峰值的纵向深度小于等于栅极沟槽的底部表面深度,P型离子注入使沟道区的底部形成一个深度从栅极沟槽的底部到P型柱逐渐变深的轮廓结构,沟道区的底部轮廓使超结器件单元的碰撞电离最强区域从多晶硅栅侧面覆盖位置下探到沟道区的底部轮廓区域,用以提升器件的EAS能力。本发明还公开了一种超结器件的制造方法。本发明能提高器件的EAS能力。