具有ESD防护器件的半导体结构的制备方法.pdf

书生****22

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

具有ESD防护器件的半导体结构的制备方法.pdf

本申请提供一种具有ESD防护器件的半导体结构的制备方法,在半导体衬底上形成包括位于半导体衬底上的ESD栅极结构的ESD防护器件,而后形成覆盖半导体衬底及ESD防护器件的层间电介质结构,层间电介质结构包括采用沉积工艺及回流工艺形成的BPSG层,且BPSG层中B元素及P元素的重量百分比均大于4%,而后于层间电介质结构上形成图形化的光阻层,并刻蚀层间电介质结构形成接触孔。本申请制备的BPSG层具有良好的流动性,回流工艺后可有效减小ESD防护器件拐角区处层间电介质结构的斜率,从而可增加ESD防护器件拐角区处光阻层

半导体器件结构及制备方法.pdf

本发明公开了一种半导体器件结构及制备方法,半导体器件结构的制备方法包括:提供衬底,所述衬底包括第一区域及与所述第一区域相邻接的第二区域;于所述衬底内形成字线沟槽,所述字线沟槽贯穿所述第一区域及所述第二区域;于所述字线沟槽内形成埋入式栅极字线,所述栅极字线包括字线导电层,所述字线导电层贯穿所述第一区域及所述第二区域,且位于所述第二区域的所述字线导电层的厚度大于位于第一区域的所述字线导电层的厚度,以形成台阶状的字线导电层,在完成制备埋入式栅极字线后可以确保形成在第二区域的第一互连孔能够暴露出字线导电层,从而确

半导体器件结构及制备方法.pdf

本发明提供一种半导体器件结构及制备方法,制备方法包括提供一半导体基底,形成第一金属层;于第一金属层内形成第一沟槽,于第一沟槽内及周围沉积第一层间介质层;形成第一氢遮挡层;于第一氢遮挡层及第一层间介质层内形第一插塞;形成由下电极层、阻变氧化层及上电极层构成的且与第一插塞相连接的叠层结构;于叠层结构上形成连续的第二氢遮挡层,形成第二层间介质层。本发明通过第一氢遮挡层及第二氢遮挡层的设计,保护了下电极层、阻变氧化层及上电极层,防止阻变氧化层受环境及制程的影响,阻止了对器件的金属层及确保晶体管特性的退火工艺对阻变

浅析ESD防护与ESD防护器件.pdf

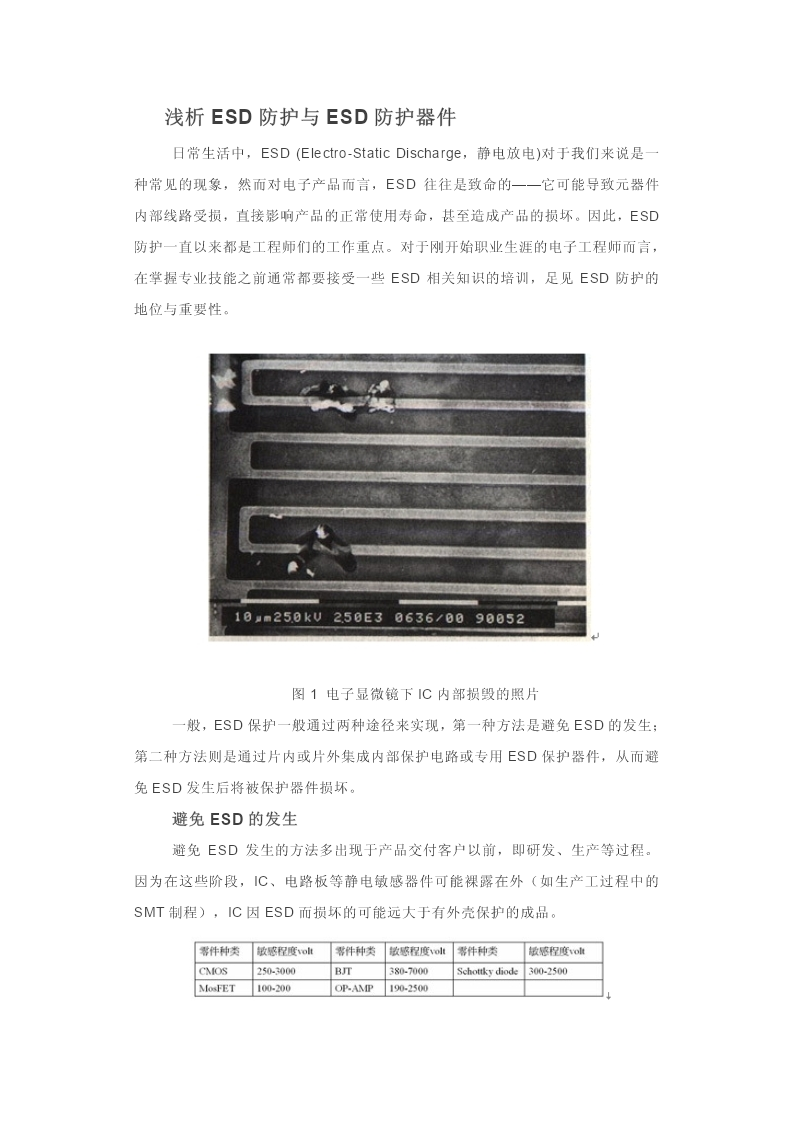

浅析ESD防护与ESD防护器件日常生活中,ESD(Electro-StaticDischarge,静电放电)对于我们来说是一种常见的现象,然而对电子产品而言,ESD往往是致命的——它可能导致元器件内部线路受损,直接影响产品的正常使用寿命,甚至造成产品的损坏。因此,ESD防护一直以来都是工程师们的工作重点。对于刚开始职业生涯的电子工程师而言,在掌握专业技能之前通常都要接受一些ESD相关知识的培训,足见ESD防护的地位与重要性。图1电子显微镜下IC内部损毁的照片一般,ESD保护一般通过两种途径来实现,第一种方

具有氧化镓纳米结构的硅晶圆器件及其制备方法、半导体器件.pdf

本发明涉及具有氧化镓纳米结构的硅晶圆器件及其制备方法、半导体器件。该制备方法包括:提供硅晶圆,硅晶圆包括依次层叠设置的硅顶层、掩埋氧化物层及硅基底层;将硅晶圆进行刻蚀,刻蚀方向为由硅顶层向掩埋氧化物层的垂直方向,得到具有凹槽的结构化复合衬底,凹槽包括贯穿硅顶层的第一凹槽,以及由第一凹槽延伸至掩埋氧化物层内部形成的第二凹槽,第二凹槽的深度小于掩埋氧化物层厚度;将结构化复合衬底在碳纳米材料、镓源及氧源环境条件下进行化学气相沉积,使镓源在第一凹槽内沉积生长,得到具有氧化镓纳米结构的硅晶圆器件。该制备方法使硅晶圆