低射频损耗硅基氮化镓高电子迁移率晶体管及其制作方法.pdf

Jo****34

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

低射频损耗硅基氮化镓高电子迁移率晶体管及其制作方法.pdf

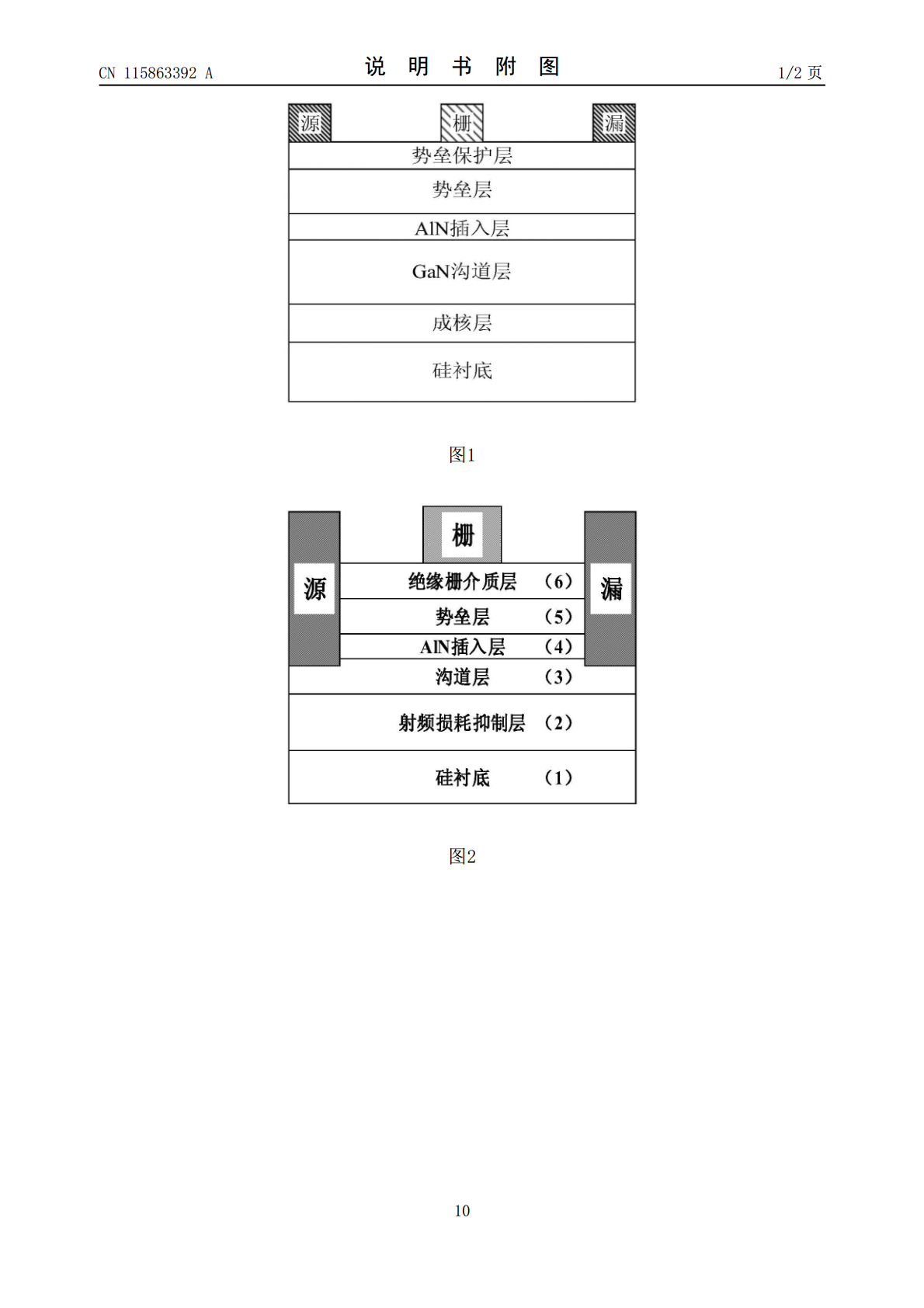

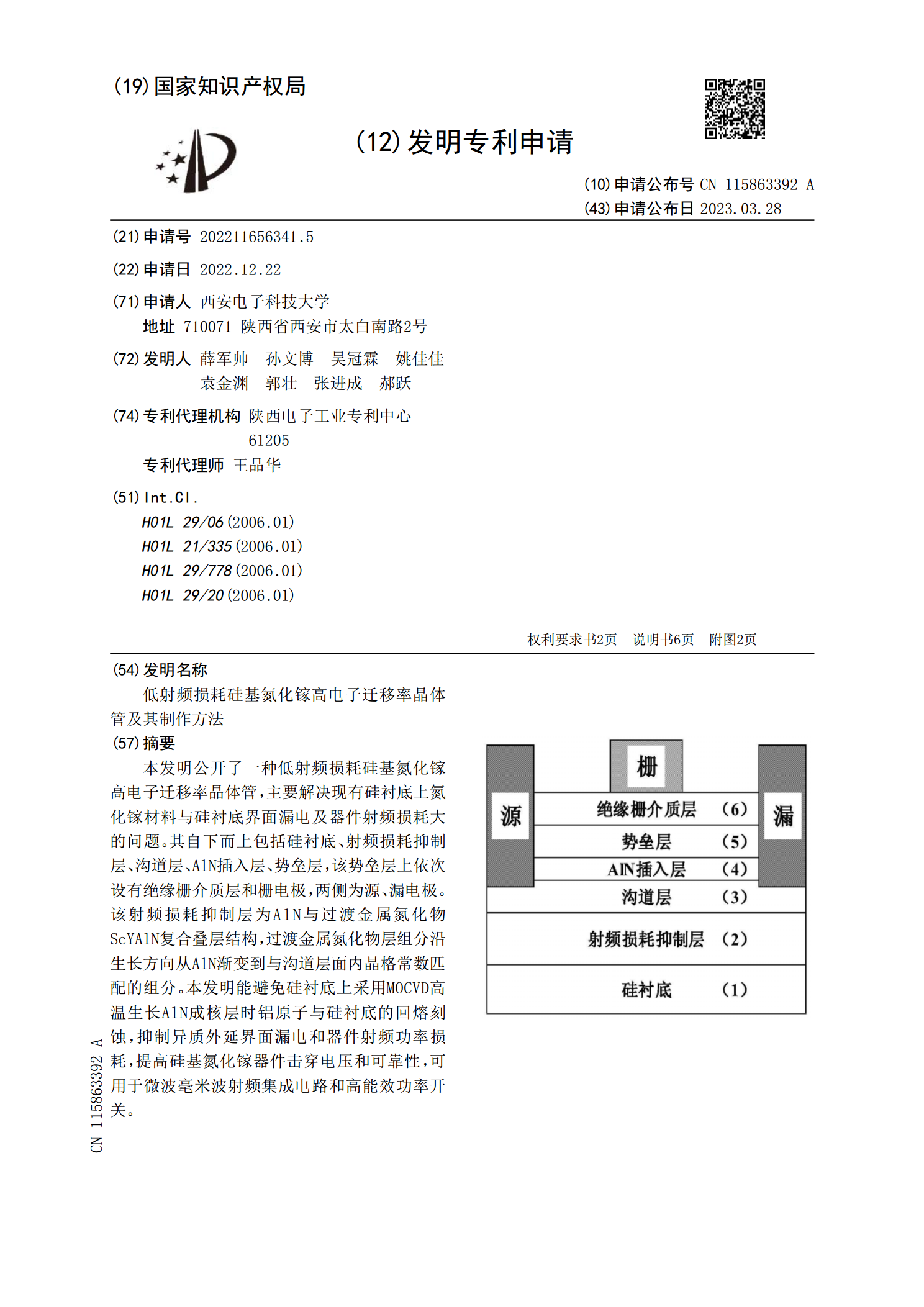

本发明公开了一种低射频损耗硅基氮化镓高电子迁移率晶体管,主要解决现有硅衬底上氮化镓材料与硅衬底界面漏电及器件射频损耗大的问题。其自下而上包括硅衬底、射频损耗抑制层、沟道层、AlN插入层、势垒层,该势垒层上依次设有绝缘栅介质层和栅电极,两侧为源、漏电极。该射频损耗抑制层为AlN与过渡金属氮化物ScYAlN复合叠层结构,过渡金属氮化物层组分沿生长方向从AlN渐变到与沟道层面内晶格常数匹配的组分。本发明能避免硅衬底上采用MOCVD高温生长AlN成核层时铝原子与硅衬底的回熔刻蚀,抑制异质外延界面漏电和器件射频功率

氮化镓基高电子迁移率晶体管及其制备方法.pdf

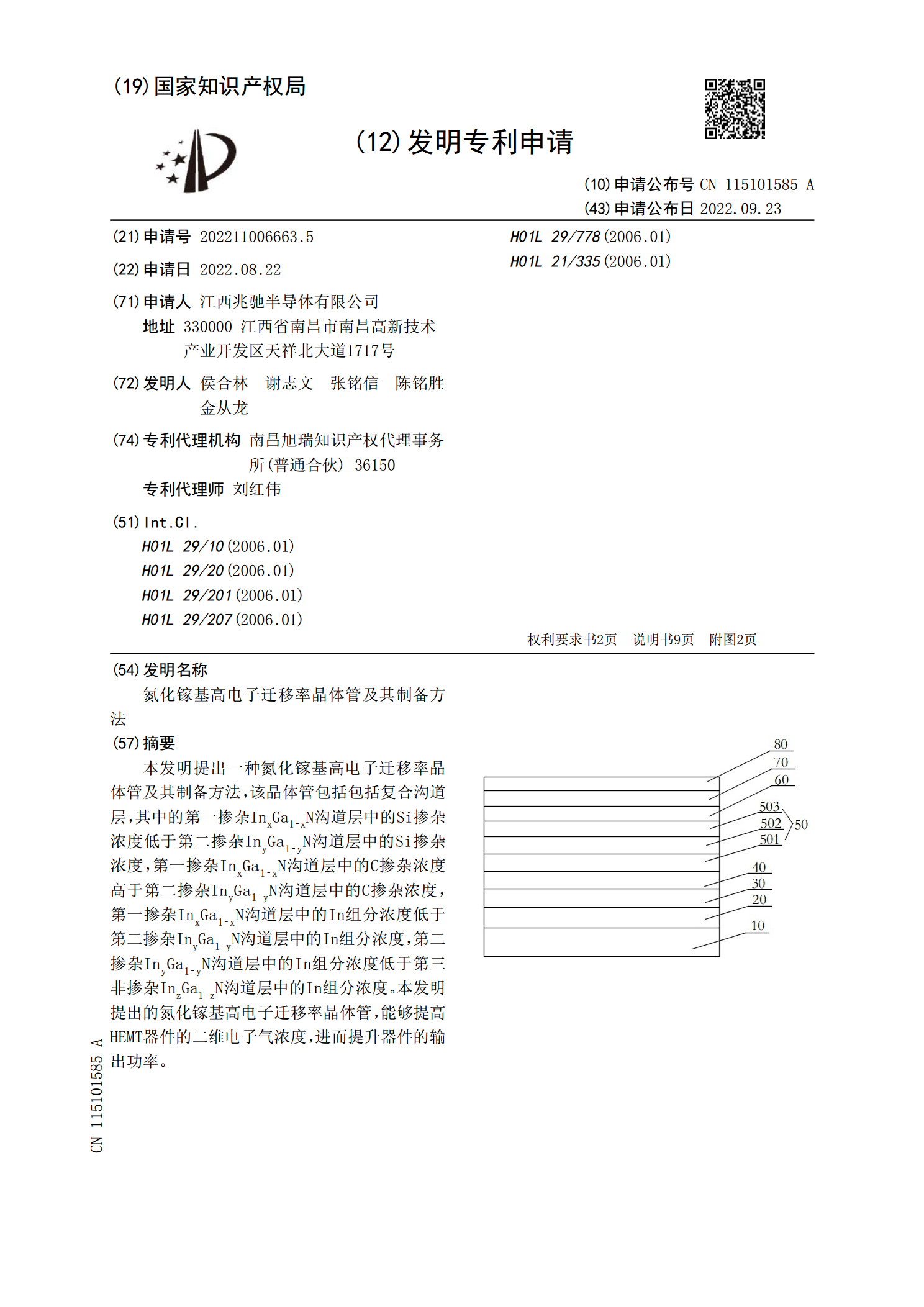

本发明提出一种氮化镓基高电子迁移率晶体管及其制备方法,该晶体管包括包括复合沟道层,其中的第一掺杂In<base:Sub>x</base:Sub>Ga<base:Sub>1?x</base:Sub>N沟道层中的Si掺杂浓度低于第二掺杂In<base:Sub>y</base:Sub>Ga<base:Sub>1?y</base:Sub>N沟道层中的Si掺杂浓度,第一掺杂In<base:Sub>x</base:Sub>Ga<base:Sub>1?x</base:Sub>N沟道层中的C掺杂浓度高于第二掺杂In<ba

氮化镓基高电子迁移率晶体管的栅电极.pdf

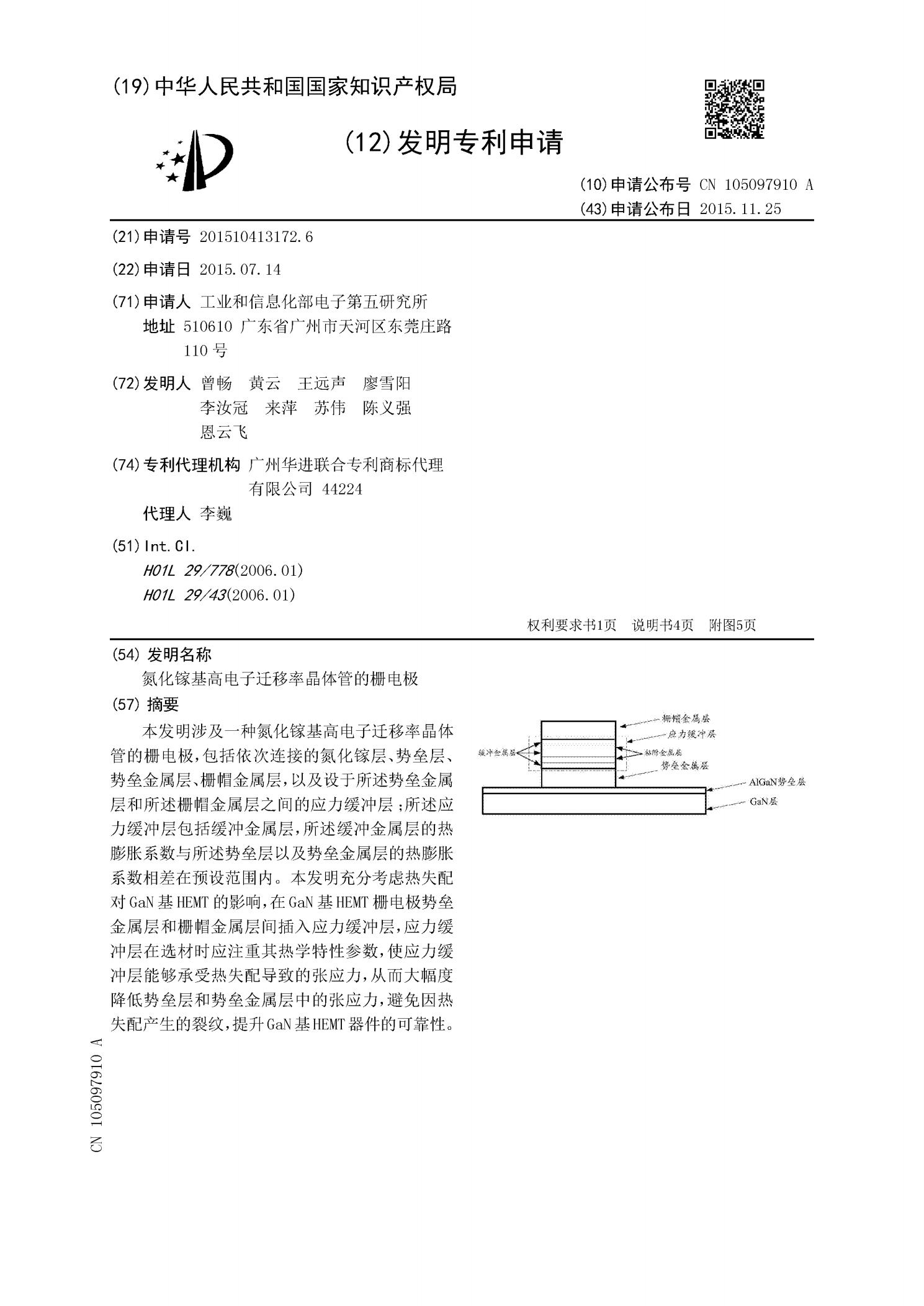

本发明涉及一种氮化镓基高电子迁移率晶体管的栅电极,包括依次连接的氮化镓层、势垒层、势垒金属层、栅帽金属层,以及设于所述势垒金属层和所述栅帽金属层之间的应力缓冲层;所述应力缓冲层包括缓冲金属层,所述缓冲金属层的热膨胀系数与所述势垒层以及势垒金属层的热膨胀系数相差在预设范围内。本发明充分考虑热失配对GaN基HEMT的影响,在GaN基HEMT栅电极势垒金属层和栅帽金属层间插入应力缓冲层,应力缓冲层在选材时应注重其热学特性参数,使应力缓冲层能够承受热失配导致的张应力,从而大幅度降低势垒层和势垒金属层中的张应力,避

氮化镓基高电子迁移率晶体管栅电流输运机制研究.docx

氮化镓基高电子迁移率晶体管栅电流输运机制研究氮化镓(GaN)基高电子迁移率晶体管(HEMT)因其高频性能和功率密度优势而备受关注,被广泛应用于无线通信、雷达、微波炉、汽车雷达等领域。其中,GaN材料的高导电性和高电子迁移率是其成为HEMT的优势之一。因此,探究GaN基HEMT的栅电流输运机制具有重要的理论和实际意义。HEMT是一种常用的半导体器件,晶体管的操作依赖于从源到漏的电流。GaN基HEMT的栅电流主要由漏极电流、压电效应电流和反向漏极电流等组成,其中,压电效应电流是GaN结构中非常独特的一种电场效

一种氮化镓高电子迁移率晶体管及其制造方法.pdf

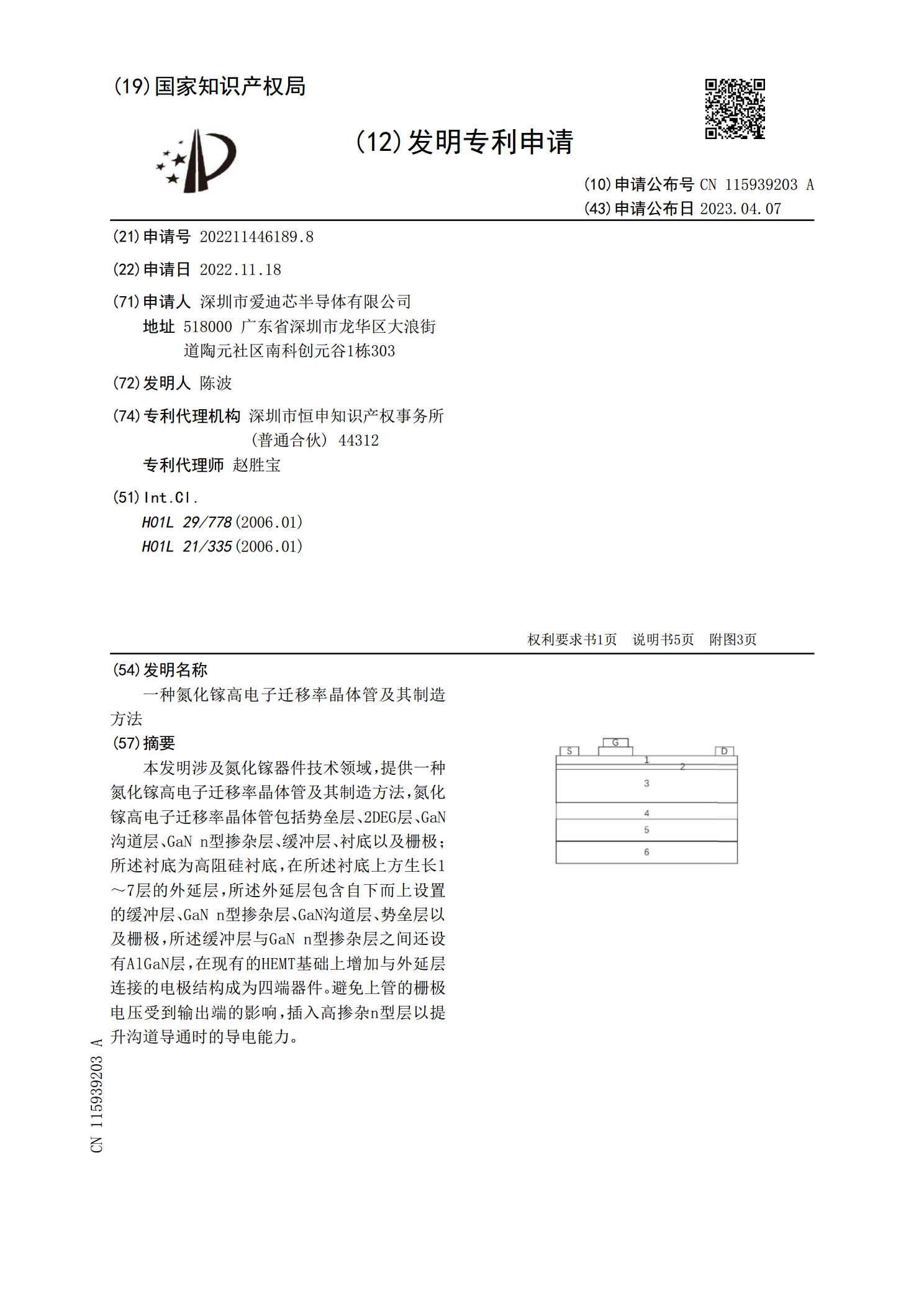

本发明涉及氮化镓器件技术领域,提供一种氮化镓高电子迁移率晶体管及其制造方法,氮化镓高电子迁移率晶体管包括势垒层、2DEG层、GaN沟道层、GaNn型掺杂层、缓冲层、衬底以及栅极;所述衬底为高阻硅衬底,在所述衬底上方生长1~7层的外延层,所述外延层包含自下而上设置的缓冲层、GaNn型掺杂层、GaN沟道层、势垒层以及栅极,所述缓冲层与GaNn型掺杂层之间还设有AlGaN层,在现有的HEMT基础上增加与外延层连接的电极结构成为四端器件。避免上管的栅极电压受到输出端的影响,插入高掺杂n型层以提升沟道导通时的