一种氮化镓高电子迁移率晶体管及其制造方法.pdf

睿德****找我

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种氮化镓高电子迁移率晶体管及其制造方法.pdf

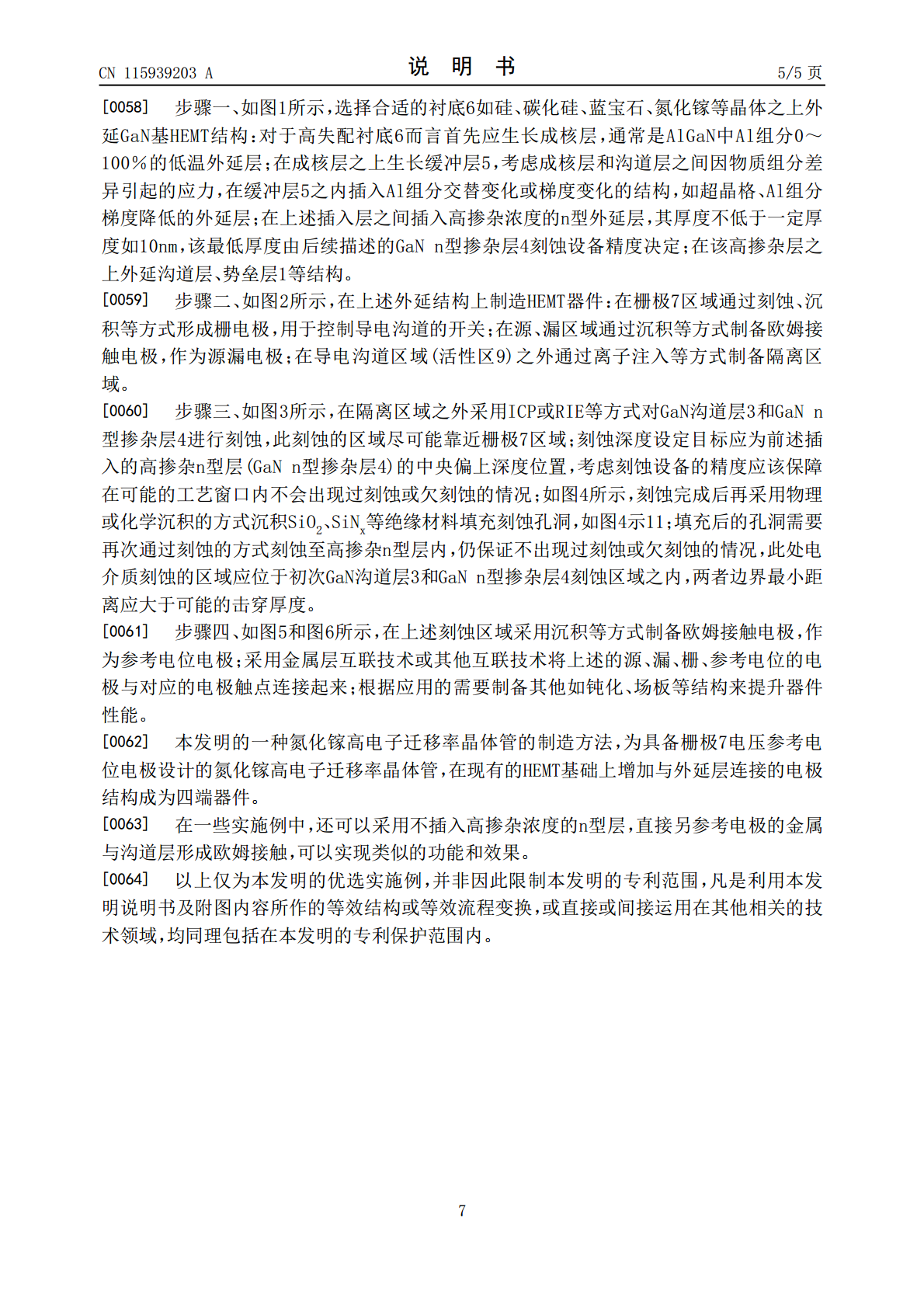

本发明涉及氮化镓器件技术领域,提供一种氮化镓高电子迁移率晶体管及其制造方法,氮化镓高电子迁移率晶体管包括势垒层、2DEG层、GaN沟道层、GaNn型掺杂层、缓冲层、衬底以及栅极;所述衬底为高阻硅衬底,在所述衬底上方生长1~7层的外延层,所述外延层包含自下而上设置的缓冲层、GaNn型掺杂层、GaN沟道层、势垒层以及栅极,所述缓冲层与GaNn型掺杂层之间还设有AlGaN层,在现有的HEMT基础上增加与外延层连接的电极结构成为四端器件。避免上管的栅极电压受到输出端的影响,插入高掺杂n型层以提升沟道导通时的

氮化镓基高电子迁移率晶体管及其制备方法.pdf

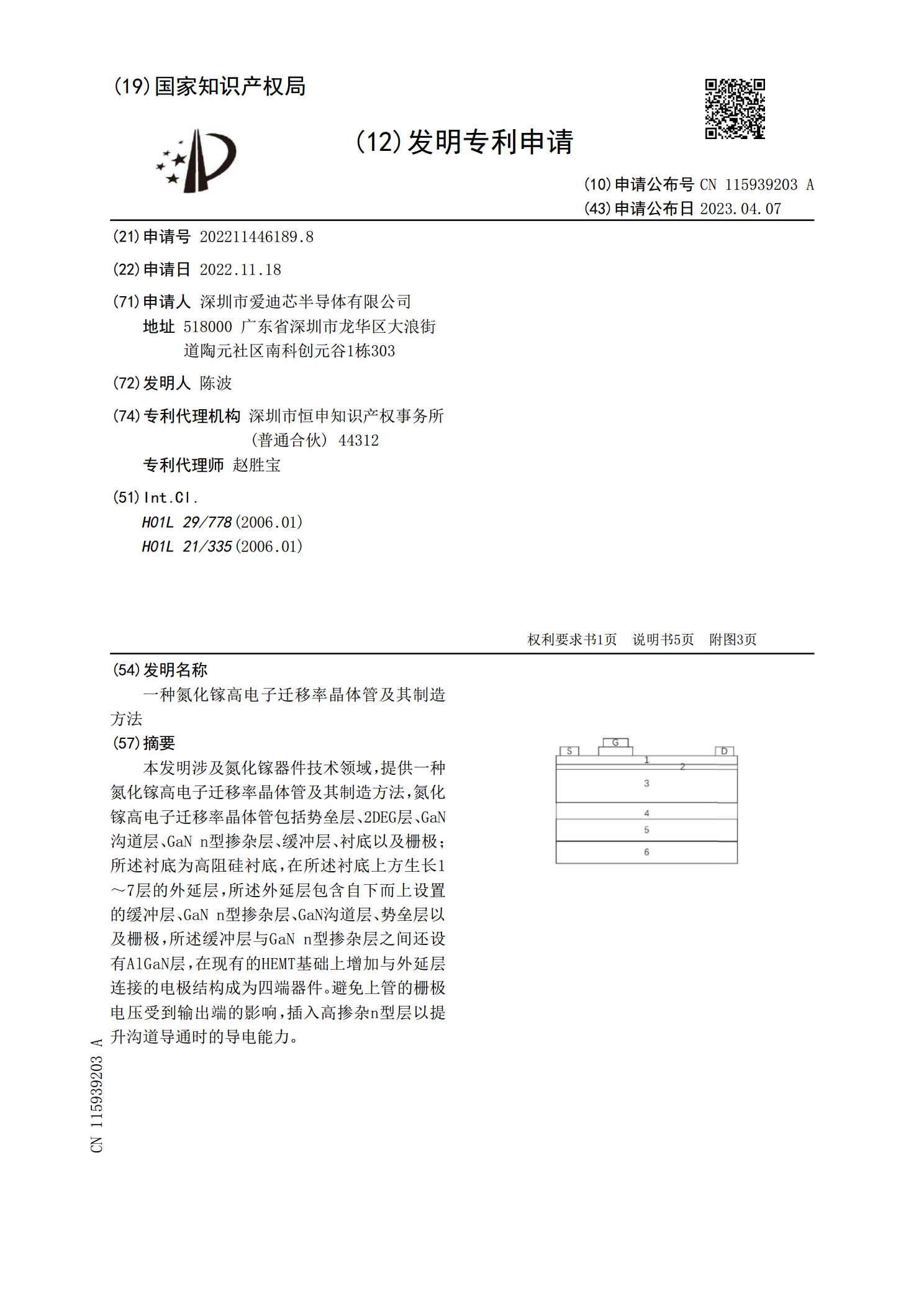

本发明提出一种氮化镓基高电子迁移率晶体管及其制备方法,该晶体管包括包括复合沟道层,其中的第一掺杂In<base:Sub>x</base:Sub>Ga<base:Sub>1?x</base:Sub>N沟道层中的Si掺杂浓度低于第二掺杂In<base:Sub>y</base:Sub>Ga<base:Sub>1?y</base:Sub>N沟道层中的Si掺杂浓度,第一掺杂In<base:Sub>x</base:Sub>Ga<base:Sub>1?x</base:Sub>N沟道层中的C掺杂浓度高于第二掺杂In<ba

一种氮化镓高电子迁移率晶体管.pdf

本发明公开了一种氮化镓高电子迁移率晶体管,该氮化镓高电子迁移率晶体管包括:包括:衬底层、缓冲层、本征氮化镓层、势垒层、源极、栅极、漏极以及复合帽层;在衬底层上为缓冲层,缓冲层上位本征氮化镓层,本征氮化镓层上位势垒层,势垒层上端两侧分别位金属电极源极和漏极;在势垒层与栅极之间设置复合帽层,所述复合帽层包括P‑GaN层和i‑GaN层,i‑GaN层位于势垒层上,P‑GaN层位于i‑GaN层上,P‑GaN层上位栅极;所述源极、栅极和漏极之间为钝化层;所述P‑GaN层、i‑GaN层和栅极的长度相同。通过通过引入i‑

基于范德华外延的氮化镓高电子迁移率晶体管器件及其制备方法.pdf

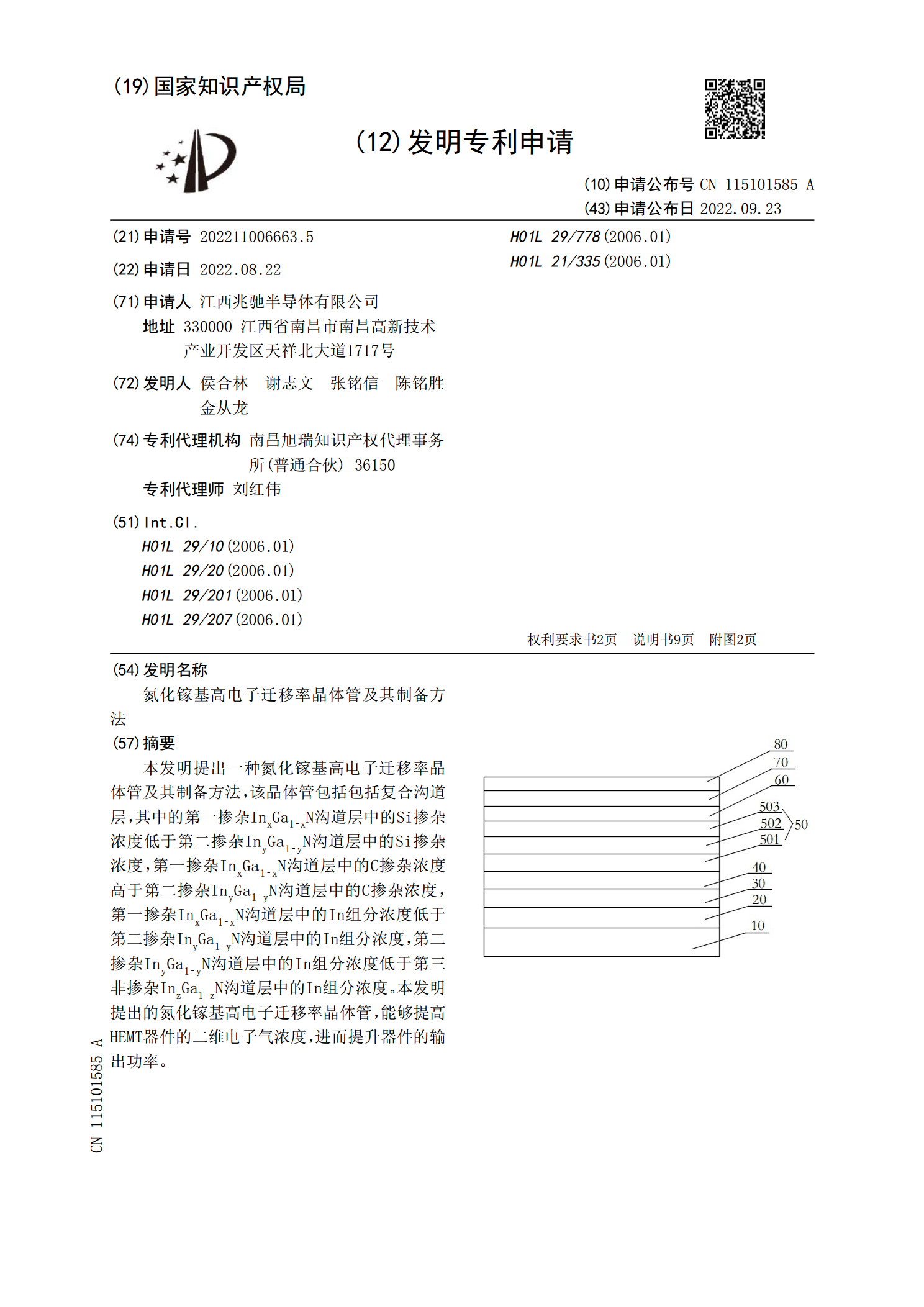

本发明公开了一种范德华外延的氮化镓高电子迁移率晶体管器件,主要解决了现有GaN‑HEMT器件击穿电压低的问题。其包括:衬底、本征GaN缓冲层、电流孔径、GaN沟道层、AlN层、AlGaN势垒层、P‑GaN帽层、源栅电极及钝化层;该本征GaN缓冲层与电流孔径之间,垂直设有两种不同掺杂浓度的第一P型GaN层和第二P型GaN层,以分别与本征GaN缓冲层形成PN结;该衬底与本征GaN缓冲层之间,垂直设有二维材料层、第一AlN层、第二AlN层和掺铁的GaN层;该二维材料层、第一AlN层、第二AlN层及衬底的中间开有

氮化镓基高电子迁移率晶体管的栅电极.pdf

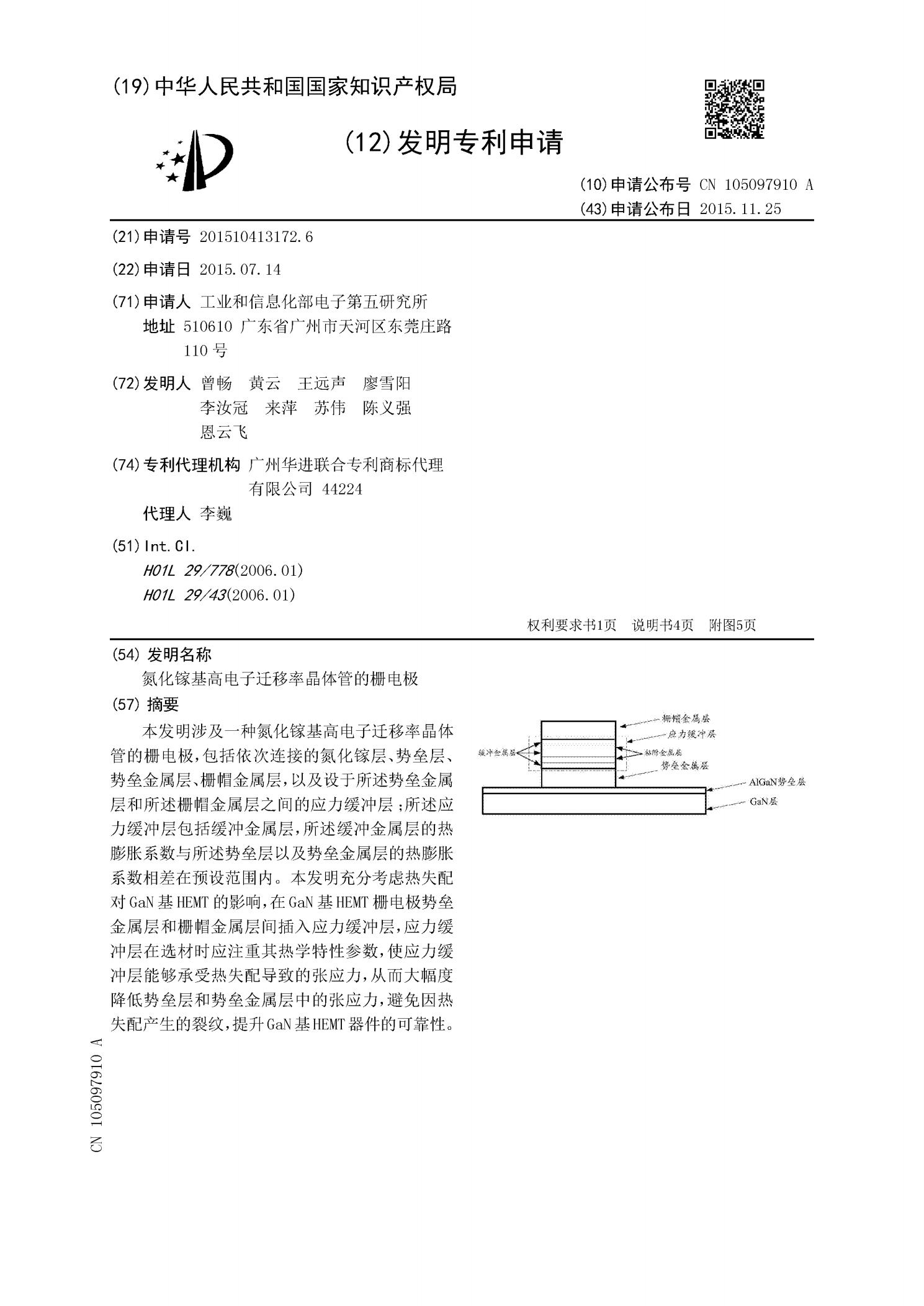

本发明涉及一种氮化镓基高电子迁移率晶体管的栅电极,包括依次连接的氮化镓层、势垒层、势垒金属层、栅帽金属层,以及设于所述势垒金属层和所述栅帽金属层之间的应力缓冲层;所述应力缓冲层包括缓冲金属层,所述缓冲金属层的热膨胀系数与所述势垒层以及势垒金属层的热膨胀系数相差在预设范围内。本发明充分考虑热失配对GaN基HEMT的影响,在GaN基HEMT栅电极势垒金属层和栅帽金属层间插入应力缓冲层,应力缓冲层在选材时应注重其热学特性参数,使应力缓冲层能够承受热失配导致的张应力,从而大幅度降低势垒层和势垒金属层中的张应力,避