光纤视频图像传输系统及传输方法.pdf

宜然****找我

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

光纤视频图像传输系统及传输方法.pdf

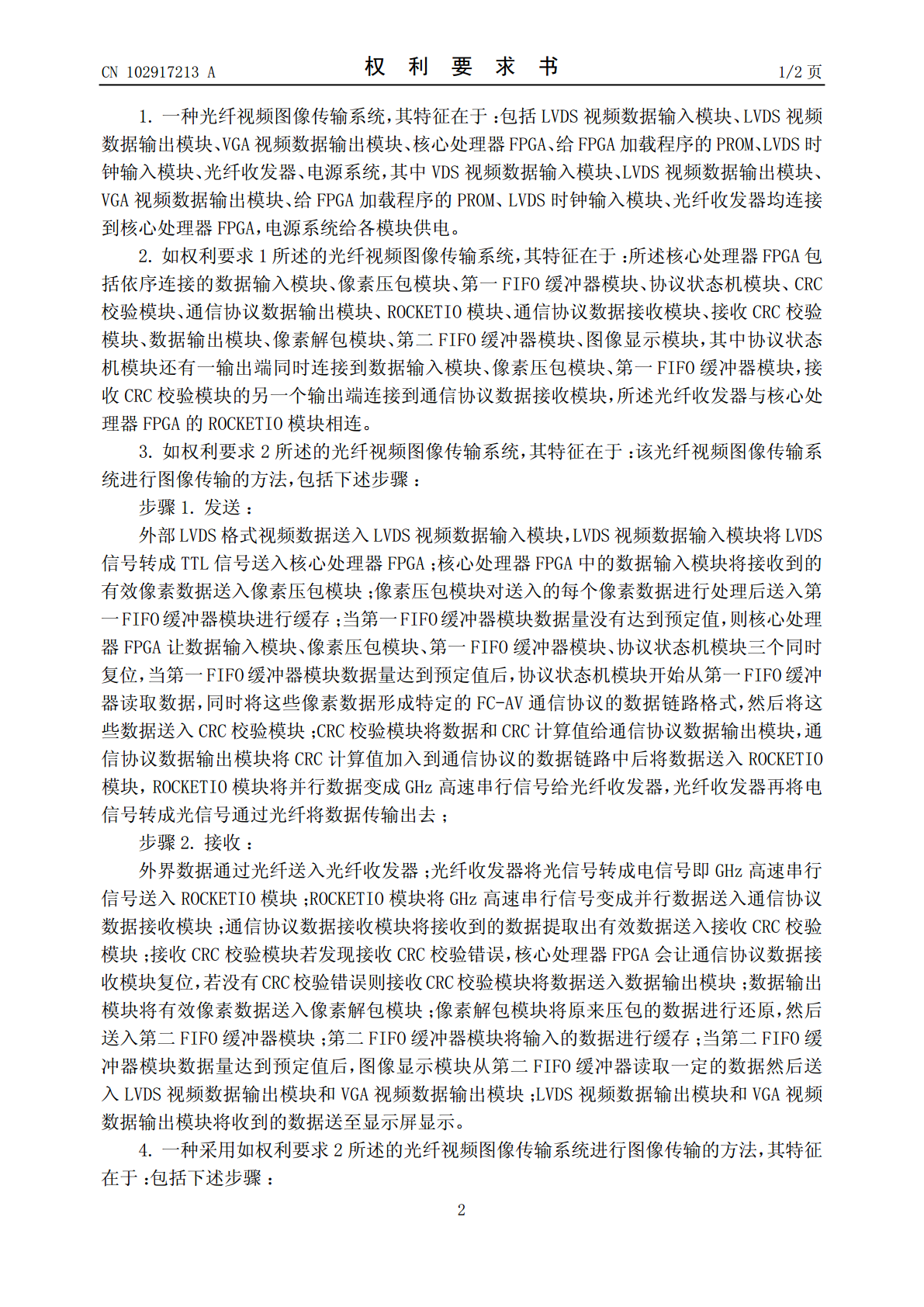

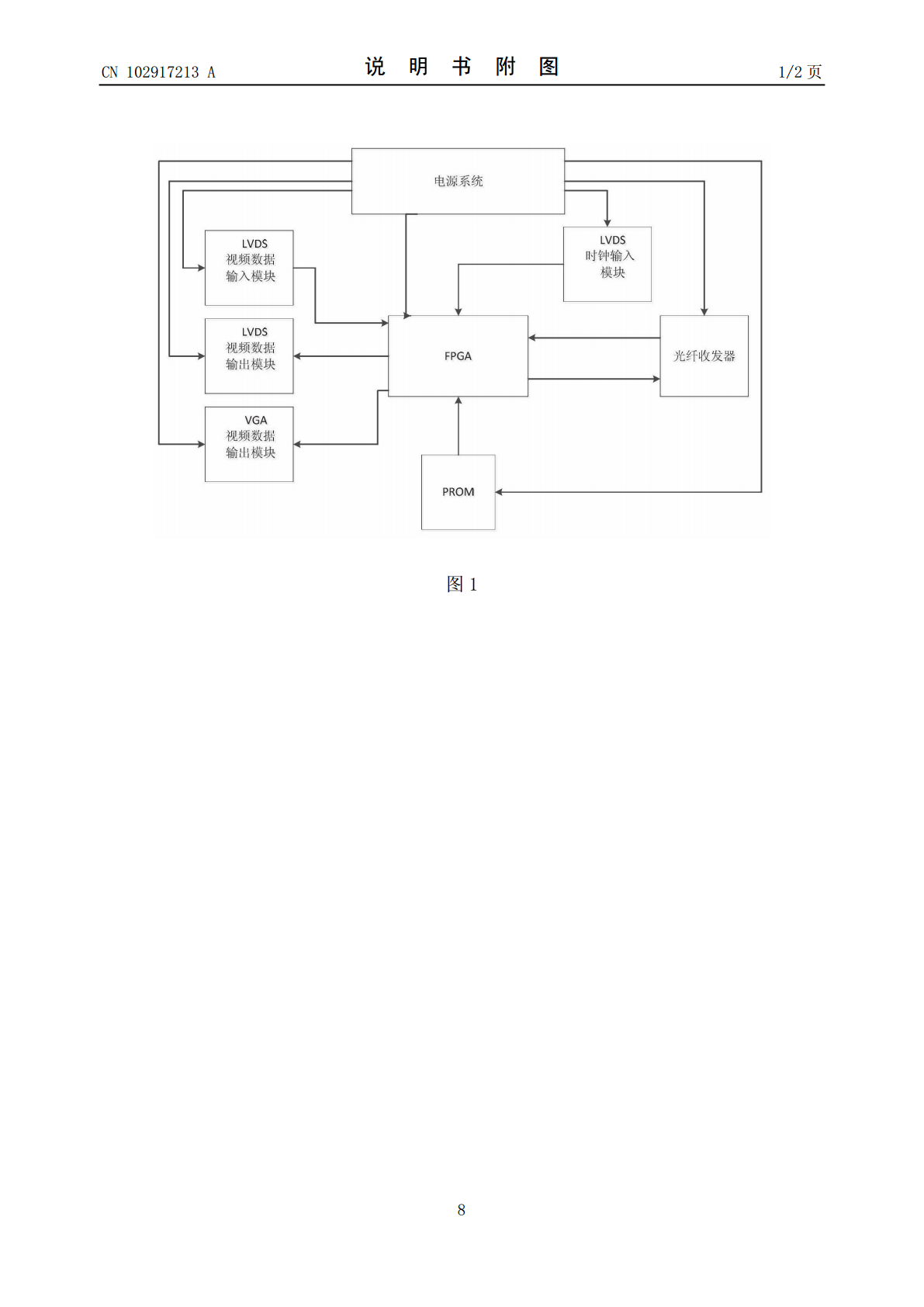

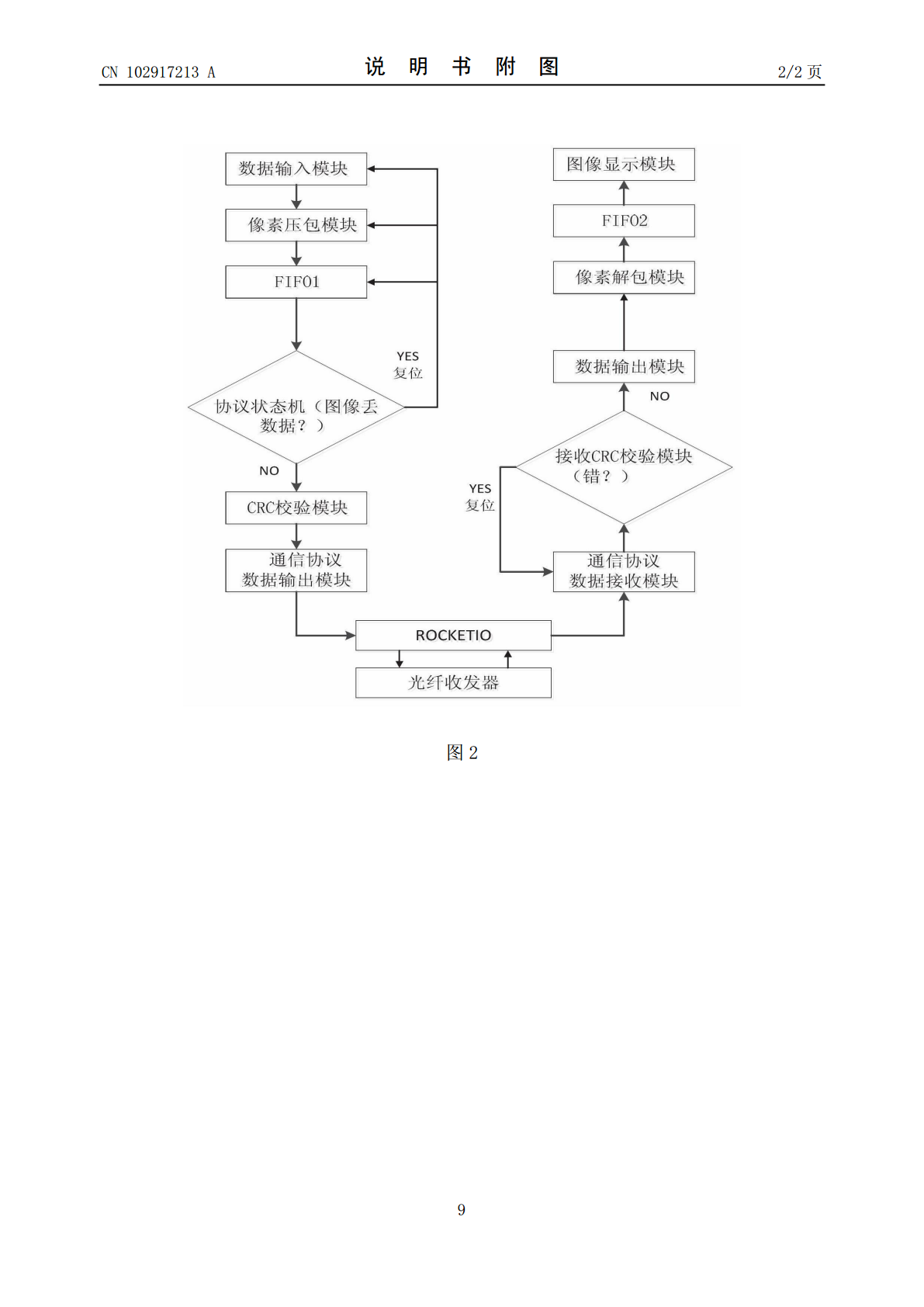

本发明提供了一种光纤视频图像传输系统,包括LVDS视频数据输入模块、LVDS视频数据输出模块、VGA视频数据输出模块、核心处理器FPGA、给FPGA加载程序的PROM、LVDS时钟输入模块、光纤收发器、电源系统,其中VDS视频数据输入模块、LVDS视频数据输出模块、VGA视频数据输出模块、给FPGA加载程序的PROM、LVDS时钟输入模块、光纤收发器均连接到核心处理器FPGA,电源系统给各模块供电。本发明还提供了一种采用该光纤视频图像传输系统进行图像传输的方法。本发明的优点在于:用FPGA实现协议可以多变

一种视频图像传输方法及传输系统.pdf

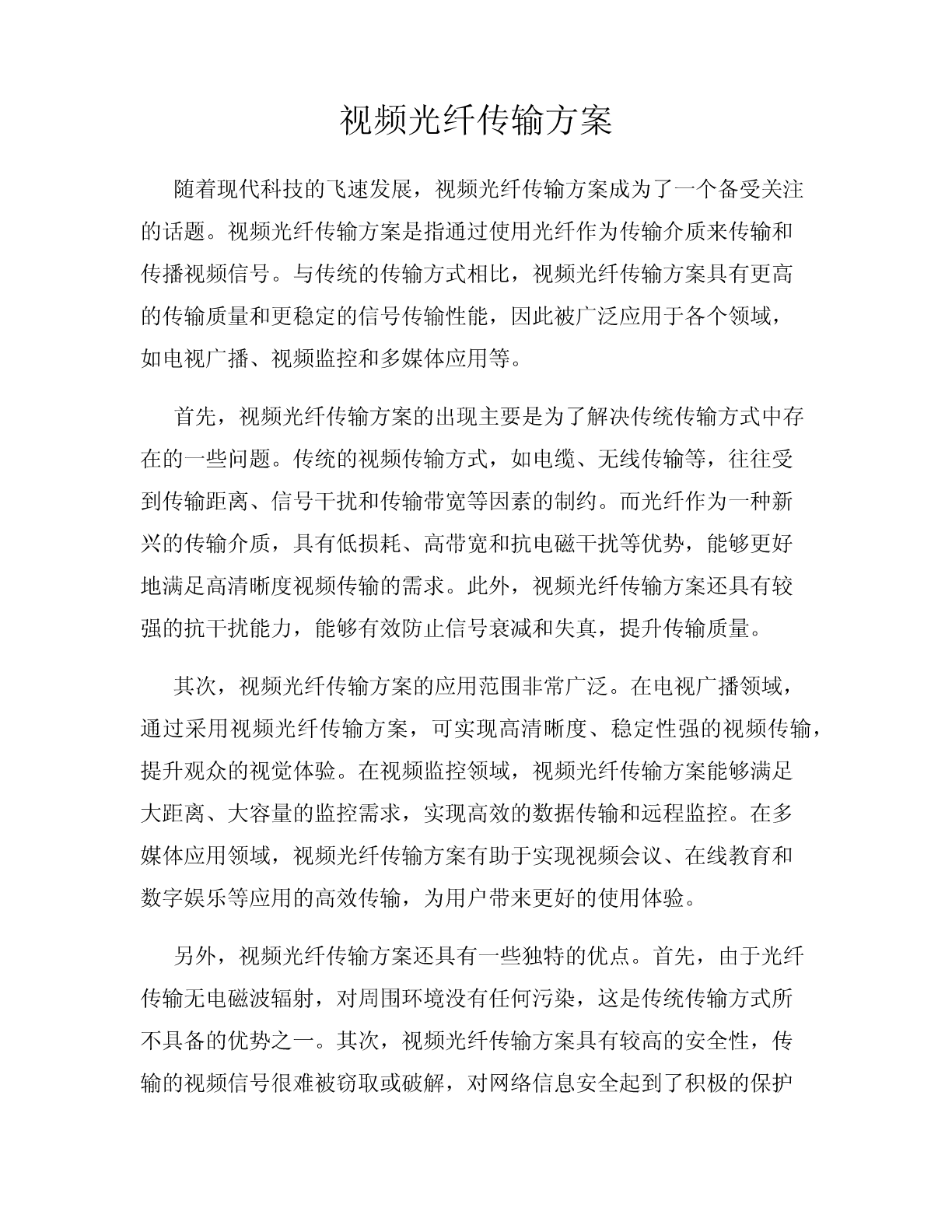

本申请涉及图像处理技术领域,尤其涉及一种视频图像传输方法及传输系统,由于本申请中,第一帧视频序列之后的视频序列的传输仅传输分割后的前景图像,从而使得该视频传输的方法可以在降低高数据量的视频数据的传输量,从而避免传输过程中出现卡顿的现象。

视频光纤传输方案.pdf

视频光纤传输方案随着现代科技的飞速发展,视频光纤传输方案成为了一个备受关注的话题。视频光纤传输方案是指通过使用光纤作为传输介质来传输和传播视频信号。与传统的传输方式相比,视频光纤传输方案具有更高的传输质量和更稳定的信号传输性能,因此被广泛应用于各个领域,如电视广播、视频监控和多媒体应用等。首先,视频光纤传输方案的出现主要是为了解决传统传输方式中存在的一些问题。传统的视频传输方式,如电缆、无线传输等,往往受到传输距离、信号干扰和传输带宽等因素的制约。而光纤作为一种新兴的传输介质,具有低损耗、高带宽和抗电磁干

高清视频光纤传输系统的开题报告.docx

高清视频光纤传输系统的开题报告一、项目概述随着高清视频技术的快速发展,高清视频光纤传输系统被广泛应用于电视直播、会议现场、安防监控等领域。高清视频光纤传输系统具有传输距离远、抗干扰能力强、传输质量高等优点,能够满足视频传输的高要求。本项目将设计开发一款高清视频光纤传输系统,采用光纤作为传输介质,实现高清视频的长距离传输。通过研究和分析现有的光纤传输技术,结合视频压缩编码标准,设计出高性能的视频光纤传输系统。二、项目目标1.研究和掌握光纤传输技术,了解现有的光纤传输方案及其优缺点。2.确定高清视频压缩编码标

分布接入的视频光纤传输系统的中期报告.docx

分布接入的视频光纤传输系统的中期报告本系统旨在实现基于视频光纤传输的分布式视频监控方案。在前期的研究和设计中,我们主要完成了以下几个方面的工作:1.确定了系统的基本架构和技术路线:我们采用了分布式视频采集、光纤传输、中心化管理的系统结构,同时选择了H.264编码和MJPEG编码两种技术路线,并分别进行了试验和对比分析,最终选定了H.264编码方案。2.完成了分布式视频采集节点的设计和制作:根据系统需求,我们选取了高清无损采集卡和摄像头,利用单片机和网口模块实现了视频数据的采集和存储,并设计了对应的硬件和软