一种主从双余度FPGA切换控制电路.pdf

静芙****可爱

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种主从双余度FPGA切换控制电路.pdf

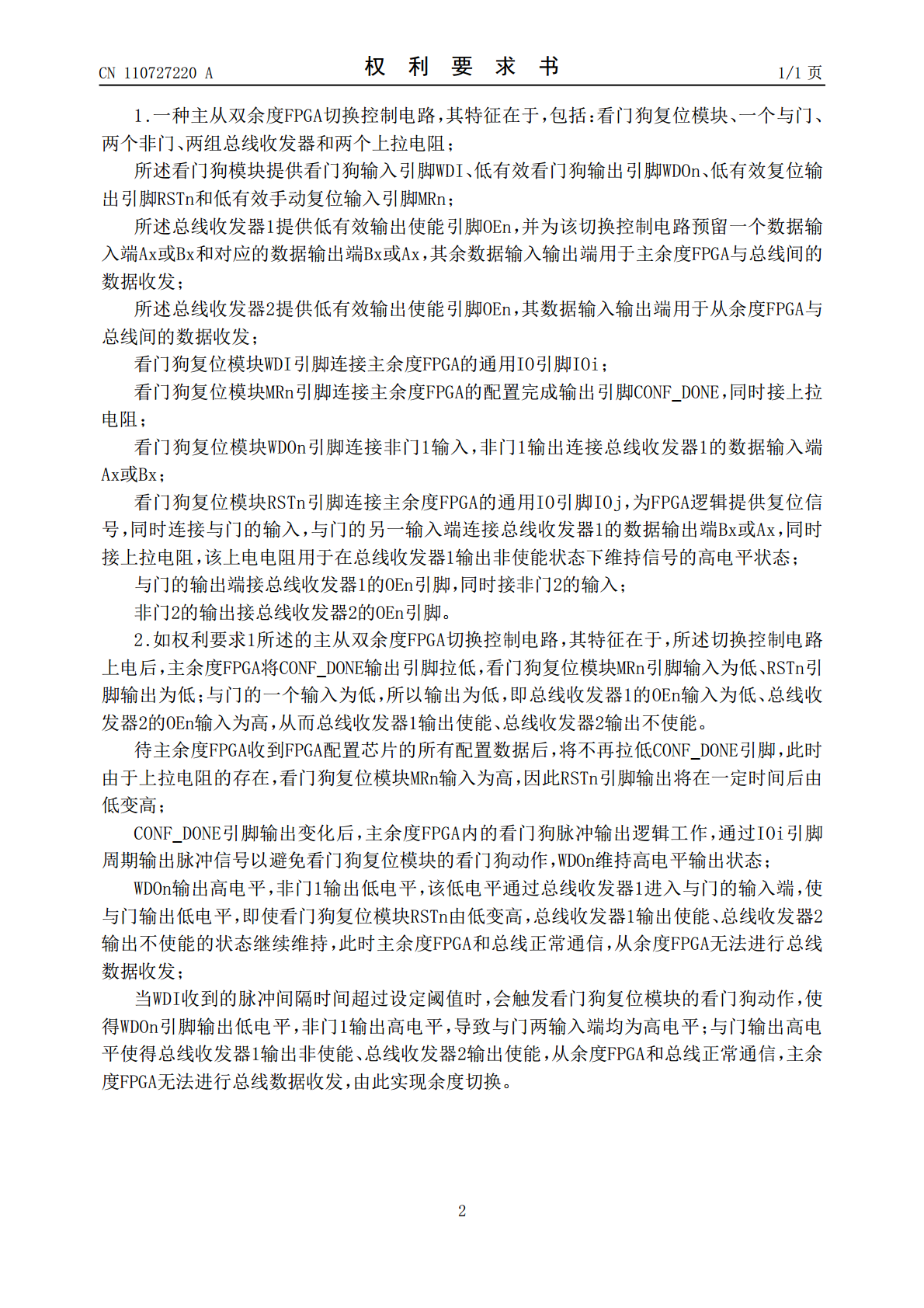

本发明属于数字电路设计领域,涉及一种主从双余度FPGA切换控制电路,由看门狗复位模块、一个与门、两个非门、两组总线收发器和两个上拉电阻构成。本发明电路以看门狗复位模块以核心进行状态监控,并通过与、非门和总线收发器实现FPGA余度切换控制,其电路简单、可靠性强,具有较高的实用价值。

一种1553B总线双余度总线控制器切换方法.pdf

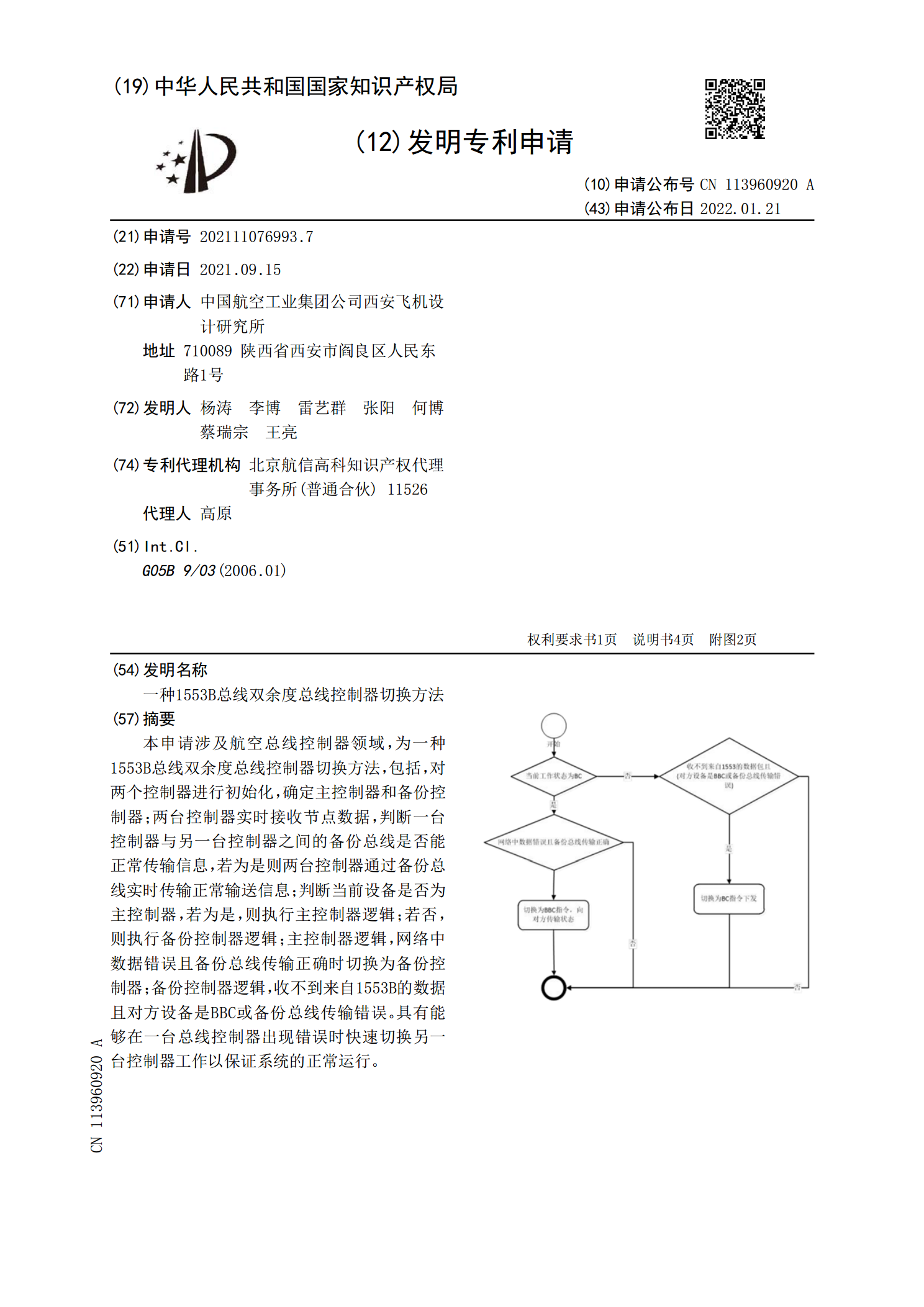

本申请涉及航空总线控制器领域,为一种1553B总线双余度总线控制器切换方法,包括,对两个控制器进行初始化,确定主控制器和备份控制器;两台控制器实时接收节点数据,判断一台控制器与另一台控制器之间的备份总线是否能正常传输信息,若为是则两台控制器通过备份总线实时传输正常输送信息;判断当前设备是否为主控制器,若为是,则执行主控制器逻辑;若否,则执行备份控制器逻辑;主控制器逻辑,网络中数据错误且备份总线传输正确时切换为备份控制器;备份控制器逻辑,收不到来自1553B的数据且对方设备是BBC或备份总线传输错误。具有能

基于FPGA的双余度旋变无刷电机控制系统.docx

基于FPGA的双余度旋变无刷电机控制系统随着信息技术、通信技术、自动化技术和电力电子技术的不断发展,无刷电机被广泛应用于工业、家用电器、汽车和机器人等领域。相比传统的有刷电机,无刷电机拥有高效、低噪音、长寿命等优点,因此逐渐成为电机控制系统的主流。在无刷电机控制系统中,基于FPGA的双余度旋变控制系统是一种重要的控制方式。该种控制方式主要是指利用FPGA芯片对电机的电流和反电动势进行高速采样和计算,并对电机驱动器进行实时的反馈控制,从而实现电机的高速、高效、精确的控制。双余度旋变控制方式采用两组正交的电流

一种USB主从状态切换电路.pdf

本发明涉及USB接口技术领域,公开了一种USB主从状态切换电路,包括USB接口、检测单元、线路切换单元和控制单元,USB接口电连接检测单元,检测单元分别电连接线路切换单元和控制单元,线路切换单元电连接控制单元。USB接口接入主设备时,检测单元向线路切换单元和控制单元输入高电平信号;USB接口接入从设备时,检测单元向线路切换单元和控制单元输入低电平信号。其中,线路切换单元根据检测单元输入的高低电平信号切换物理线路,控制单元根据检测单元输入的高低电平信号切换工作状态,以此实现USB能工作在主和从两种工作模式。

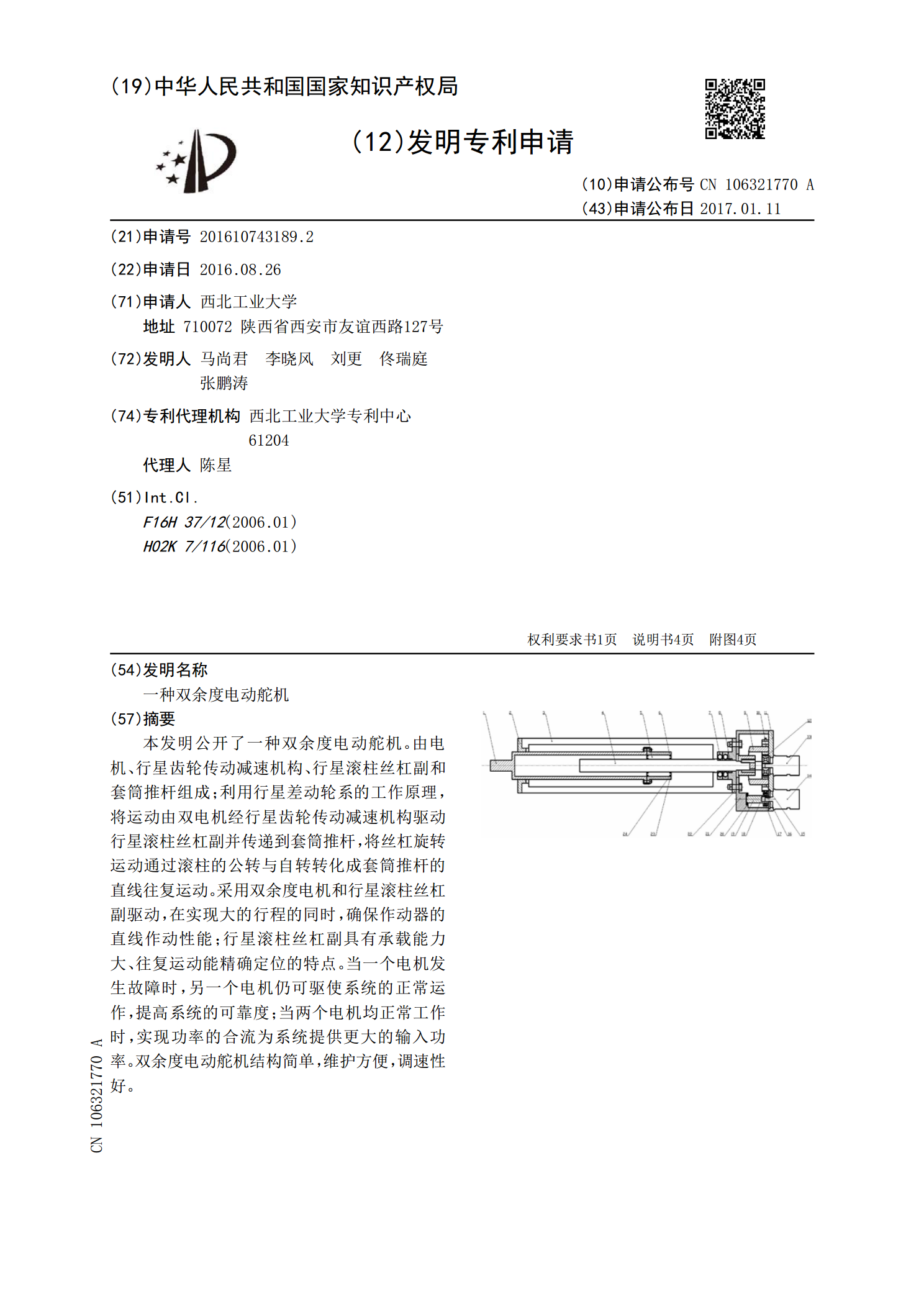

一种双余度电动舵机.pdf

本发明公开了一种双余度电动舵机。由电机、行星齿轮传动减速机构、行星滚柱丝杠副和套筒推杆组成;利用行星差动轮系的工作原理,将运动由双电机经行星齿轮传动减速机构驱动行星滚柱丝杠副并传递到套筒推杆,将丝杠旋转运动通过滚柱的公转与自转转化成套筒推杆的直线往复运动。采用双余度电机和行星滚柱丝杠副驱动,在实现大的行程的同时,确保作动器的直线作动性能;行星滚柱丝杠副具有承载能力大、往复运动能精确定位的特点。当一个电机发生故障时,另一个电机仍可驱使系统的正常运作,提高系统的可靠度;当两个电机均正常工作时,实现功率的合流为