多通道AD数据同步传输系统.pdf

一吃****福乾

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

多通道AD数据同步传输系统.pdf

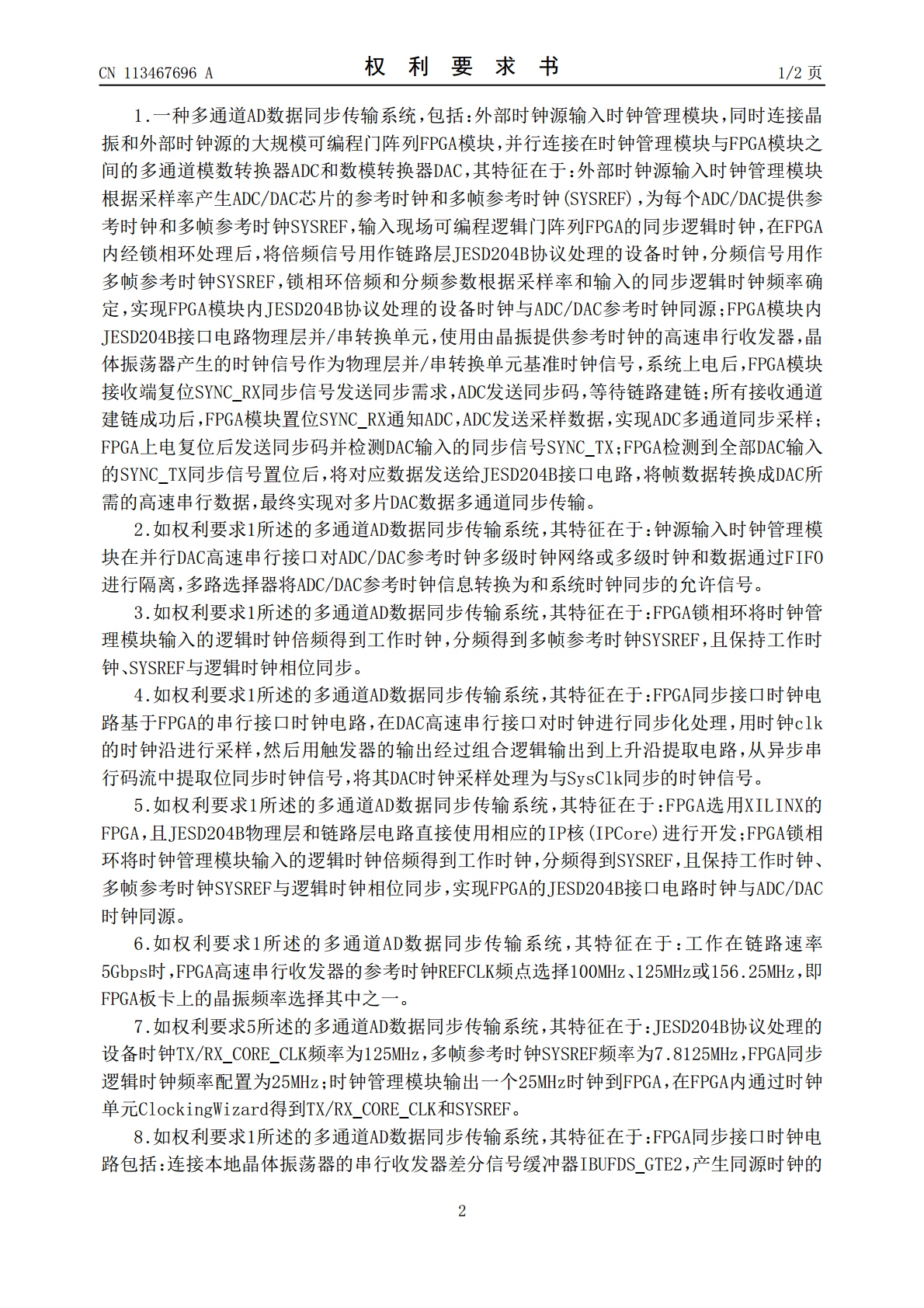

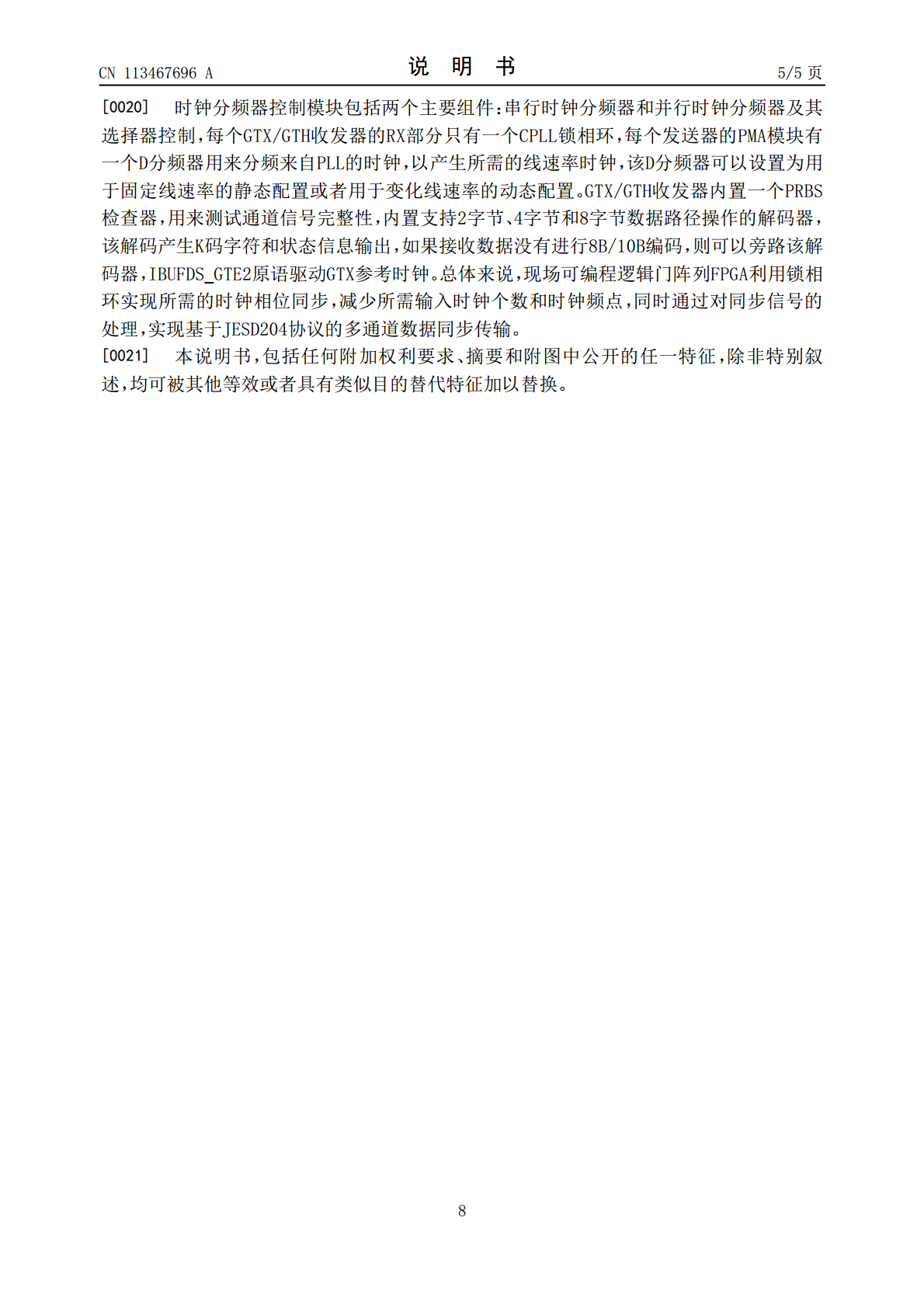

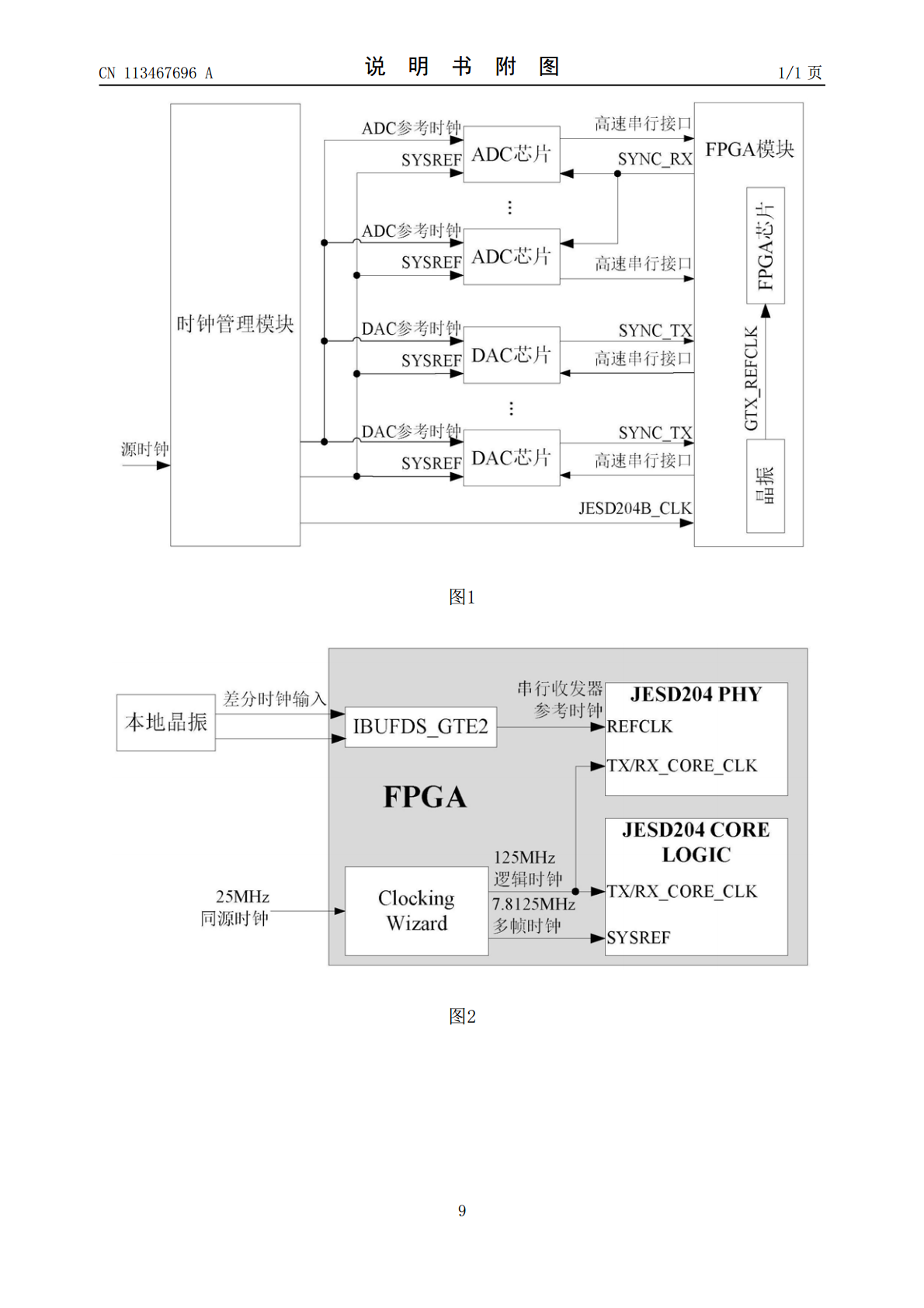

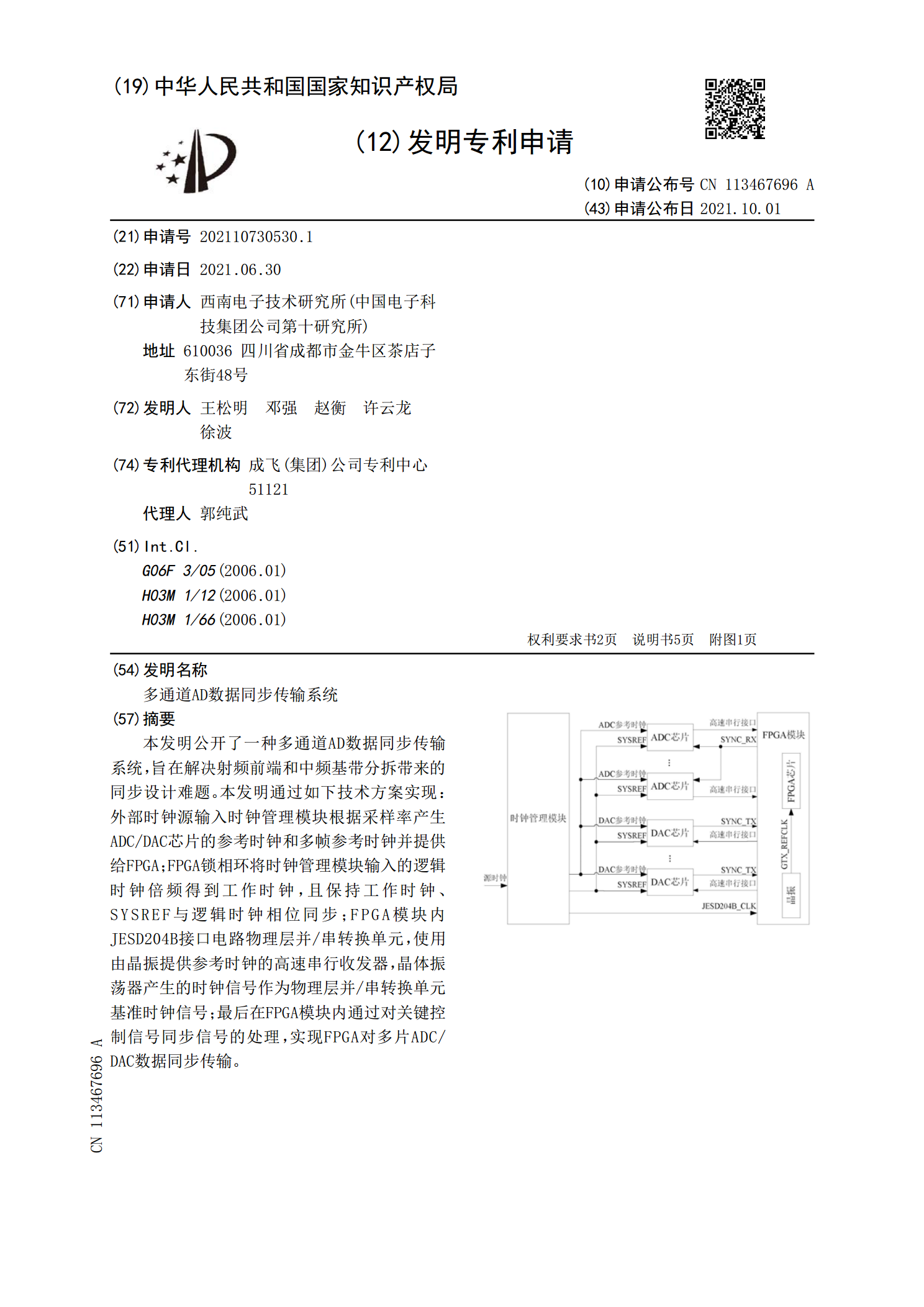

本发明公开了一种多通道AD数据同步传输系统,旨在解决射频前端和中频基带分拆带来的同步设计难题。本发明通过如下技术方案实现:外部时钟源输入时钟管理模块根据采样率产生ADC/DAC芯片的参考时钟和多帧参考时钟并提供给FPGA;FPGA锁相环将时钟管理模块输入的逻辑时钟倍频得到工作时钟,且保持工作时钟、SYSREF与逻辑时钟相位同步;FPGA模块内JESD204B接口电路物理层并/串转换单元,使用由晶振提供参考时钟的高速串行收发器,晶体振荡器产生的时钟信号作为物理层并/串转换单元基准时钟信号;最后在FPGA模块

基于FPGA的多通道高速数据传输系统的设计.docx

基于FPGA的多通道高速数据传输系统的设计杨若愚摘要:通过FPGA实现对8通道LVDS接口电路的控制实现数据收发,利用DDR3SDRAM实现对数据高速缓存,利用FPGA内嵌的PCI-E硬核以PCI-EDMA的方式实现与计算机之间的高速数据传输。测试结果表明,系统可以实现多数据的高速收发,传输速率可达到300MB/s,目前本系统已成功应用于某数据记录仪中。关键词:高速数据传输;FPGA;LVDS;DMA;PCI-E总线;DDR3中图分类号:TP274.2文献标识码:A文章编号:1007-9416(2017)

一种多通道数据动态传输方法.pdf

本发明属于计算机通信技术领域,具体涉及一种多通道数据动态传输方法。它包括以下步骤,S110,获取源数据的属性信息和数据传输接口P1、P2、…、Pn对应的传输速率V1、V2、…、Vn,其中,n为数据传输接口的数量;S111,将源数据分割成n个数据块D1、D2、…、Dn,并获取所有数据块的位置信息,数据块Di的大小与数据传输接口Pi的传输速率Vi成一定比例,i=1、2、…、n;S112,为每个数据块Di添加数据头,数据头包括对应数据块Di的位置信息和大小;S113,将数据块Di的数据头经过数据传输接口Pi传输

多通道数据传输方法及装置.pdf

本发明的实施例提供了一种多通道数据传输方法及装置、计算机可读介质和电子设备。所述多通道数据传输方法包括:通过多通道并行接收多个上行数据包;解析所述多个上行数据包获得多个目标业务数据包和多个上行包头;根据所述多个上行包头对所述多个目标业务数据包进行去重处理;将去重处理后保留的目标业务数据包发送给目标业务服务器;其中,各上行包头包括各上行数据包的包序号。本发明实施例的技术方案能够通过多通道并行传输上行数据包,并通过去重处理,实现目标业务数据包的可靠有效传输。

一种磁共振多通道数字传输系统及其数据传输方法.pdf

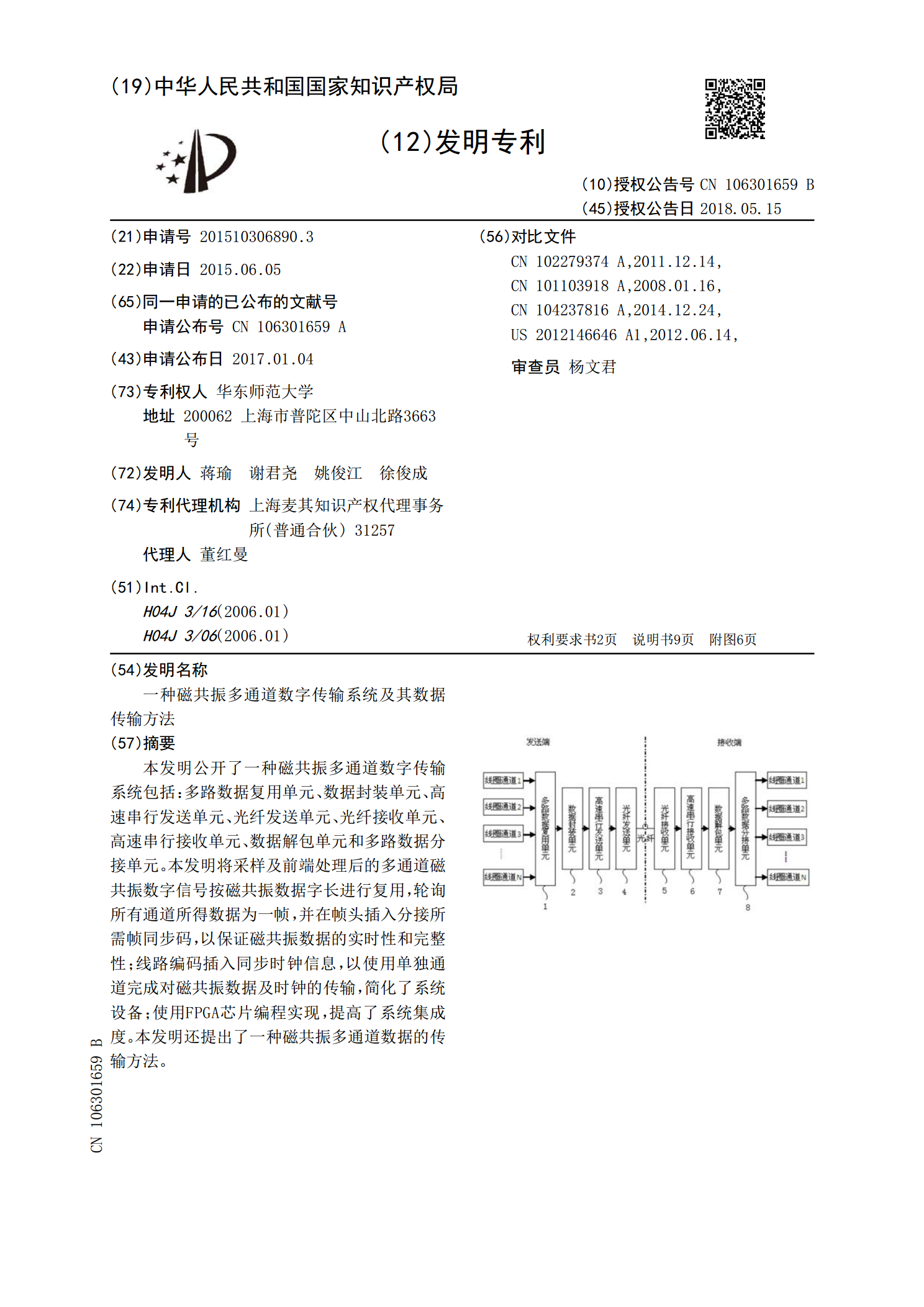

本发明公开了一种磁共振多通道数字传输系统包括:多路数据复用单元、数据封装单元、高速串行发送单元、光纤发送单元、光纤接收单元、高速串行接收单元、数据解包单元和多路数据分接单元。本发明将采样及前端处理后的多通道磁共振数字信号按磁共振数据字长进行复用,轮询所有通道所得数据为一帧,并在帧头插入分接所需帧同步码,以保证磁共振数据的实时性和完整性;线路编码插入同步时钟信息,以使用单独通道完成对磁共振数据及时钟的传输,简化了系统设备;使用FPGA芯片编程实现,提高了系统集成度。本发明还提出了一种磁共振多通道数据的传输方