基于PCIE总线的高速同步串口模块.pdf

慧红****ad

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

基于PCIE总线的高速同步串口模块.pdf

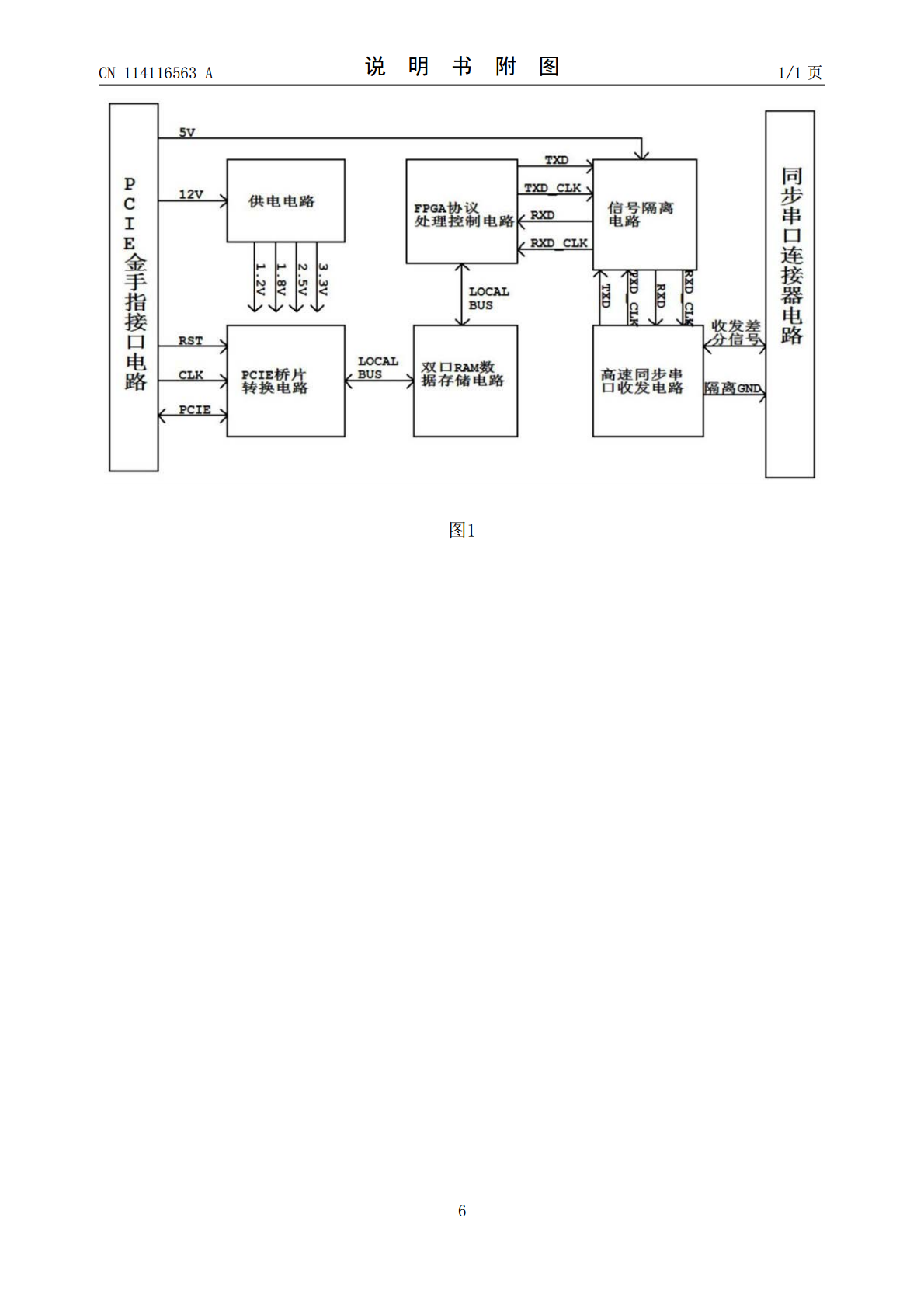

本发明公开了一种基于PCIE总线的高速同步串口模块,其特征在于,包括PCIE金手指接口电路、供电电路、PCIE桥片转换电路、双口RAM数据存储电路、FPGA协议处理控制电路、信号隔离电路、高速同步串口收发电路和同步串口连接器电路。本发明的优点和有益效果是:将通过PCIE金手指引入PCIE高速串行总线,经过协议转换实现高速同步串口总线协议,并通过高速收发器实现与外部设备通信,实现PCIE总线转换高速同步串口,具有集成度高、可操作性强,方便携带、稳定高效等特点。

基于PCIe总线的高速数据采集系统设计与实现.pptx

基于PCIe总线的高速数据采集系统设计与实现目录添加目录项标题系统概述背景介绍系统目标系统架构PCIe总线技术PCIe总线概述PCIe总线特点PCIe总线工作原理高速数据采集模块设计数据采集模块概述数据采集模块硬件设计数据采集模块软件设计数据采集模块性能测试系统实现与验证系统集成与调试系统性能测试实际应用与效果评估结论与展望结论总结未来工作展望感谢观看

基于PCIE总线的高速数据采集系统设计与实现.docx

基于PCIE总线的高速数据采集系统设计与实现基于PCIE总线的高速数据采集系统设计与实现摘要:随着科技的不断发展,高速数据采集系统在许多领域得到了广泛的应用,如物理实验、无线通信、工业监测等。本文围绕基于PCIE总线的高速数据采集系统的设计与实现展开,首先介绍了PCIE总线的特点和优势,然后分析了高速数据采集系统的需求和挑战,接着提出了基于PCIE总线的设计方案,并详细介绍了系统的硬件和软件实现过程。最后,通过实验验证了系统的性能和可行性。关键词:高速数据采集系统;PCIE总线;设计;实现;性能1.引言高

基于PCIe总线的高速数据传输技术研究.docx

基于PCIe总线的高速数据传输技术研究基于PCIe总线的高速数据传输技术研究摘要:随着计算机和通信技术的快速发展,高速数据传输技术在现代社会中的重要性日益凸显。PCIe(PeripheralComponentInterconnectExpress)总线作为电脑主板上的一种高速总线技术,具有卓越的性能和稳定性,被广泛应用于高速数据传输领域。本文通过对PCIe总线的原理和工作机制的研究,探讨了基于PCIe总线的高速数据传输技术的实现原理和优势,同时分析了其在不同领域的应用和发展趋势。关键词:PCIe总线;高速

基于PCIE的高速多串口卡系统及其发送、接收方法.pdf

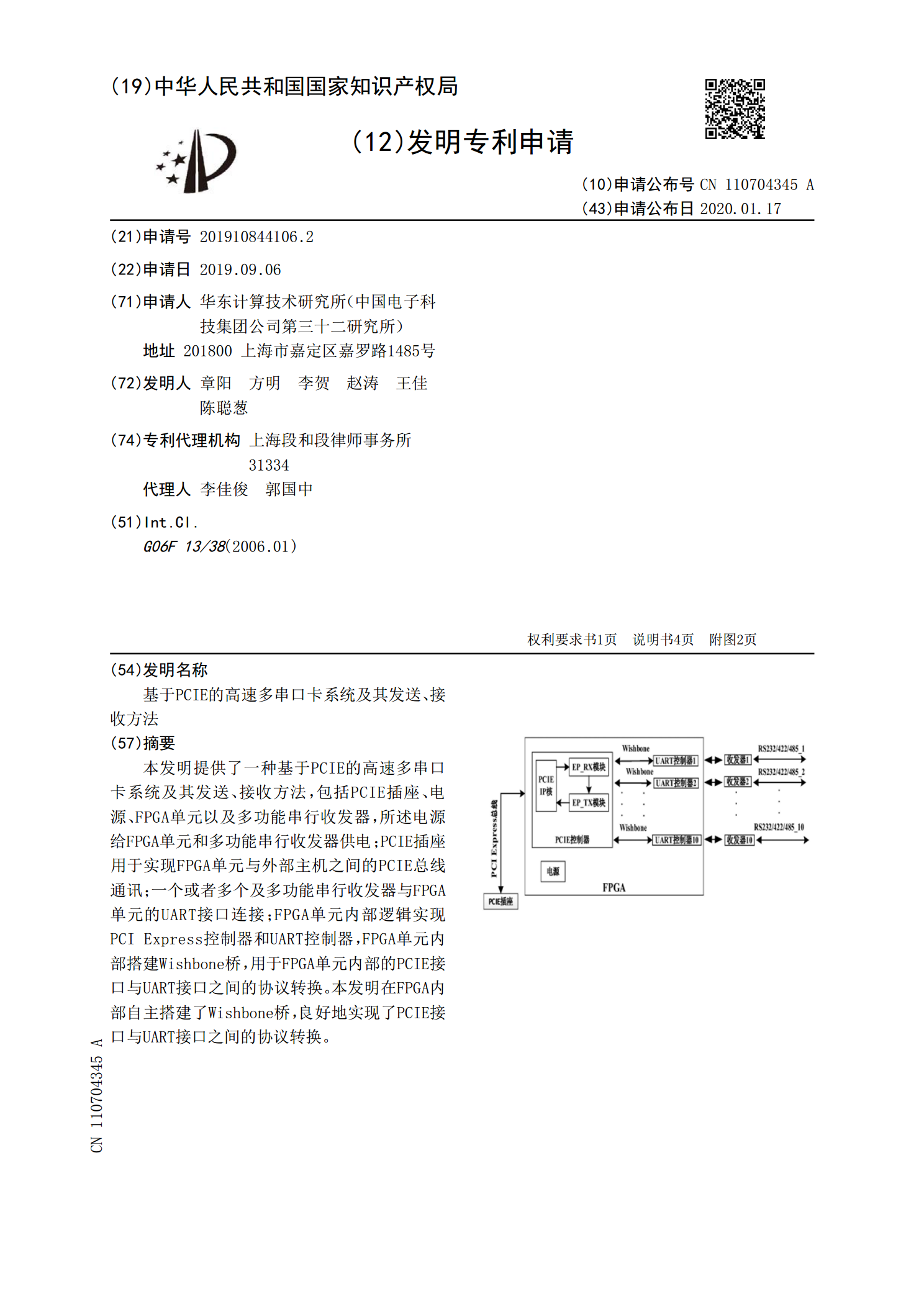

本发明提供了一种基于PCIE的高速多串口卡系统及其发送、接收方法,包括PCIE插座、电源、FPGA单元以及多功能串行收发器,所述电源给FPGA单元和多功能串行收发器供电;PCIE插座用于实现FPGA单元与外部主机之间的PCIE总线通讯;一个或者多个及多功能串行收发器与FPGA单元的UART接口连接;FPGA单元内部逻辑实现PCIExpress控制器和UART控制器,FPGA单元内部搭建Wishbone桥,用于FPGA单元内部的PCIE接口与UART接口之间的协议转换。本发明在FPGA内部自主搭建了Wis